集成电路先进制造技术进展与趋势

张睿,虞小鹏,程然,沈强,耿红艳,高大为,吴汉明

1.浙江大学,微纳电子学院,先进集成电路制造技术研究所,浙江 杭州 311200

2.浙江大学,杭州国际科创中心,浙江 杭州 311200

3.芯创智(北京)微电子有限公司,北京 100871

引 言

集成电路是电子产业和信息社会的支柱和硬件基础。金属-氧化物-半导体场效应晶体管(Metal-Oxide-Semiconductor Field-Effect Transistor, MOSFET)是构成当前集成电路的最基本器件结构,当前的绝大多数集成电路都以互补式金属-氧化物-半导体(Complementary Metal-Oxide-Semiconductor, CMOS)器件作为基础单元。MOSFET 器件进入量产以来,尺寸微缩一直是集成电路性能提升的最重要手段[1-3]。

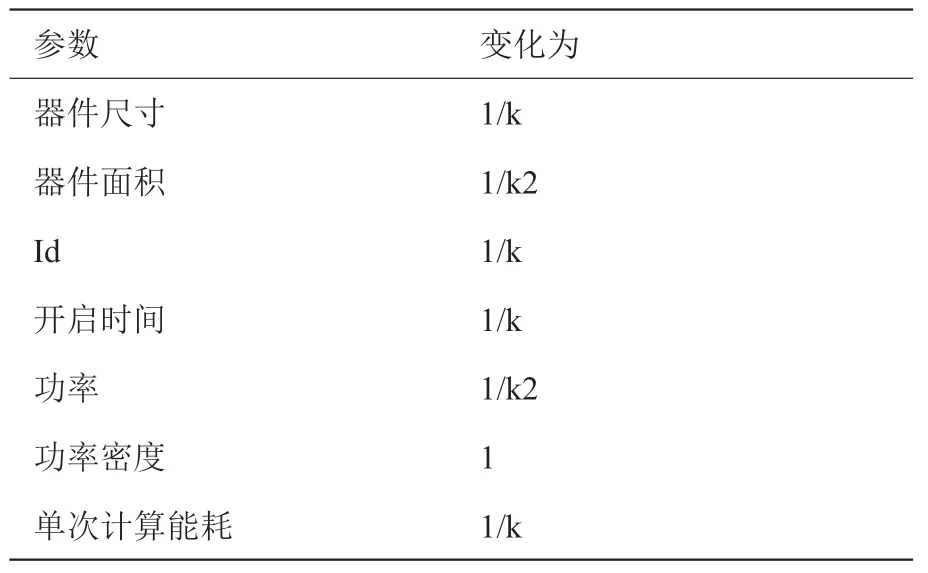

通过表1 可以看出,当MOSFET 器件的尺寸按照等电场微缩(即器件沟道内的电场维持恒定值)的方式缩小至1/k 时,集成电路的面积缩小1/k2、单次运算的功耗降低至1/k2、运算速度提高k 倍。从这一科学原理衍生出的产业规律首先被Gorden Moore发现并被命名为“摩尔定律”,成功预测并指导了集成电路产业出现以来超过半个世纪的发展路径。以典型的集成电路产品中央处理器(CPU)为例,1974年英特尔公司发布4004 处理器采用10 μm 制程,而目前英特尔公司最先进的Ice Lake 系列CPU 采用10 nm 制程(沟道长度Lg=18 nm),每平方毫米面积上集成了超过1 亿个MOSFET 器件[4]。

表1 等电场微缩对MOSFET 器件性能的影响Table 1 The impact of scaling (fixed electrical field) to the electrical performance of MOSFET

随着MOSFET 器件尺寸的急剧缩小,器件结构的典型尺寸不断逼近并超越光刻等微细加工技术的极限,因此人们不断开发新技术推动“摩尔定律”的延伸。尽管近年来在前沿探索方面人们进行了基于新材料(如碳基CPU)、新原理(如量子计算)的集成电路器件和电路原型展示[5-10],但是需要指出的是,以传统Si 基MOSFET 为基础的CMOS 电路仍将占据集成电路产业的主体地位,是集成电路向更高运算速度、更低运行功耗和更丰富功能集成等方向发展的优选方案和主流趋势。

经过半个多世纪的进步,今天的“摩尔定律”内涵已远远超过“MOSFET 器件尺寸微缩”,新技术的引入不断提高先进集成电路制造的技术门槛,并且导致集成电路的性能受到越来越多因素的影响。除了传统微缩过程中获得高性能MOSFET 器件的基本目标,提升电路中器件集成密度、抑制互联寄生效应等多方面需求在集成电路制造中占据越来越重要的地位,并因此催生出一系列提升集成电路性能的新方法,获得越来越多的关注。本文将针对近年来集成电路性能提升过程中的新制造技术进行回顾和展望。

1 MOSFET 器件性能提升

1.1 MOSFET 微缩规则

缩短沟道长度是提升MOSFET 器件性能最有效的方法,从集成电路发明以来尺寸微缩一直是集成电路制造技术发展的主要趋势。但是,单纯地缩短沟道长度将导致MOSFET 器件中短沟道效应增强,因此MOSFET 器件尺寸微缩的过程实质上是抑制短沟道效应的过程。当MOSFET 器件的沟道长度进入亚微米范围后,沟道中的电位受到栅极电压和漏极电压的共同作用,导致器件中出现短沟道效应。沟道中的电位V(y)可以用公式(1)表示[11]:

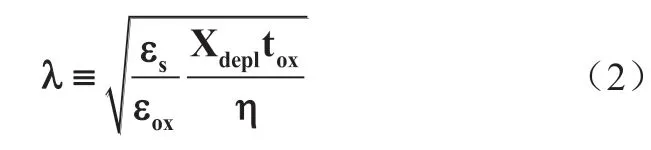

其中,Vbi为源极和沟道间的内建电势,Vds为漏极电压,VsL为源极和沟道间的电位差,y 为沿沟道长度方向的位置,Lg为沟道长度,λ 为自然微缩长度(Natural Scaling Length)。从公式(1)可以看出,当两个MOSFET 器件的沟道长度Lg与自然微缩长度λ的比值相等时,器件中电势沿沟道长度方向的函数曲线相同,即表现出相同的短沟道效应现象。自然微缩长度λ 可表示为公式(2):

其中,εs和εox为半导体和栅绝缘层的相对介电常数,Xdepl为沟道区域耗尽区宽度(当器件的沟道物理厚度TSi小于耗尽区宽度时,Xdepl即为沟道物理厚度),tox为栅氧化层物理厚度,η 为栅极的数量。因此,在不增强短沟道效应的前提下缩短器件的沟道长度,需要在器件中获得尽可能小的自然微缩长度λ。通过增大栅绝缘层的相对介电常数εox,减小栅绝缘层厚度tox,减小沟道物理厚度TSi和增大栅极数量η 等手段能够实现这一目标。这些技术方向催生出了High-k/Metal Gate(增大εox、减小tox)、FinFET(减小TSi、增大η)、全耗尽SOI(减小TSi)和纳米片/纳米线MOSFET(减小TSi、增大η)等方案,以下将分别介绍这几种技术。

1.2 High-k/Metal Gate 技术

传统的MOSFET 器件采用SiO2作为栅绝缘层材料,采用减薄SiO2厚度的方法实现更大的栅极电容密度,获得更大的漏极电流Id并增强栅极对沟道的静电控制能力。但是,随着SiO2栅绝缘层厚度的不断减薄,器件栅极逐渐产生以隧穿电流为主的漏电,导致器件功耗上升[12]。因此,提出了采用高介电常数介质(high-k)替代传统SiO2作为栅绝缘层的方法,在不增大栅极漏电的基础上获得更大的栅极电容密度[13-15](图1)。另一方面,随着器件栅绝缘层厚度的不断减小,栅绝缘层中的电场强度不断增大,导致部分栅极电压以栅极耗尽的形式消耗在多晶硅栅极中,导致器件的栅极电容密度减小。为了解决这一问题,采用金属栅有效地避免了栅极耗尽。

图1 High-k/Metal Gate 栅极堆垛结构示意图Fig.1 The structure of high-k/metal gate gate stacks, compared with conventional poly-Si/SiO2 gate stack

通常采用等效氧化层厚度(Equivalent Oxide Thickness,EOT)评价栅极堆垛的厚度(公式(3)),EOT 值反映了栅极堆垛在器件中提供电容的能力。

其中k 为栅绝缘层的相对介电常数。减小EOT 需要采用具有更大介电常数的栅绝缘层材料,首先替代SiO2的是SiON,通过将SiO2栅绝缘层表面氮化的方式实现。但是SiON 的相对介电常数仅为6 左右,无法满足集成电路技术对MOSFET 器件越来越高的要求。英特尔公司首先在45 nm 节点采用HfO2栅绝缘层(相对介电常数约为20)和TaN 金属栅材料实现了High-k/Metal Gate 技术的量产,栅极堆垛的EOT 值仅为1.2 nm[16]。与65 nm 节点相比,在相同Ioff情况下,pMOSFET 和nMOSFET 分别实现了约50%和13%的Ion提升。高介电常数介质和金属栅的材料不断优化, High-k/Metal Gate 已作为现代集成电路器件的典型结构在45 nm 节点之后的每一代制造技术中采用。但是需要注意的是,采用过大的栅绝缘层介电常数将导致器件漏极与沟道间电容增大,使得沟道电位受到漏极电压影响,器件中的短沟道效应增强。因此,尽管已开发出了相对介电常数超过70 的HfO2基higher-k 介质[17-19],目前广泛采用的仍为HfSiON 栅绝缘层(相对介电常数约为28)。

1.3 FinFET 和SOI 技术

减小沟道的物理厚度(TSi)也是抑制短沟道效应、实现MOSFET 器件进一步微缩化的有效手段。由于Si 沟道的介电常数有限,栅极电压难以对沟道内部实现有效的静电控制,因此沟道内部的漏电导致了MOSFET 器件阈值电压减小、Ioff增大等一系列问题。减小TSi能够从器件中消除无法被栅极电压调控的沟道区域,在更短沟道的器件中也能够实现有效的栅极静电控制。这种通过减小沟道物理厚度实现更短沟道MOSFET 器件的方法被称为薄体(Thin Body)器件技术,典型代表为SOI MOSFET和FinFET 器件。有研究表明当SOI MOSFET 器件的沟道长度为18 nm 时,将沟道厚度由7 nm 减薄至3 nm,可以将Ioff降低3-4 个数量级[20]。IBM 公司利用超薄沟道SOI 器件结构开发了32、22 nm 等数代技术节点(图2),与采用体硅器件结构的技术节点对比,即使SOI 器件的沟道长度比体硅器件缩短,SOI器件中仍然实现了弱得多的短沟道效应。例如,当SOI 器件沟道长度为22 nm 时,器件中的DIBL(Drain Induced Barrier Lowering,漏致势垒降低效应:漏极电压导致沟道与漏极间势垒高度降低,使得器件在较大漏极电压下的阈值电压减小)为85 mV/V,远小于体硅工艺沟道长度30 nm 时的值(120 mV/V)[21-22]。

图2 IBM 公司研发的32 nm 技术节点SOI MOSFET 器件Fig.2 The device structure of a MOSFET in the IBM 22 nm SOI technology node

抑制MOSFET 器件中的短沟道效应,还可以通过增加栅极数量(η)的方法实现。常规的体硅MOSFET 器件具有一个栅极,能够有效地改变沟道表面的电位,但是对沟道内部的静电控制能力不足,增加栅极数量能够更好地调控沟道内部的电位。FinFET 是多栅MOSFET 器件的典型代表,通过鳍状沟道两侧的栅极共同调控沟道电位,抑制器件中的短沟道效应。FinFET 器件在英特尔公司22 nm 节点首先进入量产,实现了比平面器件更低的功耗、更高的性能和集成度[1](图3)。此后,FinFET 技术成为先进逻辑器件的主流方案,在英特尔、台积电、三星等龙头企业的7/5 nm 节点中仍然采用FinFET 器件结构[23-25]。除了在抑制短沟道效应方面展现出巨大优势,FinFET 器件中反型层在沟道两侧栅极的共同调控下形成,因此载流子分布于鳍状沟道内部,有效减弱了载流子的表面粗糙度散射现象,提升了载流子的迁移率,有利于在器件中获得更高的驱动电流Id[26]。

图3 英特尔公司研发的22 nm 技术节点FinFET 器件的沟道区域横截面图Fig.3 The cross session TEM image of an Intel 22 nm technology node MOSFET, taken at the channel region

1.4 纳米片MOSFET 技术

采用FinFET 和SOI 技术能够有效地增强栅极对MOSFET 器件沟道的静电调控作用,但是进一步减小沟道长度仍将导致器件中短沟道效应增强。此外,为获得更高器件性能而将FinFET 器件鳍状沟道高度不断增大的方式将导致工艺难度急剧上升[27]。因此科学家发明了将多个沟道在垂直方向堆叠的方法,在不增大器件面积的情况下获得更大的驱动电流Id[28-30],即纳米片(Nanosheet)MOSFET 技术,如图4 所示。

图4 IBM 公司研发的具有多层堆叠结构的Nanosheet MOSFET 器件Fig.4 The cross session TEM image of nanosheet MOSFETs fabricated by IBM

利用Si 和SiGe 具有不同刻蚀速率的特点,首先在硅衬底上外延若干Si/SiGe 叠层结构,再选择性刻蚀除去SiGe,即得到了多层Si 堆叠的沟道结 构[31]。纳米片器件的优点在于利用叠层结构增加了沟道的数量,同时确保器件的投影面积没有增加。而平面型(Planar)和鳍型(FinFET)器件在增大器件驱动电流时需要采用更大的沟道宽度或多个鳍型沟道并联的方式,使得器件面积增大。因此纳米片MOSFET 器件近年来受到IBM、三星等诸多国际半导体龙头企业的关注。

2 寄生效应抑制

对于先进MOSFET 器件,其电学性能除了与沟道长度、栅极堆垛等关键结构和材料参数有关,也受到器件结构中寄生效应的影响。其中,与器件电学性能最密切相关的是栅极与源漏极间的寄生电容,以及源漏结构与金属配线间的寄生电阻。

2.1 空气侧墙技术

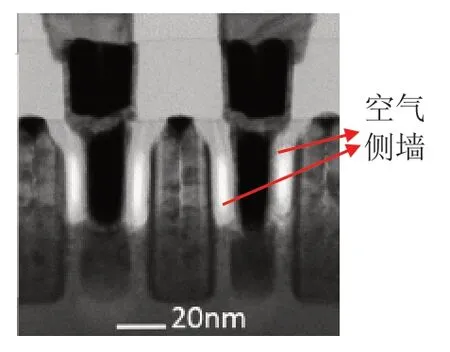

随着MOSFET 器件面积的持续缩小,源漏结构与栅极间的距离不断缩小,导致源漏与栅极间的寄生电容增大。一般采用自对准源漏和栅极结构时采用自对准工艺,工艺过程中需要采用绝缘层侧墙结构将源漏与栅极隔开,避免源漏与栅极连通。传统的侧墙材料为SiO2和Si3N4,相对介电常数分别为3.9 和5~6。为了充分抑制寄生电容,需要采用相对介电常数小于3.9 的侧墙材料。英特尔公司在第一层侧墙薄膜沉积后,利用无定形碳作为第二层侧墙薄膜提供最外侧第三层侧墙薄膜沉积的支撑,形成类“三明治”结构。最后选择性除去无定形碳,在第一、三层侧墙薄膜中间形成空气桥结构,称为空气侧墙(图5)[4]。由于空气桥的相对介电常数与真空相似,远小于SiO2和Si3N4的相对介电常数,因此采用空气侧墙技术能够有效降低源漏与栅极间的寄生电容,有益于提高MOSFET 器件的电学特性(尤其是充放电速度)。

图5 英特尔公司在10 nm 技术节点中引入的空气侧墙结构Fig.5 The structure of air-spacer developed by Intel in the 10 nm technology node

2.2 Co 局部接触金属

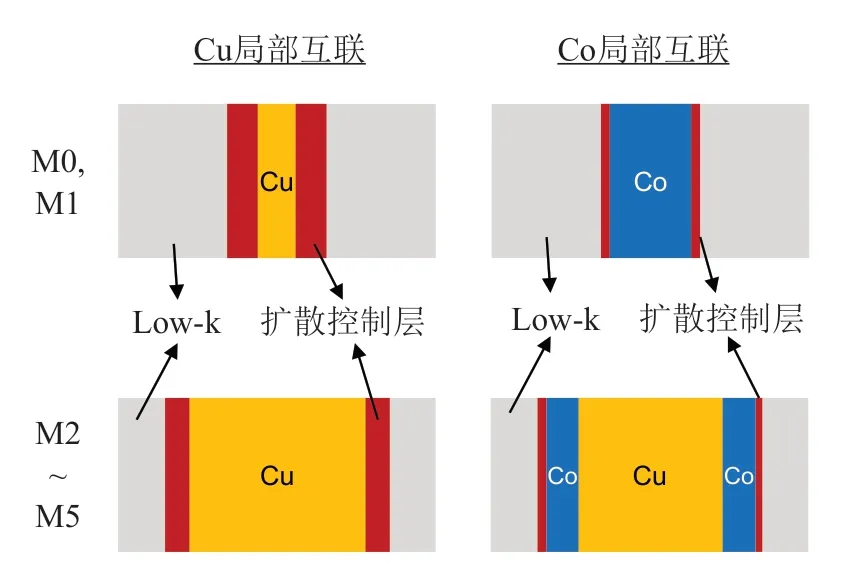

MOSFET 器件的总电阻由沟道电阻和寄生电阻共同构成,在先进制造节点中沟道长度缩短使得器件的沟道电阻急剧下降,因此器件总电阻中的很大比例由寄生电阻贡献。在先进技术节点中,器件寄生电阻必须不断减小,尤其是对于FinFET 等三维沟道器件,寄生电阻减小的趋势甚至逐步加快。金属互联是寄生电阻的重要来源,传统的集成电路制造工艺中采用铜作为互联金属材料。但是铜具有很强的电迁移特性,随器件工作时间加长出现晶须生长等现象,导致金属互联的电阻增大、可靠性下降。为避免这一现象,通常在互联通孔和互联沟道表面沉积一层扩散控制层(如TaN 等)阻止铜互联发生电迁移。但是扩散控制层材料将占据一定的互联线横截面积,不利于抑制寄生电阻。

英特尔公司在10 nm 技术节点中引入Co 局部接触金属技术(图6)[4]。以Co 作为M0 和M1 层材料。由于Co 具有比Cu 弱得多的电迁移特性,采用Co 作为金属互联材料能够显著提升集成电路的电学特性。与同等尺寸的Cu 接触金属相比,采用Co 接触金属后,集成电路的电迁移降低至1/5~1/10。同时,由于无需在互联通孔和互联沟道表面沉积较厚的扩散控制层,通孔的电阻率降低了50%。因此在较上层的M2 至M5 层金属互联,也采用了先沉积Co 薄膜再填充Cu 的方式提升互联结构的抗电迁移特性。

图6 英特尔公司Co 局部接触金属与传统的Cu 金属互联技术对比Fig.6 The comparison of Intel’s Co local contact technique and the conventional Cu interconnection technique

3 器件集成度提升技术

3.1 先进光刻技术

随着人们对集成电路功能和性能的更高需求,电路中器件的规模持续增大。以CPU 为例,近年来电路中的器件数量已达几十亿量级,并且有进一步增加的趋势。但是在这个过程中,芯片的面积维持在大约100 mm2,并没有显著增大,因此器件集成度的提升是集成电路先进制造技术最典型的特征和衡量指标之一。以英特尔公司10 nm 技术节点举例,FinFET 的鳍形沟道的厚度和密度在很大程度上决定了器件对漏电电流的控制能力和器件的集成度。与14 nm 技术节点对比,10 nm 技术节点的鳍型沟道厚度减薄了约20%,间距缩小了约25%,因此器件的电学性能得以显著提升。

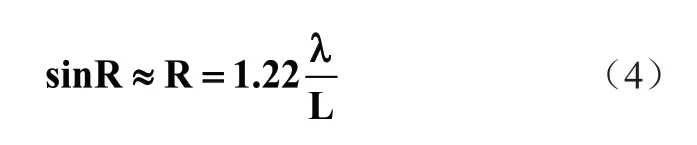

通过增加曝光次数等方法可以获得更精细、密度更大的图形,如英特尔公司10 nm 技术节点采用了四重曝光,但是曝光次数的增加将导致成本上升等一系列缺点,因此仍然需要持续突破光刻的极限尺寸。光刻的极限尺寸由光刻分辨率极限决定。光刻分辨率极限可以通过瑞利判据判断(公式(4))。

其中,R 为分辨角,L 为透镜的数值孔径,λ 为光源的波长。减小光源波长或增大透镜的数值孔径可以获得更高的光刻分辨率。由于设备自身尺寸的限制,透镜的数值孔径无法持续增大,因此随着集成电路制造工艺从微米节点进入10 nm 节点,光刻工艺中使用的波长从365 nm 逐渐转变为193 nm。尤其是在近年来,出现了采用极紫外光作为光刻光源的EUV光刻技术。EUV 光刻采用波长仅为13.5 nm 的极紫外光源,具有更高的光刻分辨率,为器件集成度的进一步提升奠定了基础。图7 为EUV 光刻经过单次曝光和193 nm 浸没式光刻经过三次曝光后的图形对比,可以确认采用EUV 光刻能够在维持图形密度的情况下获得更高的图形精度。

图7 193i 浸没式光刻三次曝光与EUV 光刻单次曝光获得的结果对比Fig.7 The comparison of the patterns fabricated by triple exposure using 193i lithography and single exposure using EUV lithography

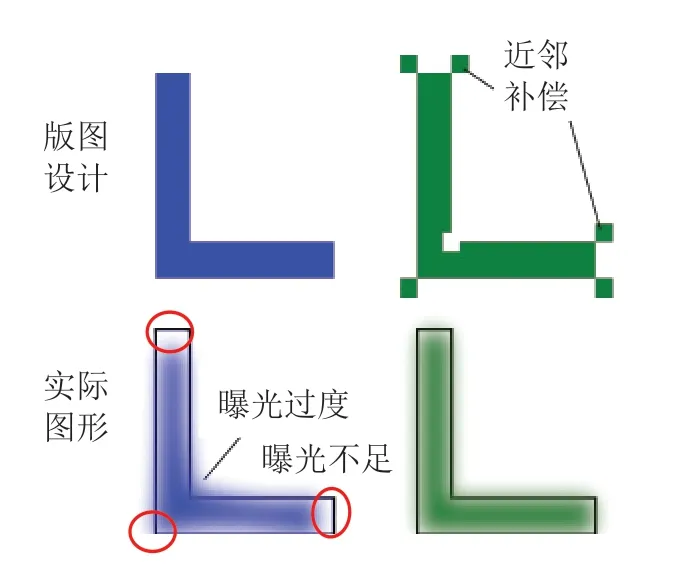

另一方面,由于目前光刻图案的尺寸已进入纳米量级,光衍射效应的增强导致光刻图案失真,无法与掩模板上的图案对应,版图设计过程中必须充分预留冗余以确保电路功能的正常实现。因此在制造掩模板和光源时,利用衍射效应对光刻图案进行光学近邻补偿(Optical Proximity Correction, OPC)。图8 为是否采用光学近邻补偿的光刻图案示意图,可以看出光学近邻补偿技术能够有效减弱衍射效应导致的光刻图案失真,确保光刻精度。

图8 有无光学近邻补偿时的光刻掩模板设计与光刻效果对比Fig.8 The comparison of the mask design and the lithography results w/ and w/o including the OPC

3.2 器件结构紧凑化

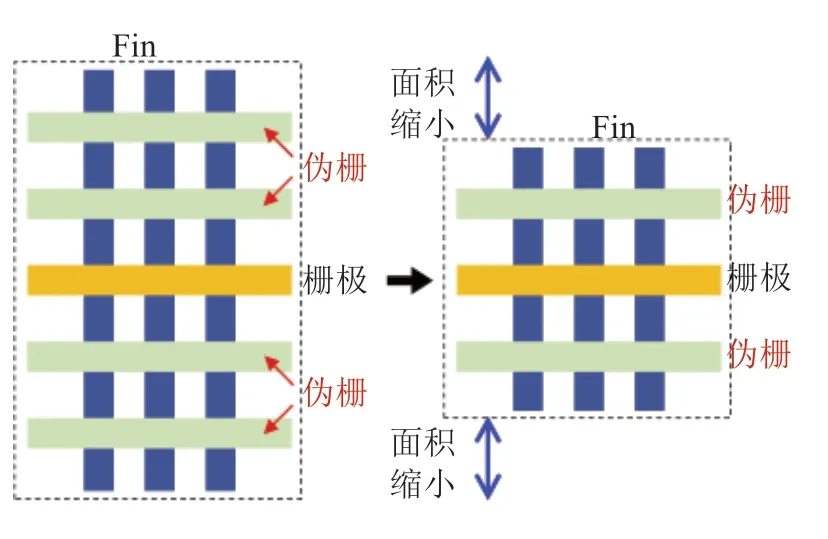

在以英特尔公司10 nm 技术节点为代表的先进制造技术中,还开发了活跃栅上触点(Contact On Active Gate,COAG)和单伪栅等技术。

传统上MOSFET 器件的栅极触点位于沟道的一侧,在器件以外占用了额外的面积。在COAG 技术中,栅极触点被直接制造在活跃栅极的正上方,无需在器件一侧占据额外的面积,使得MOSFET 器件的面积缩小约10%,实现了器件集成度的提升(图9)。此外,在22/14 nm 技术节点中,需要在活跃栅极两侧分别配置多个伪栅,用于隔开活跃栅极并在多个FinFET 并联时更为精确地匹配电流。通过更为精确的工艺控制,近年来逐步减少了该过程所需的伪栅数量。目前在FinFET 器件活跃栅的两侧可以仅使用各1 个伪栅实现隔开活跃栅极和匹配电流的功能,进一步减小了器件面积,提高了集成度(图10)。

图9 英特尔公司活跃栅上触点(COAG)技术示意图Fig.9 The schematic image of the COAG technique developed by Intel

图10 英特尔公司单伪栅技术示意图Fig.10 The schematic image of the single-dummy gate technique developed by Intel

3.3 CMOS 布局技术

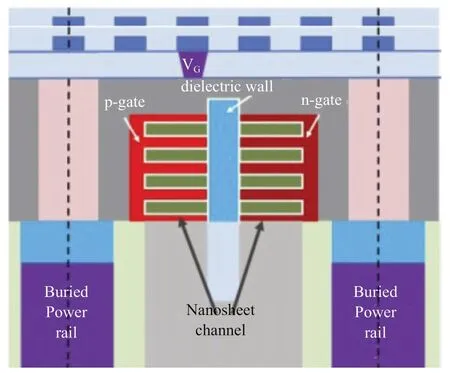

传统的集成电路制造过程中,pMOSFET 和nMOSFET 分别位于不同的有源区内,通过金属配线连接形成CMOS。由于光刻分辨率和工艺流程的限制,pMOSFET 和nMOSFET 间需保持一定距离,限制了集成度的提高。针对这一问题,IMEC 的研发人员提出了叉形晶体管(Forksheet MOSFET)结构(图11)。与传统的CMOS 布局采用有源区进行器件隔离的结构对比,叉形晶体管采用“介电墙”隔离pMOSFET 和nMOSFET,并使用叉形栅极结构控制器件的沟道,这种布局方式允许更紧密的器件间距、提升器件集成度,或将节约的空间用于增加沟道宽度提高启动电流Id。由于叉形栅极与源/漏极具有更小的交叠区,使得寄生电容减小,也有利于器件性能的提升。与传统的有源区隔离器件对比,Forksheet MOSFET 能够将器件运算速度提升10%(恒定功率)、或降低功耗24%(恒定运算速度)。在集成度方面,由于节约了栅极扩展、栅极切割及伪栅褶皱等结构占用的空间,采用8 nm 的pMOSFET/nMOSFET 间距可使SRAM 单元面积减小30%[32]。

图11 IMEC 研发的Forksheet MOSFET 结构示意图Fig.11 The schematic image of the Forksheet MOSFET developed by IMEC

构成电路结构时,金属配线的数量和宽度不能持续减小,因此当器件密度持续增大至一定程度,集成电路中器件集成度的进一步提升将逐渐受到布线空间的限制。为了突破这一瓶颈,IMEC、英特尔等公司研发了互补场效应晶体管(Complementary FET, CFET)结构。CFET 结构突破了传统上将所有器件排列在同一平面上的方式,将pMOSFET 制备在nMOSFET 上方,并在两层器件间引入额外的局部互联层。这种将器件垂直堆叠、并将一部分金属配线制备在单元内部的布局方式开发利用了垂直晶圆维度的空间,极大提升了器件的微缩潜力,为单元面积的减小提供了更大可能性。将部分金属配线制备在单元内部,也简化了各单元间的金属配线设计,有望在相同金属互联层数下实现更复杂的电路设计。目前,IMEC 已在12 吋晶圆上展示了采用纳米片晶体管器件的CFET 结构,并提出CMOS 布局结构将在2 nm 节点进入Forksheet MOSFET 阶段、在1 nm 节点进入CFET 阶段。英特尔公司在实现了CFET 结构的同时,还创新型地引入了高迁移率沟道材料[33]。通过将Ge 沟道Nanosheet pMOSFET堆叠在Si nFinFET 上方,实现了异质集成的CFET结构,充分利用了Ge 中空穴迁移率高的特点提升pMOSFET 性能,展示了CFET 结构与新材料、新结构器件技术整合的可行性。

图12 英特尔研发的CFET 结构示意图Fig.12 The schematic image of the CFET structure developed by Intel

4 结论与展望

本文回顾了近年来集成电路先进制造技术发展过程中的新方法与新技术进展。当前集成电路先进制造技术主要从MOSFET 器件电学性能提升、寄生效应等非理想因素抑制和器件集成度提升等几方面入手突破瓶颈,采用了一系列新材料、新工艺和新器件结构。需要指出的是,集成电路先进制造技术已经成为当前最精密、规模最大的系统工程,单步制造工艺或单项技术的创新已很难维持集成电路制造水平的高速持续提升。必须从材料基础、参数调节、工艺整合和良率提升等诸多方面协同优化,才能够实现满足产业需求的集成电路制造成套工艺技术。不断应对摩尔定律延伸过程中的挑战、甚至尝试突破摩尔定律将是集成电路先进制造技术在未来的主旋律。

利益冲突说明

所有作者声明不存在利益冲突关系。