碳基集成电路技术研究进展与展望

许海涛,彭练矛

1.北京华碳元芯电子科技有限责任公司,北京 100195

2.北京大学,北京 100871

引 言

自20 世纪60年代开始,摩尔定律的提出推动着硅基集成电路技术的快速发展,带来了现代信息技术革命,深刻影响着人们生活的方方面面。随着芯片技术和制造工艺的进步,晶体管的尺寸不断缩减,芯片的集成度和性能不断提升。1974年,Intel的第一代4004 处理器,采用10 微米工艺,晶体管数量约2 250 个,每秒运算约6 万次;而2020年,苹果发布的A14 芯片,采用5 纳米工艺制程,集成了约118 亿个晶体管,运算速度达到每秒11 万亿次。芯片算力的巨大提升使得机器学习、人工智能等研究从理论算法逐步走向现实应用,也带来了自动驾驶、AR/VR 等新领域的兴起和发展。与此同时,人们对芯片的信息处理能力、功耗和功能集成等也提出了更高的要求,而硅基CMOS 技术已逼近其物理极限,芯片的制造工艺也越来越复杂,工艺成本和设计成本越来越高,芯片的算力和能效受限于功耗墙和存储墙等问题难以有效提升,硅基芯片技术已经难以支撑摩尔定律的继续前进。

首先是功耗墙问题。芯片功耗由动态功耗和静态功耗组成,其中静态功耗Pleak正比于工作电压(Vdd)、漏电流(Ileak):

动态功耗Pa正比于工作频率(f)、工作电压的二次方(Vdd2)、电容(C)和活动因子(α):

在很长一段时间内,硅基芯片技术按照Dennard缩放定律的指引向前发展,即器件的尺寸(W,L)缩减时,其工作电压(Vdd)和阈值电压(Vt)等也等比例缩减,沟道中的电场保持恒定,动态功耗密度(Vdd*Ion/(W*L))保持不变。但是当硅基工艺进入90 纳米工艺节点时(物理栅长约40-50 纳米),随着晶体管数量的指数级增加,芯片的静态功耗急剧升高,已经接近动态功耗,如图1(b)所示。此时,继续提高芯片的工作频率,将使总功率密度进一步增加,芯片发热量继续增大,当超过芯片的散热能力时,芯片温度将不断上升,导致性能下降甚至烧毁。减小功率密度最有效的方式是降低工作电压。不过由于传统硅基晶体管的开关由热电子发射机制主导,电子的玻尔兹曼分布使器件的开关速度(亚阈值摆幅)在室温下无法小于60 mV/dec。为了同时满足较小的关态电流和较大的开态电流,工作电压无法按比例有效缩减。因此只能牺牲工作频率的提升,来维持芯片的功率密度在散热容限以内,如图1(c)所示。

图1 硅基芯片的功耗墙问题[1-2]Fig.1 The Power Wall for silicon chips

其次是存储墙问题。数据在计算单元、缓存、内存之间转移,占用了约90%的功耗和时间,如图2(a)和2(b)所示,造成高功耗、低效率问题,导致芯片算力无法进一步提升。目前硅基芯片解决存储墙问题主要通过多片三维集成的技术,即基于硅通孔(TSV)工艺,如图2(c),通过2.5D 或3D 异构封装来集成运算单元和存储单元,增加数据带宽;但是随着TSV 尺寸不断减小,工艺难度和成本将越来越高,良率和可靠性控制更加困难。更高效的方案是采用单片三维集成技术,逻辑层和存储层采用层间通孔(ILV)进行互连,如图2(d),通孔尺寸大大减小,采用近存计算的方案,在三维层面进行芯片架构设计和优化,更灵活地进行逻辑单元和存储单元的布局,实现更大的数据带宽、更高的算力和更低的功耗,真正解决存储墙问题,发挥出近存计算的巨大优势。但是目前,由于硅基高温退火工艺的限制,硅基计算单元和存储单元(SRAM)无法实现单片三维集成。

图2 硅基芯片的存储墙问题[3-4]Fig.2 The Memory Wall for silicon chips Single-thread

最后是尺寸缩减问题。当沟道尺寸不断减小时,源漏之间的偏压将影响沟道中的电势分布,造成栅极对沟道静电学控制的下降,源极区的势垒高度降低,即DIBL 效应,导致器件阈值电压变化和亚阈值摆幅的恶化。为了抑制短沟道效应,一个有效的方式是减薄沟道,提升栅控。硅基器件在此指引下,从平面结构到FinFET,再到环栅,但是当硅材料减薄到纳米尺度时,微加工工艺的不完美引起的表面损伤或粗糙将对载流子输运产生不利影响,降低载流子迁移率,影响器件的开态电流和器件一致性。此外,由于硅基材料通过离子注入掺杂实现电学调控,当器件尺度达到纳米量级时,杂质原子数目的涨落和分布位置的差异,将引起器件电学性能的较大变化,严重影响器件的一致性,使超大规模集成电路的设计和制备更为困难。

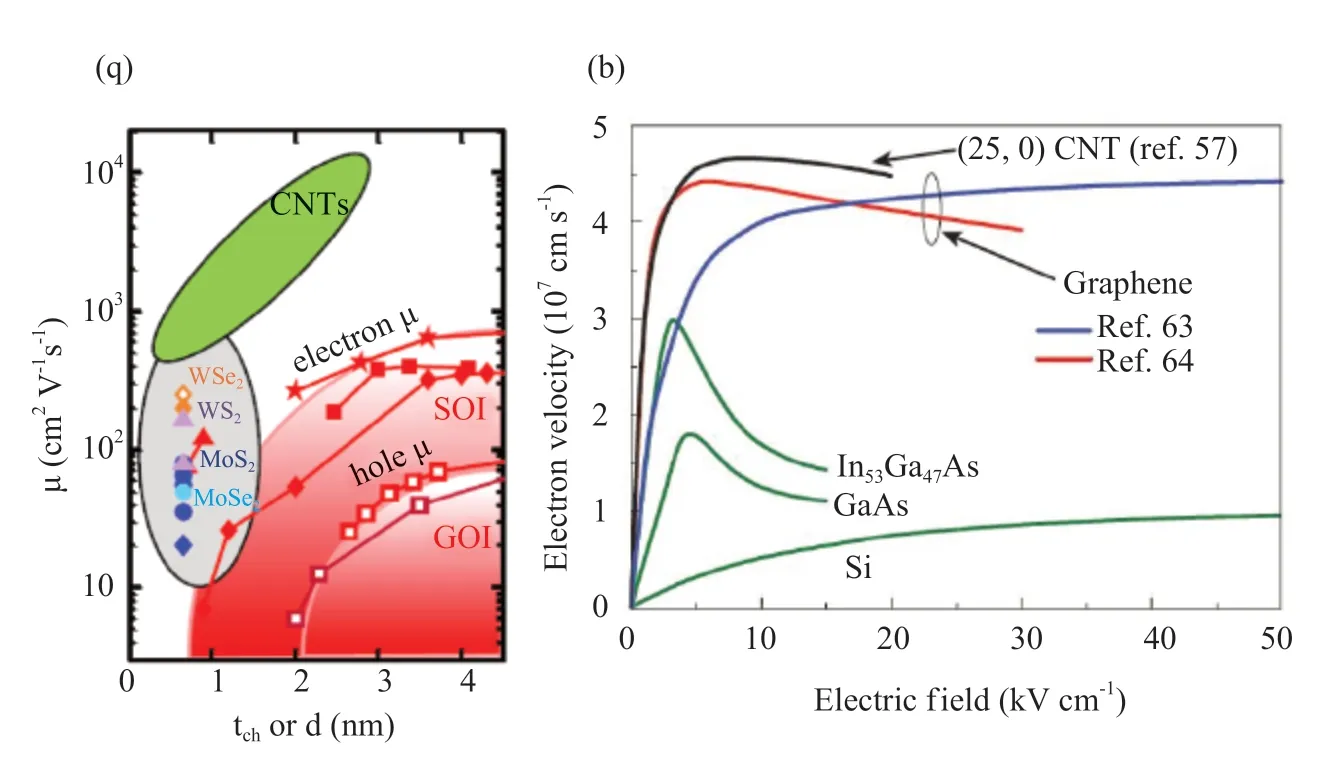

解决硅基芯片所面临的功耗墙、存储墙和尺寸缩减等问题,需要新的沟道材料和新的芯片架构,突破硅基材料和工艺的限制。新的沟道材料需要满足:(1)超薄,从而实现优异的栅控特性和满足尺寸缩减的需求;(2)具有高的迁移率和费米速度,从而可以满足高速低功耗的工作条件,实现弹道输运;(3)完美晶格,无表面悬挂键,可以形成高质量的栅界面;(4)稳定的物理化学性质,具有良好的工艺兼容性和工艺灵活性。在以上几点的指引下,我们审视目前主要的低维纳米材料,包括石墨烯、碳纳米管、二维半导体材料等,发现碳纳米管是满足所有要求的、最具潜力的晶体管沟道材料[5-6],具有极高的载流子迁移率、超薄沟道和高饱和速度,如图3 所示,有望实现低电压高驱动电流,有效解决功耗墙和存储墙等问题,成为构建下一代高算力低功耗芯片的核心材料。

图3 理想的晶体管沟道材料-碳纳米管[5-6]Fig.3 Ideal channels for logic devices - carbon nanotubes

1 碳纳米管集成电路技术研究进展

自1998年第一个碳纳米管晶体管问世以来,碳纳米管优异的电学特性和本征材料优势即引起了学术界和工业界的广泛关注。经过二十几年的不断研究,碳纳米管电子学的关键基础性问题已经基本解决,技术成熟度不断提高,产业化进程也迎来曙光,但是距离规模制造和实际应用尚面临一定的挑战。本文将从材料、器件和系统集成三个方面介绍碳基集成电路技术的研究进展,总结在推向产业化过程中存在的一些困难,并对其下一步的发展进行展望。

1.1 芯片用碳纳米管材料

为了构建高性能的碳纳米管集成电路,碳纳米管材料需要满足以下几点:(1)半导体纯度大于99.9999%;(2)碳纳米管密度100-200 根/um;(3)平行阵列,大面积均匀以及小尺度范围内(pitch uniformity)很好的一致性;(4)管径分布集中,管径大小合适(1.2-1.5 nm);(5)低缺陷;(6)表面干净,无吸附分子或杂质。

目前芯片用碳纳米管薄膜材料的制备方式主要有两种:化学气相沉积和溶液提纯与排布。

首先是化学气相沉积的方法:高温条件下,含碳气体在金属催化剂颗粒表面裂解,并生长出碳纳米管。这种方法的优势是碳纳米管阵列平行度高,碳管表面干净,如图4(a)所示,劣势是高温气相沉积过程中碳纳米管的半导体纯度和管径分布的控制比较困难,金属催化剂条带会影响大面积的均匀性,同时金属催化剂能否完全去除也有待验证。北京大学李彦教授课题组和张锦教授课题组设计了高熔点合金,使其在高温生长过程中保持其晶态结构,在某个晶面更容易催化生长手性富集的碳纳米管,手性控制可以达到90%以上[7-8],如图4(b)和4(c)。结合热流法[9],半导体碳纳米管的纯度可以进一步提升,如图4(d),但是这个过程会造成碳纳米管阵列密度的一致性变差。总的来说,基于化学气相沉积的方法制备高纯度高密度的均匀碳纳米管阵列,目前技术成熟度相对较低,还处在实验室阶段。

图4 CVD 方法制备碳纳米管阵列和热流法提纯[7-9]Fig.4 Carbon nanotube arrays prepared by CVD and purified by thermocapillary method

另外一种方案是基于溶液体系进行碳纳米管的提纯和排布,具体可以分为两类:一类是基于小分子和水相溶剂,采用小分子吸附在碳纳米管表面,通过色谱层析或双相萃取等方式,实现碳纳米管的提纯,目前产率较低,纯度一般低于99.9%[10-13];另一类是基于共轭高分子和有机相溶剂[14-17],共轭高分子和碳纳米管粉末分散在有机溶剂中,进行超声分散,在这个过程中,包裹了高分子的金属型碳纳米管,相互作用较强,碰撞后容易形成管束;未被高分子包裹的碳纳米管,互相碰撞后也容易形成管束,同时碳纳米管本身在有机溶剂中溶解度很低;经过高速的密度梯度离心,包裹了高分子的金属型碳纳米管管束和未被高分子包裹的碳纳米管管束将形成沉淀,稳定分散在溶液中的主要是包裹了高分子的半导体碳纳米管和多余的高分子,从而实现半导体碳纳米管的提纯。其中共轭高分子的结构(包括主链和支链)、空间构象,分子量分布等对碳纳米管提纯的选择性和产率等都较为重要。

图5 基于共轭高分子的溶液法碳纳米管提纯[17]Fig.5 General process of dispersion and sorting of SWNTs via conjugated polymer

目前使用较多的共轭聚合物包括芴基聚合物(PFO)和咔唑基聚合物(PCz)。美国国家标准局的Jeffrey L.Blakburn 等人研究了芴基聚合物分散大管径(1.3nm)碳纳米管的能力,其中PFO-BPy的选择性超过99%[18];苏州纳米所的李清文研究组利用聚咔唑分散提纯半导体碳纳米管,实现了超过99.9%的半导体选择性;北京大学彭练矛课题组进一步发展了多次分散离心的方法,将半导体纯度提高到99.9999%以上[19-20];其它提纯效果较好的共轭高分子还包括:斯坦福大学鲍哲南教授课题组提出的含亚胺键的可去除、可回收的共轭高分子PF-PD,用于半导体碳纳米管的分离提纯,半导体纯度超过99.995%,并且这类高分子的主链中的亚胺键暴露于酸性环境中,容易发生断裂,分解形成小分子,较容易从碳纳米管表面去除[21]。

图6 用于碳纳米管提纯的代表性共轭高分子[18-21]Fig.6 Most used conjugated polymer for s-SWNT sorting

从提纯后的半导体碳纳米管溶液到可用于流片的碳纳米管晶圆,还需要经过碳纳米管薄膜排布的过程。碳纳米管薄膜材料,从形态来说,可以分为无序网络状和顺排阵列两类。网络状碳纳米管材料,目前制备工艺较成熟,可以应用于微米级和亚微米级的碳基集成电路。更先进制程的碳基集成电路则需要用到阵列碳纳米管,以满足一致性及驱动电流密度等要求。碳纳米管顺排的方式包括:基底和模板诱导[22-23]、Langmuir-Blodgett/Langmuir-Schaefer(L-B/L-S)自组装[24]、刮涂(Shearing)[25]、蒸发自组装[26]、真空抽滤[27]、双液相界面自组装[20,28]等。目前进展较大的三个方向:(1)双液相界面自组装的方法[20]:北京大学彭练矛研究组,基于咔唑高分子体系的碳纳米管溶液,采用双液相自组装的方式,实现了高密度大面积顺排的碳纳米管阵列,密度达到100-200 CNTs/um,如图7(a),并在此基础制备了高性能的碳纳米管环振电路和射频器件[29];威斯康辛大学Arnold 课题组,基于PFO-Bpy 高分子体系的碳纳米管溶液,发展了Ta-FESA 的方法,实现大面积快速排列,碳纳米管密度约50 CNTs/um[30];(2)L-B/L-S 的方法:IBM 研究组采用L-S 自组装的方法,制备了高密度碳纳米管顺排阵列,密度大于200 CNTs/um[24],如图7(b);(3)基底或模板诱导组装的方法:IBM 研究组设计了氧化铪/氧化硅周期性的基底结构,通过氧化铪表面修饰的分子与碳纳米管表面分子的化学交换作用诱导碳纳米管排列[22];北京大学孙伟课题组利用单链DNA 的自组装作用构建了具有规整阵列结构的沟槽,然后对碳纳米管表面进行特异性修饰,使得修饰过的碳纳米管能够精准的被“拉”进设计好的DNA 沟槽中,从而实现高平行性和小尺度一致性的碳纳米管阵列排布[23],如图7(c)。

图7 碳纳米管阵列排布方法[20,23-24]Fig.7 Alignment of carbon nanotubes

1.2 碳纳米管晶体管技术

碳纳米管晶体管的输运特性与硅基晶体管有所不同。小偏压下硅基晶体管的输运一般描述为:

碳纳米管晶体管的输运方程,在弹道或准弹道输运的情形下,可以描述为:

(1)无掺杂碳基CMOS 技术

碳纳米管的单原子层特性和超强的C-C 键的共价特性使得传统的离子注入掺杂方式很难实现,而表面吸附离子进行电荷掺杂的方式又较不稳定,因此需要发展新的晶体管技术来实现高性能碳基CMOS。由于碳纳米管完美晶格、表面无悬挂键、低维有限态密度和稳定的物理化学性质(一般不会发生界面反应)等特点,金属和碳纳米管之间理论上不会出现费米钉扎现象,可以选择合适功函数的金属作为源漏接触,与碳纳米管的导带或价带能带匹配,实现电子或空穴的无势垒注入。但是实际情况更为复杂,金属与碳纳米管接触后,其有效的功函数还与金属与碳纳米管的作用方式、作用强度以及浸润性等相关。

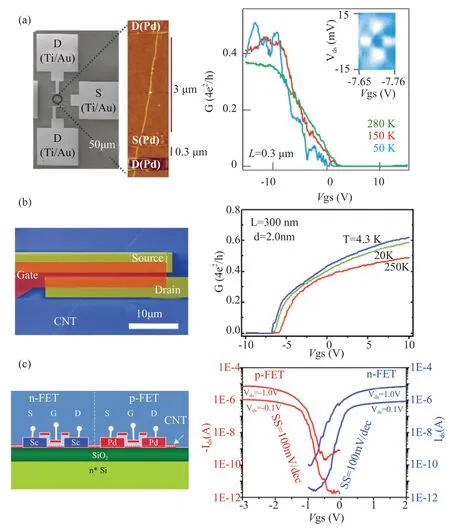

2003年斯坦福大学戴宏杰教授研究组使用钯(Pd)作为源漏金属,实现了欧姆接触,首次制备了弹道输运的碳纳米管P 型晶体管,如图8(a),开态电导接近理想量子电导G0[31];接着采用铝(Al)作为接触,制备了碳纳米管NMOS,但是Al 和碳纳米管的接触存在肖特基势垒,其开态电流明显小于同等尺寸的PMOS 晶体管[32];2005年,IBM 研究组进一步研究了不同金属与碳纳米管的接触特性,及其对管径的依赖效应[33]。接下来需要解决的即是高性能N 型碳纳米管晶体管的制备。使用更低功函数的金属作为接触,面临着接触容易被氧化、工艺条件苛刻等难题,实验上一直无法制备出与P 型晶体管性能相当的高性能N 型器件,制约着碳纳米管CMOS 技术的发展。直到2007年北京大学彭练矛研究组采用低功函数的Sc 作为N 型器件的源漏接触,发现其与碳纳米管具有很好的浸润性和合适的作用强度,是实现高性能NMOS 的理想金属材料,在实验上首次制备了弹道输运的碳纳米管NMOS 器件,室温和低温下均实现了欧姆接触,如图8(b),其开态电导也接近理想量子电导G0[34]。在此基础上彭练矛研究组进一步发展了无掺杂碳基CMOS 技术,实现了高性能碳纳米管CMOS 器件和电路的制备,如图8(c),为碳纳米管集成电路技术的发展打下了坚实的基础[35]。

图8 无掺杂碳基CMOS 技术[31,34-35]Fig.8 Doping-free carbon nanotube CMOS

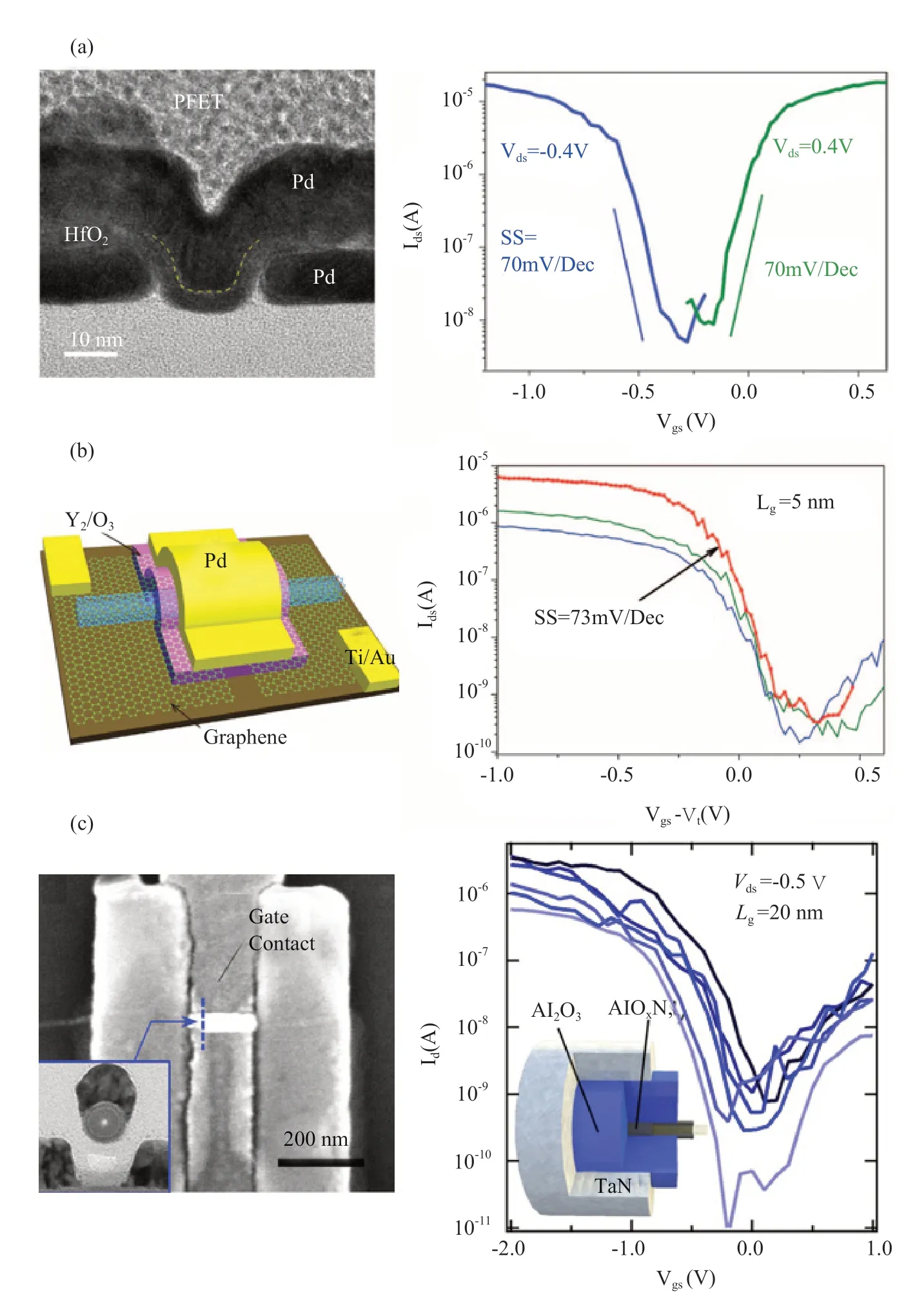

(2)碳纳米管晶体管的尺寸缩减和弹道输运

碳纳米管的一维单原子层结构,使其具有优异的静电学栅控特性,实现快速有效的开关。仿真结果显示,在碳纳米管环栅晶体管中,栅长为5nm 的情况下,晶体管的亚阈值摆幅(SS)仍可保持在60 mV/dec 附近[36]。北京大学的彭练矛研究组采用平面自对准顶栅结构制备了10nm 栅长的碳纳米管CMOS器件,器件的亚阈值摆幅约70 mV/dec,如图9(a),远小于10nm 栅长的硅基晶体管器件(90-120 mV/dec);当栅长进一步缩减到5nm 时,由于源漏金属对栅极电场的静电屏蔽效应,平面栅结构下的碳纳米管晶体管的亚阈值摆幅明显上升[37]。为了增强亚5nm 栅长下的碳纳米管晶体管的栅控,实验中,一个方法是采用超薄的石墨烯作为源漏接触,以减少其对栅极电场的屏蔽作用,在5nm 的栅长下,碳纳米管晶体管的SS 降低为73 mV/dec,如图9(b),取得了显著效果[37];另一个可行的方法是采用环栅结构,栅极的静电控制将进一步提高,有助于在亚5nm 的极限缩减情况下,降低SS,维持有效的栅控。环栅结构的另一个优势是,减少了栅介质和基底的界面作用,结合静电控制的提升,将有助于提高碳纳米管器件的一致性,这对于小尺寸器件的规模集成至关重要。IBM 研究组制备了碳纳米管环栅器件,器件栅长为20 nm-30 nm,亚阈值摆幅约85 mV/dec,如图9(c),与理论仿真的环栅器件的60 mV/dec 的SS 相差较多,这可能主要是由于栅介质层中的缺陷电荷密度和界面态密度过高,影响了栅控[38]。需要进一步开发碳纳米管清洗工艺和优化原子层沉积(ALD)工艺,提高栅堆垛界面质量,减小界面态密度,以真正发挥出碳纳米管晶体管环栅结构的优势。

图9 栅长极度缩减的平面顶栅和环栅碳纳米管晶体管[37-38]Fig.9 Extremely scaling CNT FET with planar top gate (TG) and gate-all-around (GAA) structure

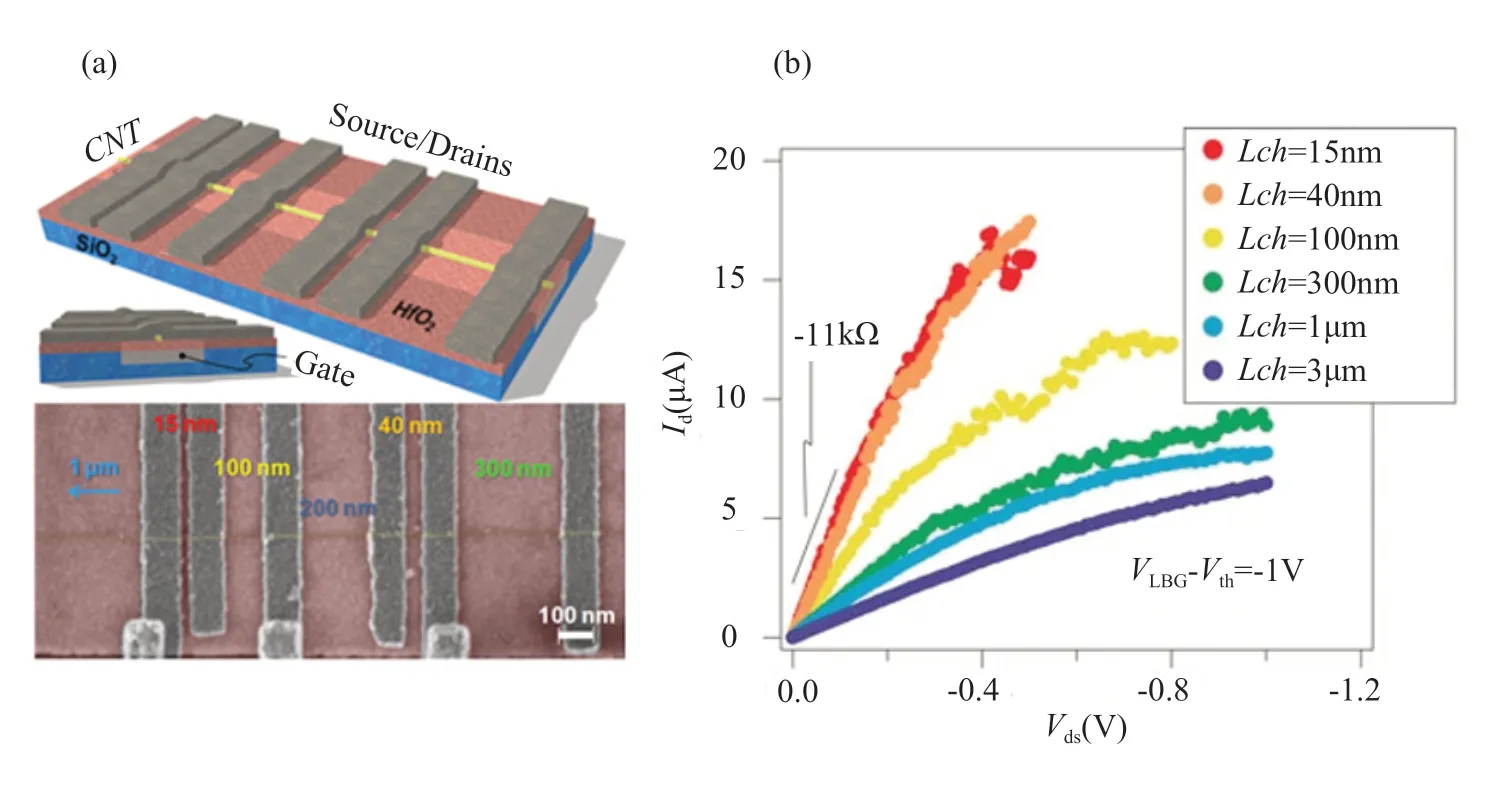

碳纳米管的特殊晶格结构,使其费米面附近的电子态主要是扩展态,室温下电子和空穴都具有极高的本征迁移率。在小偏压情况下,光学声子未被激发,声学声子散射较弱,其平均自由程可达到微米量级;在强场条件下,光学声子散射占主导,其平均自由程也有几十纳米。当碳纳米管晶体管的沟道尺寸接近或小于其平均自由程时,其输运过程就进入了准弹道或弹道输运。IBM 研究组基于单根碳纳米管制备了不同栅长的碳纳米管P 型晶体管,如图10,当栅长缩减到40 nm 以下时,器件在室温下表现出弹道输运特性[39]。

图10 碳纳米管弹道晶体管[39]Fig.10 Ballistic CNT FET

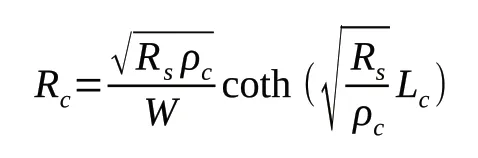

碳纳米管晶体管的尺寸缩减,除了沟道长度,还包括接触尺寸的缩减。如前文所述,在弹道输运情况下,器件的开态电流完全由接触电阻决定。实现小的接触尺寸下,有效的载流子注入,即低接触电阻,是碳纳米管晶体管技术研究中需要解决的一个重要问题。常见的碳纳米管晶体管的接触方式可以分为两种:面接触(side contact)和端接触(endcontact)。对于面接触,如图11(g)所示,接触电阻RC可以描述为[40-41]:

其中RS为接触下方碳纳米管的电阻率, 为金属和碳纳米管接触界面的电阻率,Lc为接触长度。RS与金属接触对碳纳米管的静电掺杂程度有关, 取决于金属与碳纳米管的作用强度,与制备工艺有关。一般来说,金属与碳纳米管的作用强度较大时,载流子从金属到碳纳米管的注入效率较高,即在更小的Lc下即可实现载流子的充分注入,但是注入过程中载流子的透射率较低,接触电阻比较大;在Lc足够大的情况下,选择载流子透射几率更高的金属作为接触,例如Pd,可以实现更小的接触电阻,如图11(c)所示。IBM 研究组制备了不同接触尺寸,相同沟道长度(Lch=40 nm)的碳纳米管P 型弹道晶体管,研究了接触长度(Lc)的尺寸缩减效应[39]: Pd 作为接触时,在Lc小于50nm 后,Rc即随着Lc减小急剧上升,如图11(a)和(b)。

为了提高小尺寸Lc情况下的载流子注入效率,一种可能的办法是优化金属接触的沉积工艺,改善金属和碳纳米管的界面质量。斯坦福大学Philp Wong 教授研究组改进了Pd 的蒸镀工艺,在提高单位接触长度载流子注入效率的同时,维持了高透射几率,实现了Lc为10 nm 情况下的低接触电阻[42],如图11(h)所示。不过这种方法对碳管表面洁净度和沉积工艺控制等要求较高,器件的一致性还有待提高。

碳纳米管的一维特性提供了解决接触尺寸缩减问题的另一个方案,即端部接触(end-contact)。IBM 研究组采用金属Mo 或者Ni 与碳纳米管接触,经过高温退火处理,金属与碳纳米管形成了稳定的碳化物,金属原子与碳原子之间形成强化学键,实现了高效的载流子注入,其触电阻不依赖于接触长度,表现出显著的尺寸缩减优势[43-44],如图11(d)(e)和(f)所示。

图11 碳纳米管晶体管接触尺寸缩减研究[39-43]Fig.11 Contact length scaling of CNT FETs

为了充分展示碳纳米管晶体管的尺寸缩减优势,IBM 研究组采用端部接触,分别基于单根碳纳米管和阵列碳纳米管,制备了亚10 nm 栅长和接触长度的碳纳米管P 型晶体管,整个器件的尺寸约为40 nm,如图12(a)所示,对应的接触栅间距(contactedgate pitch, CGP)约为30 nm,远远领先于硅基5 纳米技术节点的CGP[45]。其中基于阵列碳纳米管的底栅器件,如图12(c)和(d),相较于相近工艺节点的硅基FinFET 和硅纳米线器件,表现出显著的低电压工作优势,从实验上验证了碳纳米管晶体管低功耗高速开关的优势和潜力。

图12 最小的碳纳米管晶体管- 器件尺寸40 nm[45]Fig.12 Smallest CNT FET- 40 nm footprint

(3)碳纳米管晶体管的高k 栅介质制备

在硅基CMOS 技术的发展过程中,氧化硅扮演了很重要的角色。作为栅介质,氧化硅与硅沟道之间的高质量界面保证了器件的有效栅控以及器件的高可靠性,即便在先进工艺制程(45 纳米工艺节点之后),采用了高k 栅介质和金属栅极,依然将氧化硅作为高k 栅介质与硅沟道之间的过渡层,以降低界面态密度。对于碳纳米管晶体管来说,缺少类似氧化硅这样的碳基氧化物作为栅介质层。碳纳米管晶格结构完美,表面无悬挂键,采用传统的ALD工艺,很难在其表面生长高质量均匀的介质层。

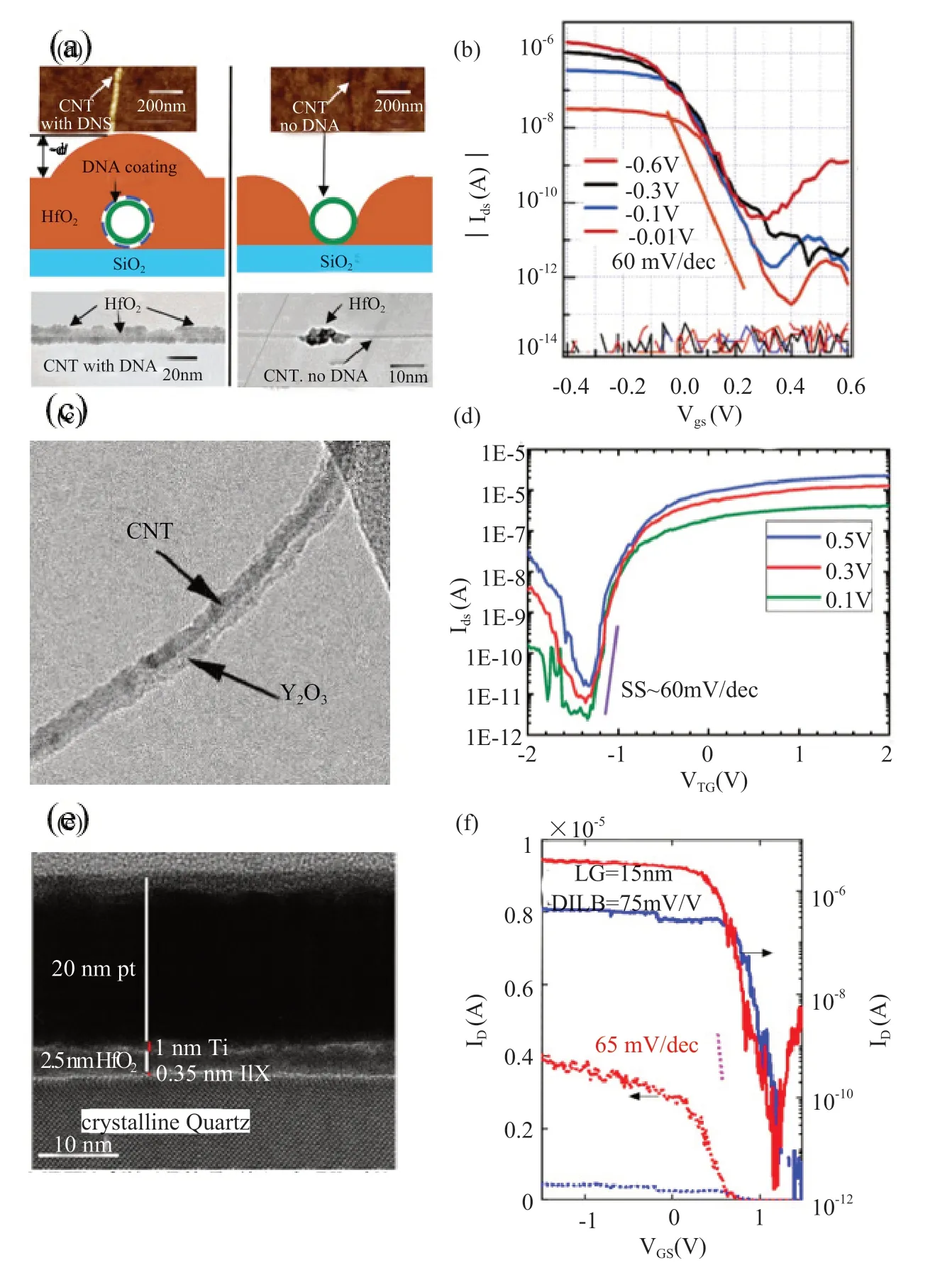

斯坦福大学戴宏杰研究组采用DNA 分子修饰碳纳米管,作为种子层,ALD 生长了高质量的氧化铪栅介质,室温的亚阈值摆幅达到理论极限的60 mV/dec[46],如图13(a)和(b)。北京大学的彭练矛研究组,研究发现金属钇(Y)与碳纳米管具有很好的浸润性,通过电子束蒸发镀膜的方法,在碳纳米管表面均匀沉积一层金属钇薄膜,在空气或氧气氛围下高温氧化,就可以得到均匀包裹在碳纳米管表面的高质量的氧化钇栅介质。以此制备的碳纳米管顶栅晶体管器件,其亚阈值斜率摆幅也达到了理论极限60 mV/dec[47],如图13(c)和(d)。

不过DNA 修饰的方法不大适合规模集成电路的制备工艺,器件的一致性、可靠性和工艺的重复性难以保证;蒸镀金属钇,热氧化制备氧化钇栅介质的方法,不适合环栅工艺,并且得到的氧化钇薄膜呈多晶状态,当栅介质缩减到很薄时,其可靠性和一致性也会受到影响。因此还需要继续开发碳纳米管晶体管高k 栅介质制备技术,实现低界面态密度和高可靠性的栅介质层。斯坦福大学的Philip Wong 研究组和台积电合作,发展了Al2O3的ALD 生长工艺,作为过渡栅界面层,其等效EOT 约0.5 nm,在其上ALD 生长了HfO2作为高k 栅介质,以此制备碳纳米管顶栅晶体管,对于15 nm 栅长的器件,其SS 约65 mV/dec,DIBL 小于20 mV/V,表现出优异的静电学栅控特性[48],如图13(e)和(f),为ALD 生长高质量的碳纳米管晶体管栅介质提供了一种可能方案。

图13 碳纳米管晶体管高k 栅介质层制备[46-48]Fig.13 Fabrication of high-k gate dielectric for CNT FETs

1.3 碳纳米管集成电路

碳纳米管材料和晶体管技术的发展与积累为碳基集成电路的制备奠定了基础。随着CNT 材料与器件技术的不断突破与创新,基于CNT 的碳基电子学逐渐从基础性研究转向实际应用,科研人员已经成功实现了各种基础逻辑单元和具有一定功能与复杂度的碳基集成系统。

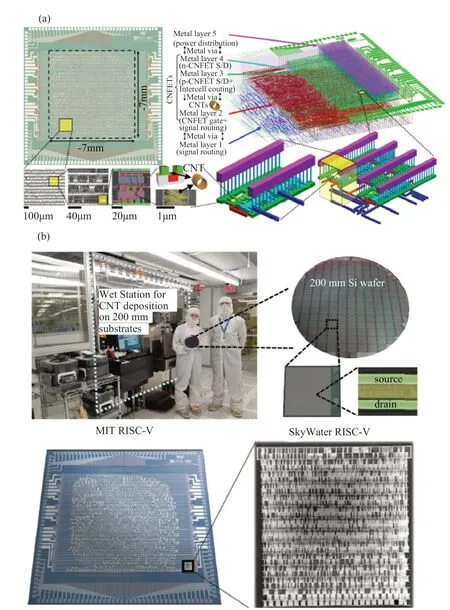

(1)碳纳米管中大规模集成电路

2013年,斯坦福大学报道了全球首台碳纳米管原型计算机。采用PMOS 工艺,每个碳纳米管原型机包含178 个碳纳米管晶体管,采用MIPS 指令集架构,配合硅基电路,实现了20 个不同指令[49]。2017年,北京大学彭练矛课题组采用CMOS 工艺制备了首个碳纳米管4 位全加器和D-Latch、MUX2X1 等标准门单元[50]。2019年,麻省理工大学(MIT)Shulaker课题组报道了碳纳米管16 位Risk-V 处理器,流片基于CMOS 工艺,采用标准EDA 工具进行碳纳米管处理器的设计仿真和版图绘制,包含约 14 700 个碳纳米管晶体管,在16 位地址上运行32 位Risk-V 指令集[51],如图14(a)。随后MIT 研究组与美国芯片制造公司Sky Water 合作,在8 英寸工艺线上,基于130 nm 的工艺制程,实现了Risk-V 碳纳米管芯片的流片[4,52],如图14(b),标志着碳纳米管集成电路技术正从实验室走向产业化。

图14 碳纳米管Risk-V 微处理器[51-52]Fig.14 Carbon nanotube Risk-V microprocessor

(2)碳纳米管三维单片集成系统

碳纳米管晶体管技术不需要离子注入掺杂和高温退火过程,工艺热预算在400 度以下,与互连工艺、新型存储技术(如MRAM、RRAM 和PCRAM等)具有很好的工艺兼容性,有望实现三维单片集成,基于近存计算的架构进行芯片设计,解决平面芯片布局中的存储墙等问题,大大提高芯片的算力和能效。2014年,斯坦福大学研究组率先报道了硅基逻辑层、阻变存储层和碳纳米管逻辑层的简单三维单片集成系统[53]。2017年,斯坦福大学和麻省理工大学的研究团队进一步研制了更复杂的感存算一体三维单片集成系统,从下往上,分别集成了硅基逻辑层、碳纳米管逻辑层、阻变存储层和碳纳米管传感+逻辑层[54],如图15(a)和(b)。整个三维集成系统可以作为电子鼻,区分和确定多种常见气味,如柠檬汁、酒精、伏特加和红酒等;2018年该研究团队基于碳纳米管逻辑层与阻变存储层实现的三维单片集成芯片,演示了类脑超维计算系统,用来实现语言分类识别,与对应的硅基电路比较,面积缩减了3 倍,能效提高了约35 倍[55];2019年,麻省理工团队又报道了在硅基图像传感器上在片集成了碳纳米管逻辑电路,对图像信息进行预处理,有效提高图像分类过程的能效[56]。在DARPA 项目的支持下,美国麻省理工大学、斯坦福大学、佐治亚理工大学和Sky Water 等合作,基于130 nm 工艺线和开发的碳基EDA 工具,演示了碳纳米管逻辑层和阻变存储层三维单片集成系统的设计仿真和流片,如图15(c)和(d),在碳纳米管三维单片集成技术的研发上走出了重要一步[4]。

图15 碳纳米管三维单片集成系统[4,54,56]Fig.15 Carbon-based monolithic 3D integration

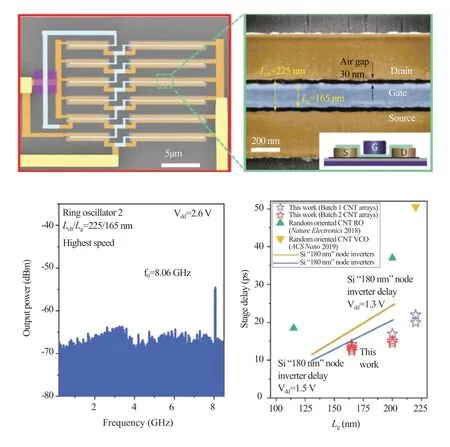

(3)高速碳纳米管集成电路

在单根碳纳米管上,北京大学的研究团队制备了速度(本征门延时)和能效(能量延时积)均优于硅基的碳纳米管晶体管器件,但是电路层面的速度优势却受碳纳米管材料的限制,很长时间没有突破。2018年北京大学彭练矛研究团队基于高质量的网络状碳管薄膜制备了5.6 GHz 的5 阶环振,与相同节点的硅基电路性能相当[57];2020年,彭练矛团队发展了高密度、高纯度的碳纳米管阵列的制备方法,在此基础制备的5 阶环振,其振荡频率超过8 GHz,如图16,代表了目前碳基高速电路的最高水平[20]。环振电路中碳纳米管晶体管的制备采用非自对准工艺,形成“空气”侧墙,以最大程度地减小寄生电容。不过环振电路中的晶体管属于耗尽型,关态电流很大,开关比较低,降低寄生电容的非自对准工艺也较难应用于大规模集成电路。满足实际应用的高速低功耗的碳纳米管逻辑电路的实现还需要在器件结构、阈值电压控制和自对准工艺开发等方面进一步地努力。

图16 碳纳米管高速环振电路[20]Fig.16 High speed carbon nanotube 5-stage oscillators

碳纳米管的高速输运特性更直观地反映在碳基射频器件上。基于高密度碳纳米管阵列制备的碳纳米管射频器件,其电流增益和功率增益截止频率分别高达540 GHz 和306 GHz[29],充分说明了碳纳米管高速工作的优势和潜力。

2 挑战

如前文所述,在材料、器件和系统集成方面,碳纳米管集成电路技术均取得了众多进展,但距离产业化和实际应用尚存在一些问题需要解决。

2.1 高品质碳纳米管阵列薄膜的可控制备

基于共轭高分子方法制备的碳纳米管薄膜材料,还存在着高纯度和高产率较难同时满足、碳纳米管表面包裹的高分子难去除、阵列排布工艺重复性和大面积的均一性有待提高等问题。为了满足先进技术节点碳基集成电路对材料的要求,需要在以下几个方面进行攻关:(1)高分子的可控合成,满足高选择性、高分散率、分子量分布控制、批次重复性、易降解等;(2)高鲁棒性的顺排工艺,满足小尺寸的一致性、大面积均一性、高重复性、单层和密度可控等要求;(3)高分子去除工艺,满足无损伤去除和完全去除;(4)材料表征,包括纯度、形貌、杂质、缺陷等,建立表征方法、表征标准,与器件电学特性建立对应关系等。

2.2 面向应用的碳纳米管晶体管技术

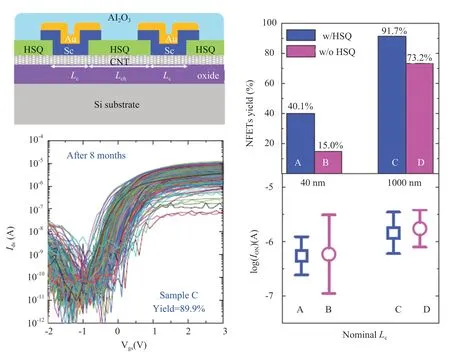

(1)高性能高可靠性N 型碳纳米管晶体管的制备

基于阵列碳纳米管,北京大学研究组和IBM 研究组均制备出了高性能的P 型碳纳米管晶体管,而与之性能匹配的N 型晶体管的制备则面临着一些困难。使用Sc 等低功函数金属作为接触制备N 型晶体管,Sc 较容易被氧化,尤其是在小的接触尺寸下,部分氧化的Sc 接触,其载流子注入能力大大下降,导致接触电阻急剧增加。当采用顶栅自对准结构时,Sc 与高k 氧化物栅介质在热处理过程中,也容易发生夺氧反应,造成接触质量下降和栅介质漏电等问题。因此需要对Sc 进行较充分的保护,IBM 研究组制备了底栅器件,通过侧面和顶部的钝化保护层,大大提高了小尺寸接触长度下,碳纳米管NMOS 器件的成品率和一致性[58],如图17 所示。对于顶栅器件或者环栅器件,也需要设计合适的器件结构,选择有效的钝化层,在不影响器件性能的同时,提高碳纳米管NMOS 的成品率、一致性、热稳定性和可靠性等。

图17 Sc 接触碳纳米管NMOS 的钝化保护[58]Fig.17 Passivation of Sc contacted CNT NMOS

另一种实现N 型晶体管的方式是使用较高功函数、稳定性好的金属作为源漏接触,通过静电掺杂调整接触区的能带弯曲,实现载流子的隧穿注入,以此避免Sc 等低功函数金属的不稳定性带来的问题。具体的实现方式包括:局域底栅结构,选择含有固定电荷的介质,如HfOx,AlOx和SiNx等,沉积在沟道表面,实现静电掺杂[59],如图18(a);顶栅或环栅结构,选择含有固定电荷的栅介质层,如YOx[60],或者通过栅介质组合,形成偶极子,如采用AlOxNy和HfO2 叠层作为栅介质,界面偶极子实现对沟道的电子掺杂[38],实现N 型碳纳米管晶体管,如图18(b)。

图18 静电掺杂实现碳纳米管NMOS[38,51]Fig.18 CNT NMOS with electrostatic doping

这种静电掺杂和隧穿注入的方式也存在着一些隐患:①使用配比不完整的金属氧化物实现静电掺杂,如HfOx,膜层中存在较多氧空位和缺陷态,和沟道的界面质量也较差,容易引起沟道中载流子散射,也不利于栅控;同时非理想配比的氧化物,其热稳定性也较差,在热处理过程中,膜层形态容易发生变化,改变静电掺杂的效果;②偶极子静电掺杂的方式相对比较稳定,作为栅介质时,其界面态的优化是关键;另外器件的开态电流、阈值电压和亚阈值摆幅三者的协同优化也将是一个挑战,尤其是在器件尺寸缩减的情况下;③隧穿注入的方式下,实现器件的高一致性,相较于欧姆接触的无势垒注入,将更加困难。

(2)碳纳米管晶体管阈值电压的控制

与硅基器件不同,碳纳米管晶体管不适合采用离子注入的方法进行掺杂,其阈值电压的调控主要通过静电掺杂来实现。一种方法是采用局域底栅的器件结构,沉积含有固定电荷的钝化层在沟道上方,来实现静电调控,但是这种方式可能会导致栅控效率的下降,在小尺寸下,器件的开关态、阈值电压和亚阈值摆幅较难平衡。另外一种方法是通过调节栅堆垛,包括栅介质和栅金属,来实现阈值电压的调整。但是考虑到界面态密度控制、热稳定性、工艺兼容性和栅控特性等限制条件,单一通过栅堆垛调控来同时满足碳纳米管PMOS 和NMOS 对阈值电压的要求,工艺难度挑战较大。因此碳纳米管晶体管阈值电压的调控还需要更多的调控手段,例如,侧墙区的静电调控。

(3)满足综合性能指标的器件结构和工艺开发

从第一个底栅碳纳米管晶体管发展至今,各研究组相继演示了丰富的碳纳米管晶体管器件结构和工艺,包括:局域底栅、高k 自对准顶栅、反馈栅、非对称栅和环栅等,从实验上充分验证了碳纳米管作为逻辑器件和射频器件的沟道材料的优势和潜力。但是从实际应用和产业化规模制备的角度,面向高速低功耗芯片应用的碳纳米管晶体管,需要满足严苛的综合技术指标的要求,包括高开态、低关态、阈值电压控制、自对准工艺、低寄生、可靠性、热稳定性、工艺兼容性、一致性、良率等等,已发表的技术方案大多是实现了单个或部分指标的优化,尚存在明显短板,仍需要学术界和产业界的共同努力,针对不同应用场景下各自的技术指标要求,开发出满足实际需求的技术方案。

2.3 三维单片集成系统的优化设计

三维单片集成的近存计算架构可以最大程度地发挥碳基集成电路技术的优势,突破存储墙等限制,满足人工智能、大数据、物联网、自动驾驶等对高算力低功耗的要求,另一方面三维单片集成技术可以实现将更多的功能单元在片集成,包括传感、存储、计算、通信等等,提高能效,降低成本,实现功能多样化。但是目前三维单片集成系统的架构和算法设计还不成熟,如何实现三维集成的自动化设计,从不同层级,包括晶体管级、门单元级、功能单元级、系统级,进行三维设计优化,是目前存在的重要挑战。

另外在先进工艺节点,三维单片集成系统的设计,除了性能-功耗-面积(集成度)-功能方面的平衡和优化,还需要考虑热管理的设计和布局,统筹规划[61]。

图19 碳基三维单片集成系统[61]Fig.19 Cabon-Based monolithic 3D integration

3 总结与展望

碳纳米管集成电路技术经过20 多年的发展,解决了一系列关键性基础问题,目前正处在从实验室向产业化过渡的阶段。为了真正发挥碳纳米管晶体管弹道输运和三维单片集成等方面的优势,仍需要在科学和技术层面解决一些关键技术问题,包括满足先进技术节点的碳纳米管阵列薄膜的可控制备、面向应用的碳纳米管晶体管技术的开发和三维单片集成系统架构、算法、EDA 工具和工艺的协同建立等,评价标准和研究导向也需要从部分指标优化向综合指标协同提升转变。

目前我国在芯片行业被严重桎梏, 碳纳米管集成电路技术的兴起发展和巨大潜力为我国未来信息电子产业,尤其是高端芯片技术,提供了一次宝贵的“换道超车”的机会。我国在碳基集成电路材料和器件方向的研究开展较早,在本世纪初即开始了布局,经过近20年的努力,已经发展了体系完整的原创性技术,具备自主知识产权,为大规模产业化方向的突破奠定了基础。

当下世界各国都对下一代芯片技术密切关注并巨额投入,对我国而言,自主可控的芯片技术更是尤为重要,加快布局和推进碳基集成电路技术发展的紧迫性日益凸显,需要从国家层面制定战略、协调资源,将材料、器件物理、系统设计、微纳加工等相关各领域的人才和力量集合起来,提供一个长期稳定的支持环境,牢牢把握住后摩尔时代非硅基技术发展的机遇期,抢占下一代半导体技术战略制高点,形成中国自己的碳基纳电子产业。

利益冲突声明

所有作者声明不存在利益冲突关系。