基于光电忆阻器的新型加法器电路设计与仿真印技

黄诗诗,金湘亮,汪 洋,钟泽宇

(湖南师范大学物理与电子科学学院,湖南 长沙 410081)

0 引言

1971年,蔡少棠教授根据对称性理论提出表现电荷和磁通量关系的非线性无源两端电路元件-忆阻器[1]。1976年,LEON O. CHUA和SUNG MO KANG将忆阻器概念推广,称其为忆阻型非线性动力学系统[2]。2008年,Hewlett- packar(HP)实验室 Dmitri B. Strukov等人证实了忆阻器的存在,验证了Chua教授的推论,成功制备出实际物理器件[3]。2008年,Strukov D B.等介绍了忆阻器和忆阻系统在模型分析、仿真记忆行为以及基本电路和器件设计中的应用[4]。2010年惠普公司提出了基于忆阻器件的实质蕴含逻辑并且实现布尔逻辑[5]。2012年,S.Shin等人通过适应性地控制忆阻器的条件设置操作同时控制开关,实现了基于忆阻器的异或逻辑功能[6]。2015年,Yaxiong Zhou等人提出了 CMOS/忆阻器混合非易失性异或门[7]。2018年,Dong Z等人设计了基于阈值忆阻器的逻辑电路,实现了 NAND,AND,OR,NOR门操作,总延迟小,效率高[8]。2017年,Teimoori M基于忆阻通用逻辑门设计了混合忆阻器-CMOS乘法器[9]。2019年,冯朝文将一种电压阈值型压控双极性忆阻器模型与CMOS反相器混合设计实现基本逻辑门[10]。2020年,杨辉等人提出一种能在同一电路中实现 AND-OR-XORXNOR 4种基本逻辑操作的忆阻器-CMOS逻辑电路,提高了硬件可实现性[11]。虽然基于忆阻器的数字逻辑电路已有大量研究者关注,但电路本身都具有局限性。例如脉冲电压约束条件要求很高等问题。本文设计的异或门使用一种新型光电忆阻器设计而成,进而实现半加器的逻辑功能,结构简单,使用元器件少,并且光电脉冲约束条件要求低,外加电压序列简单,使用双极电压源即可完成。与此同时,该技术与CMOS技术完全兼容,将其应用在数字电路中,可以实现更快的开关速度以及更高的集成密度。有广泛应用前景。

1 加法器设计与仿真

1.1 雪崩光电二极管的忆阻特性理论分析

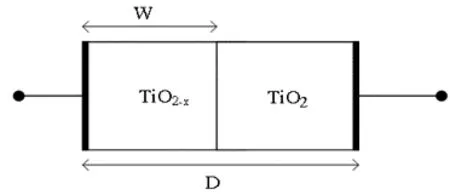

雪崩光电二极管(Avalanche Photo Diode)是一种光敏元件。在P-N结二极管两端加上反向偏压,同时外加光照条件时,P-N结吸收射入的光进而形成光电流,此时若加大反向偏压,空间电荷区中电场将会增强,晶体原子中的共价电子对被激发形成电子-空穴对,光电流(此时为反向电流)将成倍地激增,因此P-N结发生雪崩击穿形成雪崩效应。雪崩产生的载流子较多,光电流大,此时APD的阻值较小,称之为低阻态。在理想无光条件下或突然无外加偏压时,光电二极管的雪崩无法持续,因而雪崩淬灭,内部载流子迅速减小,但是由于等效结电容的存在,电容拥有存储电荷的功能,会释放一定的载流子,减缓淬灭的速度,该过程为雪崩光电二极管雪崩的淬灭过程,称之为高阻态。参考HP实验室Williams等人制备出如图1所示的Pt/TiO2-x/TiO2/Pt忆阻器结构。设忆阻器主体宽度为D,掺杂层宽度为W,当在忆阻器两个端口加上电压时,流经的电流会引起忆阻器内部掺杂了氧原子空位的 TiO2层中有氧空位的移动,此时,忆阻器阻值将发生改变。当电流从左往右流动时,有氧空位的移动使得掺杂层宽度W变宽,忆阻器阻值逐渐变小,当W无限接近于D时忆阻器达到最小阻值;当电流从右往左流动时,有氧空缺位的移动使得掺杂层宽度W 变窄,忆阻器阻值变大,当 W 无限接近于 0时忆阻器达到最大阻值。断开电流时,忆阻器内部的有氧空位不移动,保持断电瞬间的状态不发生改变,因此忆阻器的阻值保持断电时刻的瞬时值不变,不会回到初始状态,该特性即TiO2忆阻器的掉电记忆特性。由此可见,雪崩光电二极管的高低阻态与忆阻器模型的高低阻态类似。因此在理论分析层面,雪崩光电二极管可以用作忆阻器件在电路中使用。

图1 Pt/TiO2-x/TiO2/Pt忆阻器结构Fig.1 The structure of Pt/TiO2-x/TiO2/Pt memristor

1.2 雪崩光电二极管等效电路模型(APD模型)的Multisim仿真

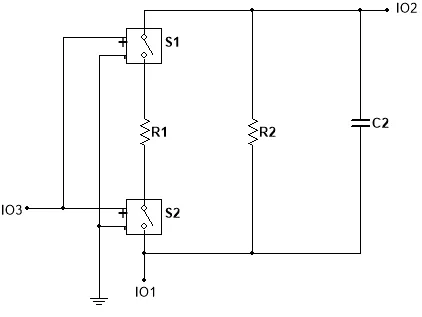

下图2为雪崩光电二极管的等效电路模型,在Multisim中仿真以及测试其忆阻特性。S1和S2为光电的开关,用来感受光脉冲,当出现光脉冲时,APD感光发生雪崩,从而使APD切换到低电阻的状态;R1为 APD导通时的等效电阻;R2为未触发时的等效电阻。C2为等效结电容(理想无光条件下或突然无外加偏压,雪崩淬灭,内部载流子迅速减少,但是等效结电容可以存储电荷,释放一定的载流子)。在Multisim中建立APD模型的框图。接口1(IO1)代表 APD的阳极,图中接口2(IO2)代表APD的阴极,图中接口3(IO3)代表APD的光控端,仿真时输入具有脉冲的双极电压源,使得APD的忆阻等效电路更为简单。立足于元件本身的需要,在仿真过程中将光强度转化成与电压有关的参数,并且设置为最佳元件参数。电压源的电压越大代表给与的光强度(光脉冲)越大;当电压源的电压为0时,代表无光照射(无光脉冲),因此无法破坏二极管中载流子平衡,也就无法产生雪崩,进而无法导通。

图2 APD等效电路模型Fig.2 Equivalent circuit model of APD

1.3 雪崩光电二极管忆阻特性的实验验证

用 Multisim对雪崩光电二极管进行瞬态分析,将数据导出进行绘图,发现该雪崩光电二极管具有夹点返回线的特征,即磁滞回线[12],如图3所示。根据忆阻器的三条简单判据:V-I特性曲线为磁滞回线;电信号扫描频率增大时,磁滞回线波瓣面积减小;当输入信号频率趋近无穷大时,磁滞回线收缩为单值函数。因此得出,雪崩光电二极管是一种新型的光电忆阻器件。

图3 光电忆阻器的磁滞回线Fig.3 The Hysteresis loop of photomemristor

1.4 基于光电忆阻器的新型半加器设计

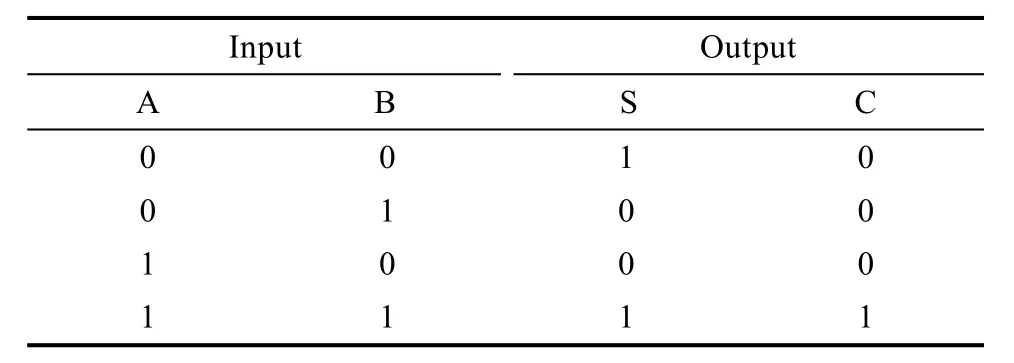

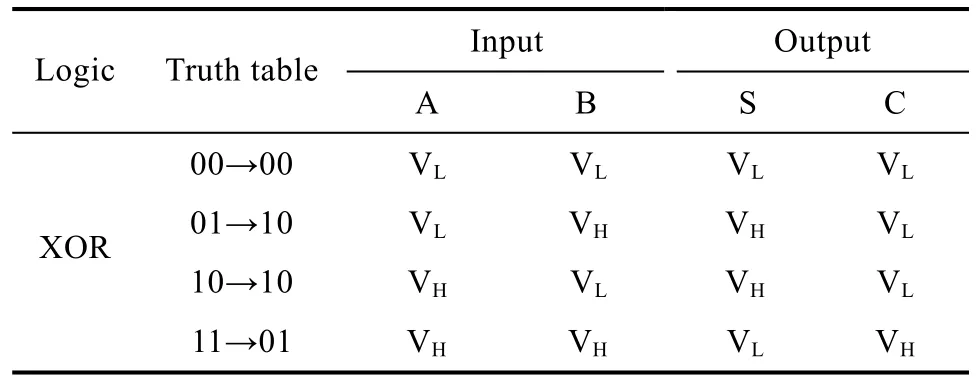

分析异或逻辑门的表达式,如公式(1)所示;分析半加器的逻辑表达式,如公式(2)所示;分析半加器真值表如表1所示。

表1 半加器的真值表Tab.1 The Truth table of half adder

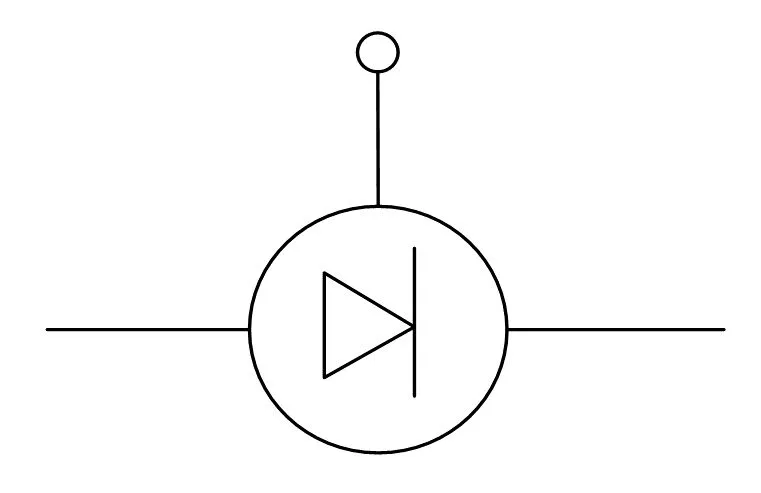

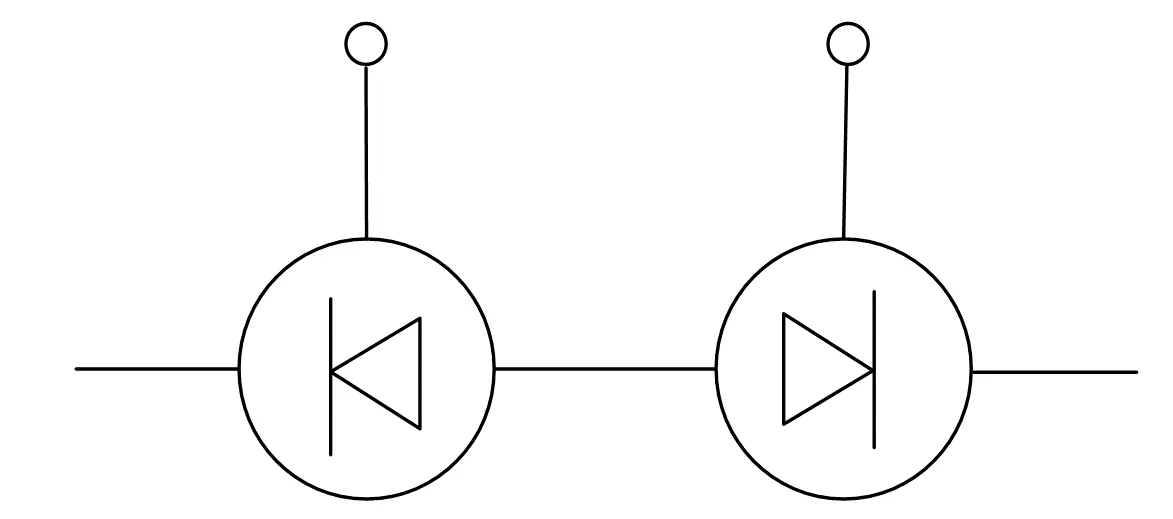

由上述分析可得,使用与门、或门以及非门可以构成半加器。电路设计过程中,本文使用图4代表雪崩光电忆阻器,将其作为光电忆阻器的符号,规定左端为阳极,右端为阴极。其忆阻特性已在1.3节中得以验证。如图5,将光电忆阻器的阳极相连得到与门;如图 6,将光电忆阻器阴极相连得到或门。

图4 光电忆阻器的符号Fig.4 The Symbol of photomemristor

图5 基于光电忆阻器的“与”门Fig.5 “AND” gate based on photomemristor

图6 基于光电忆阻器的“或”门Fig.6 “OR” gate based on photomemristor

通过Multisim仿真得到AND-OR逻辑门的波形图如图7所示,通过光迹线以及数据点的展示得出的仿真结果证明了理论分析的正确性,验证了电路的“与”、“或”的逻辑功能。图7中Input A和Input B分别代表了两个不同周期的双极电压源,Output C为AND逻辑门的输出,Output D为OR逻辑门的输出。由波形图分析得到下表 2中“与”、“或”逻辑门的实现过程。

表2 “与”、“或”门实现过程Tab.2 The realization process of AND-OR

图7 基于光电忆阻器的“与”、“或”门波形图Fig.7 The Waveform diagram of AND-OR based on photomemristor

基于上述AND-OR逻辑门的实现构建出如图8所示的半加器模型。

图8 基于光电忆阻器的半加器等效电路模型Fig.8 The equivalent circuit model of a half adder based on a photomemristor

分析该半加器的工作过程:

(1)当输入电压VA = VB = 0 V时,L1、L2不给予光脉冲。当内电场与施加的电场相反且不产生光脉冲时,由于没有雪崩,雪崩光电二极管截止,没有电流通过,则VF1=0;L3、L4给与光脉冲,对应二极管处于导通状态,则VF2 = 0 V;此时L8无论是否给与光脉冲,L7给与光脉冲,输出S与地相连,因此,输出电压VS = VC = 0 V。

(2)当输入VA = 0V,VB = 5 V时,L2给予光脉冲,由于发生雪崩,对应二极管导通,则VF1 = 5 V;L4不给与光脉冲,对应二极管截止,则VF2 = 0 V;此时L7不给与光脉冲,L8对应的二极管施加正向电压,无论是否给与光脉冲,L8对应的二极管导通,因此输出电压 VS = 5 V,VC=0 V。

(3)当输入VA = 5 V,VB = 0 V时,L1对应的二极管正向导通,则 VF1= 5 V;此时不给予L3光脉冲,对应的二极管截止,则VF2 = 0 V;此时L7不给与光脉冲,L8对应的二极管施加正向电压,无论是否给与光脉冲,L8对应的二极管导通,因此输出电压VS = 5 V,VC=0 V。

(4)当输入VA = VB = 5 V时,L1、L2对应的二极管正向导通,则VF1 = 5 V;与门输出VF2= 5 V。此时L7不给与光脉冲,由于正极接地,对应二极管截止。L8给与光脉冲,对应二极管导通,因此输出电压VS = 0 V,VC = 5 V。

1.5 新型半加器功能验证与仿真

由 1.4中分析的 4种情况对该电路逻辑功能进行验证,结果表明,输出波形与理论分析一一对应。

通过Multisim仿真得出半加器波形如下图9所示。表3是对XOR逻辑操作的实现过程的分析,与仿真结果一一对应。

表3 “异或”门实现过程Tab.3 The realization process of XOR

图9 新型加法器的波形图Fig.9 The Waveform diagram of the new adder

2 结论

本文从理论以及仿真方面介绍了雪崩光电二极管的忆阻特性,并设计了基本数字电路逻辑门,即“与”、“或”门,进而结合“非”门设计出基于光电忆阻器的新型半加器。根据仿真结果进一步证明了该设计是可行的。该半加器是在矩形波输入以及光脉冲的控制下实现的其逻辑功能的。它仅由一种光电忆阻器构成,脉冲电压约束条件要求不高,结构简单,因此可以实现更高的集成密度,为忆阻器的大规模集成提供了新的研究参考方向。同时,它可以实现更快的开关速度,如果将该新型加法器模型应用于数字逻辑电路、计算机等其他电子相关领域,将产生可观的积极效应。