一种提高PON 系统时间同步精度的硬件架构

刘 畅,姜 超,柯明明

(1.武汉邮电科学研究院,湖北武汉 430074;2.烽火通信科技股份有限公司,湖北武汉 430073)

随着基站向Small Cell 方向发展[1],覆盖密度越来越大,运营商们需要建设低成本、深度覆盖的承载网络。而PON 成本更低、可节约光纤消耗,并且已能满足小基站数据传输需求,PON 成为承载LTE 小基站回传业务的理想之选[2]。PON 系统是纯介质的光网络,网络结构中完全没有有源设备,相比于其他接入网技术,具有设备简单、组网灵活、成本低廉等优点[3],因此,利用现有的低成本、广覆盖的PON 网络实现小基站回传是可行的,实现小基站回传的一个关键点便是要实现时间同步,业界最热门的时间同步协议为IEEE1588v2 协议,1588v2 协议是近些年发展起来的时间同步技术协议,可以实现亚微秒级精度的时间同步[4],精度与当前普遍采用的GPS 方案类似,但与之相比具有成本低廉、维护方便等优点[5]。目前PON 时间同步已经基本实现,但如今4G 全面覆盖,5G 时代即将到来,峰值速率、网络时延、系统容量等性能指标将出现大幅提升[6],时间同步的精度急需提高[7],该文旨在提出一种新的PON 系统硬件架构,以提高时间同步精度。

1 时间同步的过程

1.1 时钟同步和时间同步

PON 系统是一种点到多点的网络结构,由3 个部分组成,分别为光线路终端OLT(Optical Line Terminal)、光网络单元ONU(Optical Network Unit)和无源分光器POS(Passive Optical Splitter)[8],数据流从局端OLT 到光分路器,再到各个ONU。实际工程中,将PON 网络看做一个整体,只有每个部分均实现时间同步,整体的时间同步精度才能有保证。

时间同步的前提是时钟同步,时钟同步分为带内时钟同步和带外时钟同步,二者对比如表1 所示。

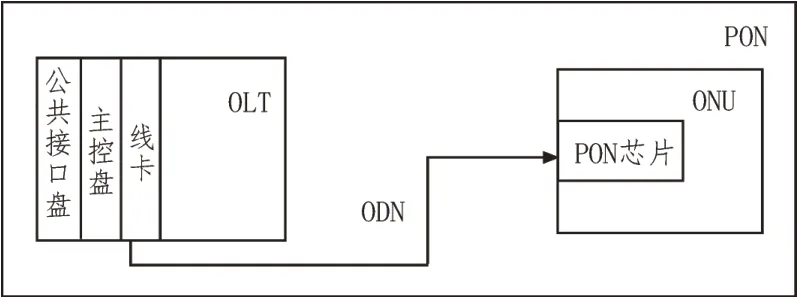

表1 时钟源对比

表2 时间源对比

1.2 时钟/时间同步应用场景

实现高精度时间同步的前提是高精度的时钟同步,目前的1588 时间同步方案主要采用1588 时间+SyncE 时钟的混合同步方式,较为普遍的有以下两种部署方案:

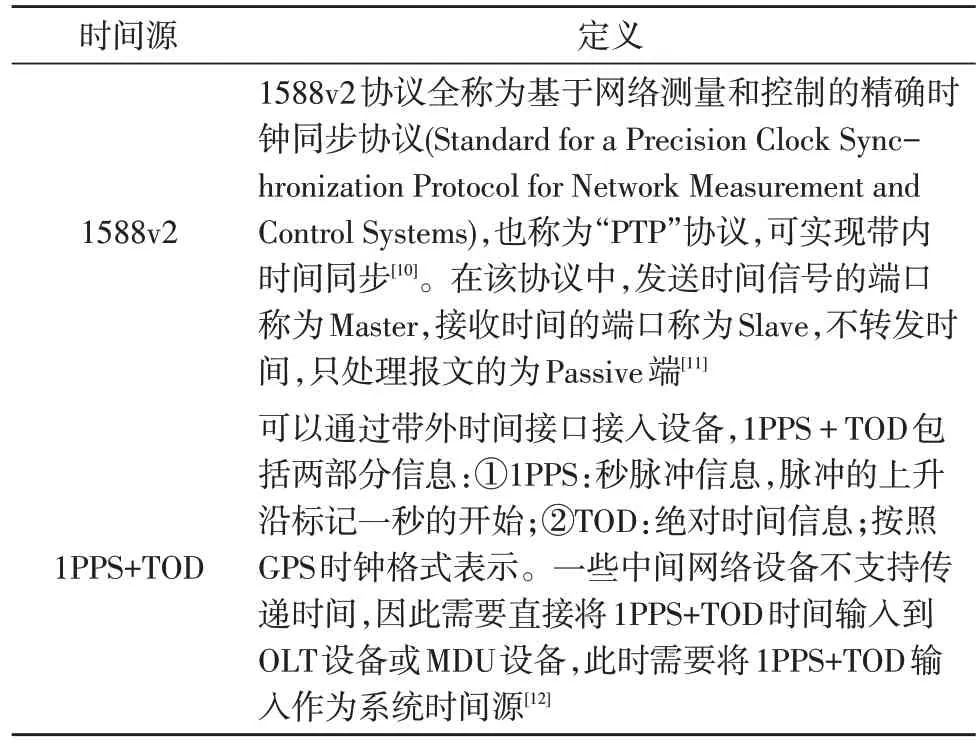

1)全网部署1588v2。无线基站要求时间同步,需要承载网提供时间同步。当承载网设备支持1588v2同步时,时间源从承载网设备注入,如图1所示。

图1 同步应用(全网部署1588v2)

承载网设备通过1PPS+TOD 接口注入同步时间源,作为普通时钟[13(]Ordinary Clock,OC)设备。承载网设备之间通过1588v2 完成时间、时钟同步。OLT+ONU 设备作为一个整体被看作是边界时钟(Boundary Clock,BC)设备,OLT 通过GE/10GE 上行链路输入1588v2 时间,ONU 设备通过用户侧GE 链路向下游设备输出1588v2 时间。OLT 设备和ONU设备之间,PON 时间传递以OMCI(ONU Management and Control Interface)方式下发。

基站作为OC 设备时,若不支持1588v2 同步,使用1PPS+TOD 接口输入时间同步源,使用SyncE 完成时钟同步;若支持1588v2 同步,使用1588v2 完成时间、时钟同步。

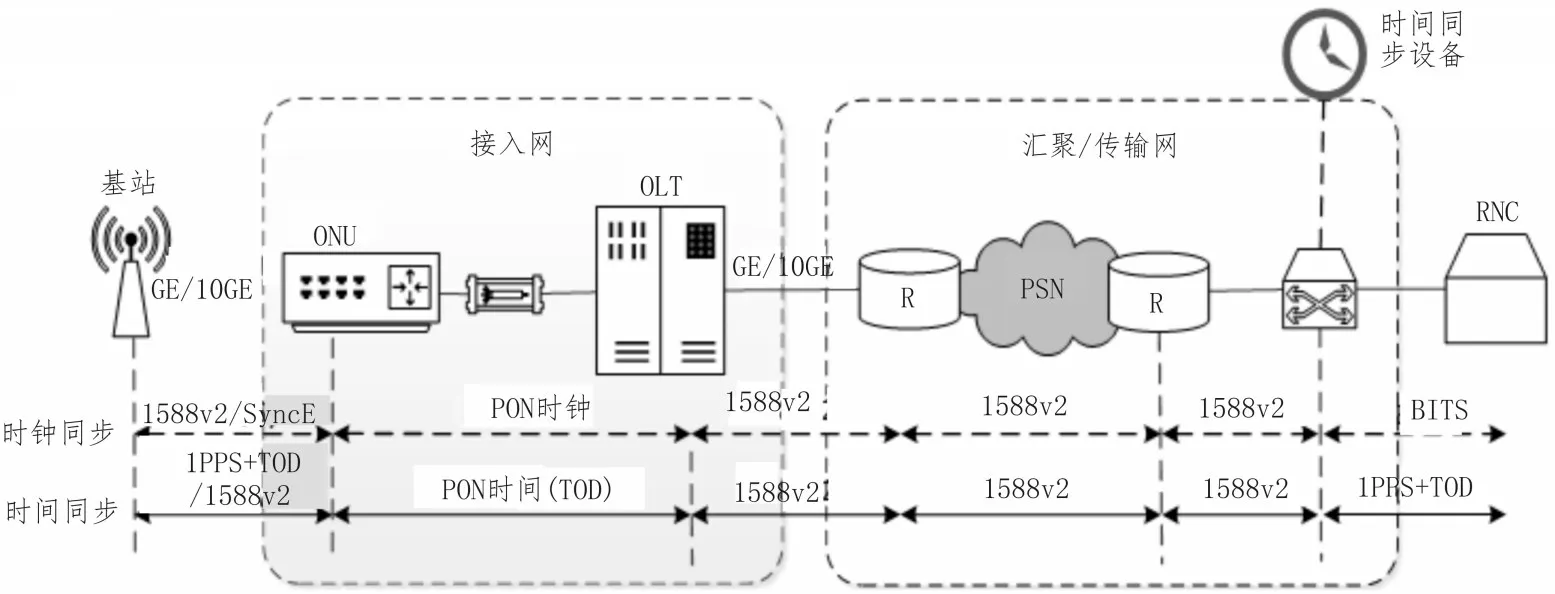

2)OLT 注入时钟源/时间源。无线LTE 基站要求时间同步,当承载网设备不支持1588v2 同步时,时间源从OLT 设备注入。其余与第一种部署相同,不再赘述。如图2 所示。

图2 同步应用(OLT注入时钟源/时间源)

2 新的硬件架构

2.1 总体设计思路

网络的迅速发展对小基站时间同步精度提出了更高的要求,以前采用的旧方案是时间盘[14]方案,即独立一个盘专门同步时钟,通过时间盘和控制盘之间的报文交互来同步时钟,但有报文拥塞的可能性,且步骤繁琐,影响同步精度,已经不能满足5G 时代的要求。因此,针对时间盘方案的弊端,笔者提出了如下几点优化思路:

1)将时钟模块内置于控制盘,通过FPGA 与时钟芯片的相互配合同步时钟,减少不必要的报文交互,提升时钟同步精度,进而可以提升时间同步精度。

2)OLT 不再使用CPU 带内方式与ONU 传递时间时钟,而是通过PON 物理线路连接,这种硬件上的走线更能提升性能。

斗室内,冼星海正全神贯注修改《在太行山上》曲谱,未发觉有人到访。一曲终了,郭沫若捅了捅冼星海后背:“星海,周副主席看你来了。”他让冼星海先试唱一遍,说:“我和周公当你的第一个听众”。冼星海说:“这是一首二部合唱,需要有一个人和我配合。”周恩来便说:“你唱主旋律,我唱第二声部,如何?”冼星海兴奋地说:“好!”浑厚而激昂的歌声在小屋里回荡。合唱完后,周、郭当场拍板,确定《在太行山上》在武汉纪念抗战一周年歌咏大会上演唱。1938年7月,武汉歌咏大会盛况空前。这首歌由张曙、林路、赵启海等在大会上唱出,迅速传遍大后方及各敌后抗日根据地。

3)上联盘为主控盘端口的拓展,提取带内时钟步骤繁琐,若直接将上联端口的物理线路通过背板走线直接连接到主控盘上,可提升同步时间能力。

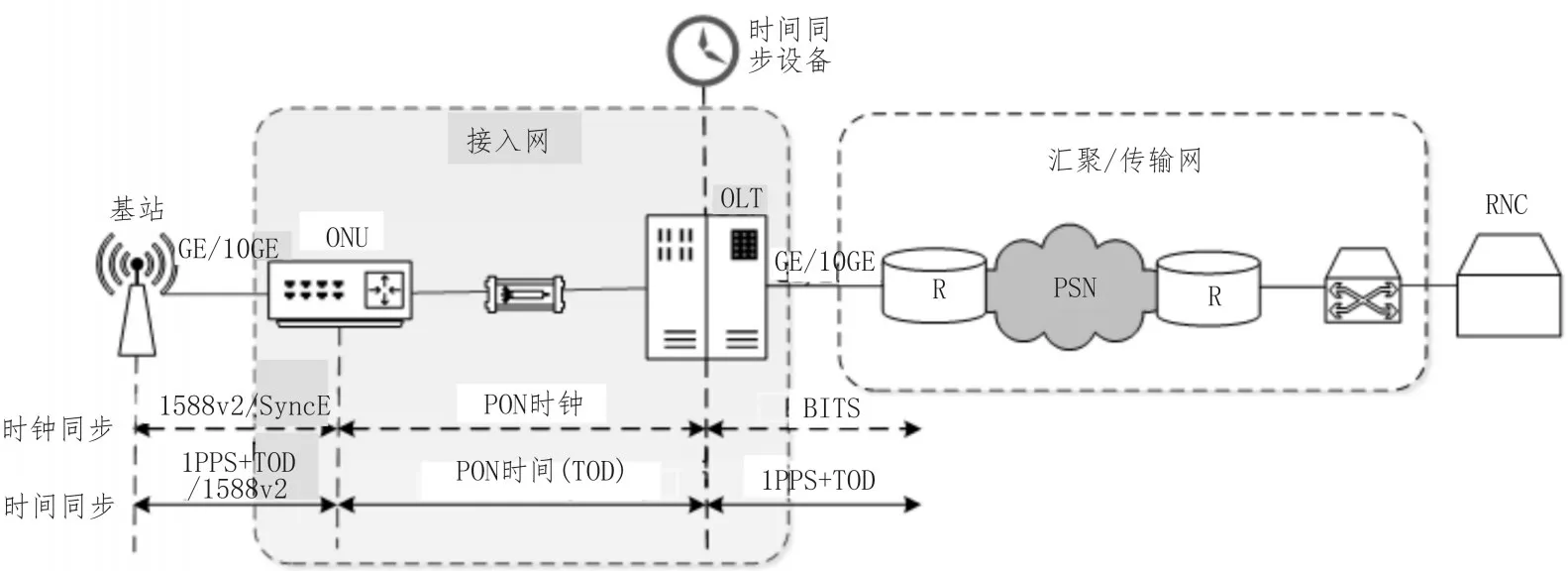

根据以上思路,该方案重新设计了硬件架构。取消时间盘,加入了公共接口盘,以提供2M 带外时钟接口及1PPS+TOD 带外时间接口,如图3 所示。

图3 PON系统结构

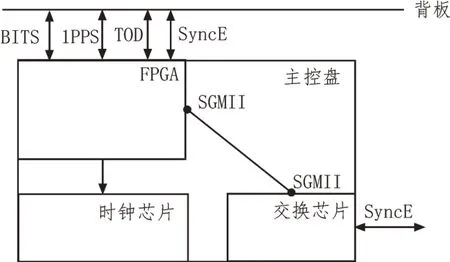

设计的关键在于主控盘内部模块,新方案采用以FPGA 为主导,时钟芯片、交换芯片、CPU 相配合的方式替代时间盘。设计框图如图4 所示。

图4 主控盘设计

2.2 各模块功能

在新方案中,主控盘的关键模块功能如下:

FPGA 模块:FPGA 支持通过BMU 本地总线接口访问模块内部寄存器,实现以太网接口的1588 协议传输,能处理Sync、Delay_Req、Delay_Resp、Announce和Signaling 5 种报文,还支持VLAN、以太网和IP 等6种报文封装格式。也可配置Sync 报文的发送周期,上限为每秒256 次,下限为2 秒1 次。FPGA 根据软件配置自行维护所有报文的收发,收方向需向BMU上报完整的Announce 报文(34 字节帧头和30 字节载荷)和T1、T2、T3、T4 时戳以及CF 域[15]。

1588 协议传输需要的所有时戳由FPGA 自行维护。各个通道支持主从模式选择、单播组播模式选择。各通道可配参数,保障各通道可工作于不同模式,最多支持128 个通道。各个通道支持PTP 报文发送使能控制功能。实现对所有通道的收发PTP 帧内容监测和性能统计。各个通道支持静态时延补偿功能。支持主备工作状态使能控制。

时钟芯片模块:时钟芯片模块包含多个数字锁相环[16],起锁定信号的作用。数字锁相环一般由数字鉴相器、数字环路滤波器、数字压控振荡器三部分组成,如果本振信号的频率和输入信号的频率完全一致,两者的相位差将保持某一个恒定值,则数字鉴相器的输出将是一个恒定直流电压(忽略高频分量),数字环路滤波器的输出也是一个直流电压,DCO的频率将停止变化,这时,环路处于锁定状态。

CPU 模块:主要负责选源。

在各模块的配合之下,实现时钟同步和时间同步的流程如下:

1)时钟同步:BITS 时钟信号输入时,FPGA 将时钟信号分频为8K 时钟信号,SyncE 信号输入时,主控的交换芯片通过SGMII 将信号发送给FPGA,FPGA将其分频为8K 时钟信号,再从所有的8K 时钟信号中选择一路作为时钟芯片的备选参考时钟源。时钟芯片锁定后再发送给FPGA,由FPGA 送往背板。

2)1588v2 时间同步:FPGA 模块具有控制PTP 报文产生、处理单元以完成PTP 报文收发,协议处理,最优时间源(Best Master Clock,BMC)算法实现等功能。通道读取PTP ANNOUNCE 报文,根据1588v2 协议从报文中提取PTP 时间源信息,保存到本地。收发包通道:上游设备端口<->上联口<->主控交换芯片<->FPGA。PTP 通过在主从时钟间交互报文精确测量线路时延和主从时钟间的偏差值,以实现时间同步。

3)1PPS+TOD 时间同步:FPGA 接收来自背板的1PPS+TOD 信号,完成1PPS+TOD 信号的接收和存储,并对1PPS 信号提供输入时延补偿功能,将补偿后的1PPS 信号输出提供给时钟芯片进行时间同步。时钟芯片同步1PPS 信号后发送给FPGA,FPGA按中国移动TD TOD 协议规范组成TOD 帧,在下一个PPS 上升沿之后发送出去,生成发往背板的1PPS+TOD 信号。

3 实验验证

3.1 测试环境

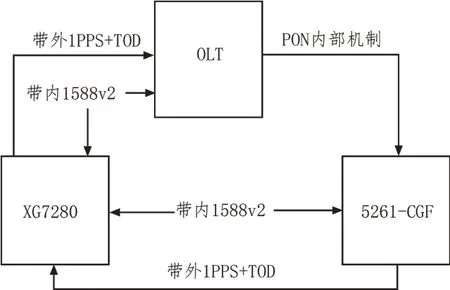

测试中使用的OLT 是烽火通信的AN6000-17 系列,主控盘为HSCA,上联盘为HU8A,线卡为GNOA,ONU 型号为5261-CGF,测试仪表为夏光XG7280 时频同步分析仪。测试组网如图5 所示。

图5 测试组网

3.2 实验过程及结果

实验分为4 种情况:2 MBITS 时钟测试、SyncE 时钟测试、1PPS+TOD 时间测试和1588v2 时间测试。由于时钟同步是为时间同步服务的,最后的目的还是时间同步,因此这里只展示最后的时间同步的测试结果。

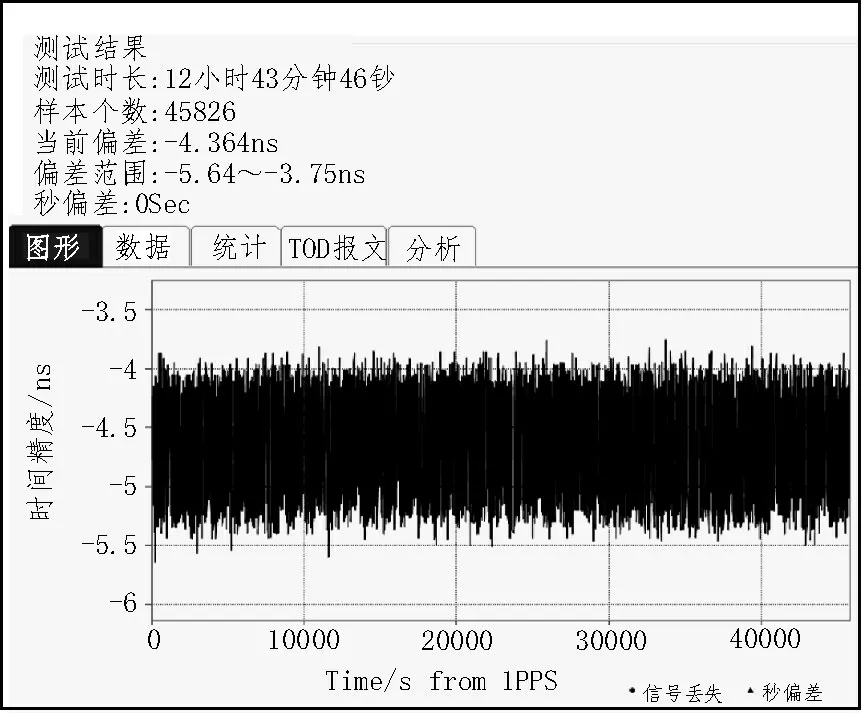

1)1PPS+TOD 为纯物理线路,主要的误差来源于线缆造成的延时,该延时可以通过计算消除,不会影响抖动范围。该次测试时间约为12 小时,总体抖动在5 ns 内,多次测试抖动在20 ns 内,时间同步精度较高,结果如图6 所示。

图6 1PPS+TOD长时测试结果

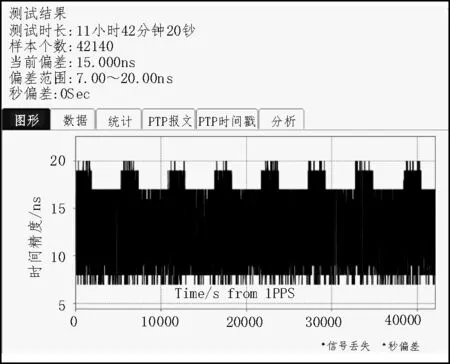

2)采用1588v2 时间同步,误差由三部分引入:①上下行波长不同,上行波长为1 310 ns,下行为1 490 ns,在最大物理距离为20 km的情况下,产生的误差约为17 ns,可通过计算从而进行补偿;②serdes 串并转换引入的误差,GPON的下行速率为2.488 Gbit/s,误差约为±6.4 ns,该误差消除较为困难;③测距引入的误差,该误差容易补偿,但GPON 在单向时延上引入的最大误差为±1.6 ns,暂时无法进行补偿,所以,在补偿都实现的情况下,精度可以达到±1.6 ns;若不做任何补偿,精度应在±25 ns 以内。该次测试口为10G 光口,测试时长约为12 小时,抖动范围为0~15 ns,多次测试抖动在20 ns 内,对比以前时间盘1588v2 方案(偏差±40 ns)有了明显的提升,结果如图7 所示。

图7 1588v2长时测试结果

4 结论

通过上述测试结果可以看出,PON 系统的时间同步精度得到了很大提升,1588v2 和1PPS+TOD 时间同步精度均在20 ns 以内,这种全新的硬件架构以FPGA 为主导,采用时钟模块置于控制盘内,PON 物理线路连接等创新性设计,解决了目前时间同步精度低的问题,能够接受即将到来的5G 时代的挑战。另外,该方案长时测试的稳定性也很强,具有很高的应用价值,可以大规模商用。