“VLSI物理设计”科教融合教学方法探索

李金城

(北京交通大学 电子信息工程学院,北京100044)

0 引言

集成电路产业是信息技术产业的核心,是支撑经济社会发展和保障国家安全的战略性、基础性和先导性产业[1]。我国集成电路设计人才严重短缺,加强集成电路人才培养是促进我国集成电路产业持续发展的重要任务,受到全社会的共同关注[2~4]。

研究生培养是集成电路设计人才培养的重要阶段,按照教育部《关于全面提高高等教育质量的若干意见》和《高等学校创新能力提升计划》的部署和要求,集成电路研究生人才培养也要不断探索科教融合的途径与方法,为我国集成电路产业发展培养急需的创新型人才[5~6]。

“VLSI物理设计”是我校集成电路设计专业方向研究生的核心课程,通过理论教学和实践训练两方面入手,加强研究生集成电路设计能力的培养,要求课程必须具有很强的实践性和系统性。

为了提高课程教学质量,并结合“VLSI物理设计”课程的教学内容和课程特点,本课程在教学过程中引入了卫星授时芯片设计项目,把项目的研发方案、设计流程和科研成果等转化为教学案例,对科教融合的课程教学方法进行有益的尝试和探索。

1 “VLSI物理设计”课程说明

由于本科阶段,集成电路理论和集成电路设计流程方面的教学相对薄弱,学生尤其对集成电路设计流程中相关的原理和方法理解不够到位,所以需要在研究生阶段开设“VLSI物理设计”课程进行必要的完善和补充。

课程的集成电路设计流程教学内容由模拟和数字两条主线构成,其中模拟集成电路设计流程是从原理图到版图,数字集成电路是从Verilog到版图。由于课程只关注设计流程本身,所以电路原理、参数计算和Verilog代码设计等内容则不属于本课程的教学范围。

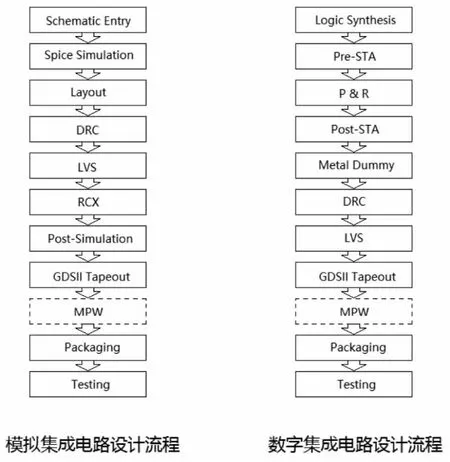

如图1所示,模拟集成电路设计流程包括原理图输入(Schematic Entry)、Spice仿真(Spice Simulation)、版图设计(Layout)、设计规则检查(DRC)、版图与原理图比对(LVS)、寄生参数提取(RCX)、后仿真(Post-Simulation)、GDSII交付流片(GDSII Tapeout)、MPW制造(多项目晶圆)、封装(Packaging)和测试(Testing)。

图1 课程集成电路设计流程框图

数字集成电路设计流程包括逻辑综合(Logic Synthesis)、前时序分析(Pre-STA)、自动布局布线(P&R)、后时序分析(Post-STA)、添加金属(Metal Dummy)、设计规则检查(DRC)、版图与原理图比对(LVS)、GDSII交付流片(GDSII Tapeout)、MPW制造(多项目晶圆)、封装(Packaging)和测试(Testing)。

为保证实践教学质量,本课程不仅制作了实验手册,而且还搭建了完整的EDA软件平台,准备了配套的PDK、标准单元库和Verilog源代码等数据文件,使学生能够顺利完成模拟集成电路和数字集成电路全流程的设计实验。

课程分配了一定的课堂学时讲解集成电路设计流程的原理与方法,使学生对设计实验过程中的参数设置方法、脚本命令格式和指令预期结果等做到心中有数,减少实验操作的盲目性,再结合科教融合案例对课堂内容进行比对、分析和扩展,以提高学生分析和解决实际问题的能力。

2 课程案例项目简介

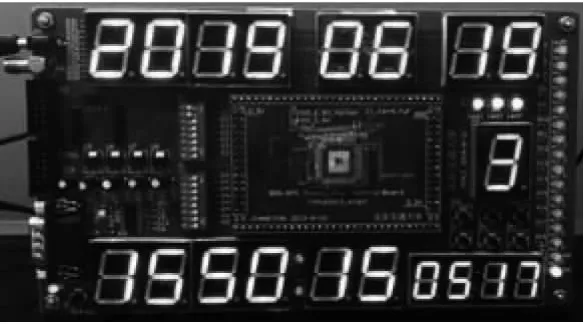

引入课堂的案例项目是一款BDS/GPS兼容的卫星授时芯片设计项目,主要应用与日常计时,要求授时精度优于20 ms,能够输出年月日时分秒星期及农历等信息,并提供数码管扫描和UART输出。

BDS与GPS都是每6秒播发一帧导航电文,并在导航电文中提供每帧播发的起始时刻[7~8]。因此,本项目卫星授时的方案是捕获跟踪卫星信号,解调导航电文,从电文中提取当前帧的播发时刻并对其进行传输延时修正,最后转换成格林威治时间实现卫星授时。

需要说明,由于卫星到接收机的信号传输延时在70 ms到90 ms之间,精确的延时计算需要定位。本项目芯片不定位,按80 ms估算延时用于授时修正,虽然有10 ms左右的误差,但仍然能满足项目指标要求的优于20 ms的授时精度。

图2为本项目芯片的电路结构图,电路由卫星信号捕获模块(AC)、卫星信号跟踪模块(TC)和格林威治时间转换模块(UTC)、4块双端口SRAM(DPSRAM-0、1、2、3)和1个3.3 V转1.8 V的LDO模块构成。输入为BDS和GPS的中频采样信号,输出为数码管扫描和串口,以及控制射频芯片工作模式的SPI接口。

图2 案例芯片的电路结构图

案例项目的研发流程是首先确定兼容BDS和GPS的卫星信号捕获跟踪算法、格林威治时间的转换方案和数据输出格式,然后设计Verilog代码,制作FPGA样机,实测算法性能和授时精度等指标,最后进行ASIC设计实现。

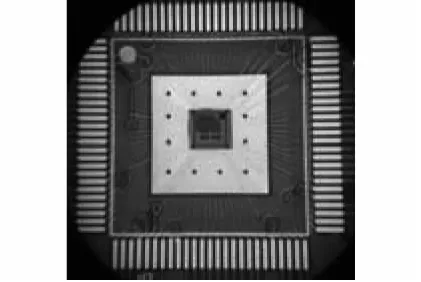

案例芯片采用SMIC 0.18 um CMOS工艺设计实现,首先准备好PDK、标准单元库、Memory Compiler和LDO IP,然后按照图1的设计流程得到GDSII版图,进行MPW流片和COB(Chip on Board)封装,制作测试样机。最后经样机测试,芯片一切功能正常,流片取得成功,裸芯面积为2.2x2.2 mm2。

3 科教融合教学实践

案例项目是一个典型的数字集成电路设计项目,其中从Verilog到Layout的主要设计步骤都包含在“VLSI物理设计”课程中,与课程内容具有很好的对应关系,而且项目研发所使用的EDA软件平台、PDK和标准单元库等也与课程实验的一致,因此非常适合作为教学案例引入到课堂教学中。本课程的科教融合教学实践主要包括以下几个方面:

1)整理项目成果,制作PPT课件

把项目内容制作成PPT课件,穿插在课堂教学中进行讲解和说明,是本课程科教融合教学实践的重要工作之一,作为项目展示的主要载体,课件包括项目代码结构、源码分析、设计流程、流片、封装、测试和改进展望等内容,在科教融合的教学实践中发挥着关键作用,图3所示为项目PPT课件的封面页。

图3 项目PPT封面页

2)梳理项目流程,比对课堂内容

虽然案例芯片的设计流程与课堂教学的设计流程基本相同,但是课程教学比较基础,通过项目与课程的比对,不仅可以加深对课堂内容的理解,而且还能对一些工程实际问题建立感性认识,明确课堂所学与实际所需的差距,为今后的深入学习指明方向。

在教学中只要遇到与项目案例相关内容就会进行比对,虽然案例项目属于数字集成电路设计项目,需要比对的内容也主要集中在数字部分,但是由于数字集成电路的版图也需要DRC和LVS,所以在讲完模拟集成电路DRC和LVS时,也会结合案例讲解如何对数字集成电路的版图进行DRC和LVS,使学生明白数字集成电路版图最终也要导入到模拟环境中进行处理和验证。

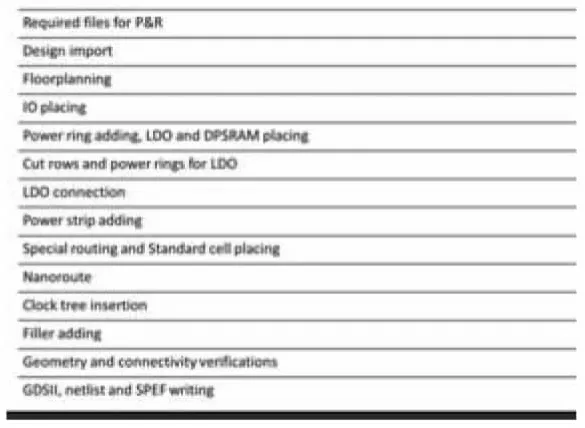

图4和图5分别为课程和项目的关于自动布局布线(P&R)部分的PPT目录页(图5进行了局部放大处理),虽然它们都是从网表到版图的设计,但案例项目流程中增加了放置I/O、DPSRAM和LDO,以及连接LDO的步骤,通过课堂比对和说明,使学生了解如何摆放和连接模拟IP模块,为设计较为复杂的芯片打下一定的基础。课程中比对的内容还有很多,这里就不再一一介绍了。

图4 自动布局布线(课程PPT)

图5 自动布局布线(项目PPT)

3)扩展教学内容,增加深度广度

除了前面的比对教学外,课程还对案例芯片的电源供电方法、时钟门控(clock gating)方案、Pad选型与规划、DPSRAM生成与连接、DFT策略与扫描链设置、形式验证流程、金属密度添加、天线效应消除、流片数据提交和芯片封装测试等问题进行了扩展讨论。

例如,如图6所示为芯片COB封装打线示意图,这是按照COB封装厂家要求提供的高分辨率裸芯Pad管脚与PCB焊盘连接关系的示意图,同时厂家还要求PCB板做沉金处理。在课堂上对案例芯片的COB封装进行扩展讨论,使学生对COB封装和PCB沉金有了一定的了解,今后若遇到COB封装问题时,也知道大致的解决方案。

图6 案例芯片COB封装接线示意图

由此可见,通过案例扩展教学内容,不仅可以增加课程的深度和广度,而且还能提高课程的实用性。

4)实物视频展示,激发学习热情

在课程教学内容全部完成后,将项目芯片、样机和测试视频等带进课堂进行展示和播放,让学生零距离接触项目成果,观察卫星授时样机的工作过程,体会将代码变成芯片的实际过程,用成功案例激发学习热情,树立学习信心。图7和图8分别为课程展示的COB显微照片和芯片测试样机。

图7 COB显微照片

图8 芯片测试样机

5)回顾项目经历,培养科学精神

项目工作日志记录了从确定算法方案到流片测试成功的整个研发过程,每天的项目进度、问题难点、解决方案、成功经验与失败教训等等都写在日志文档中。在课堂上与同学们分享日志中的酸甜苦辣,不仅能使同学们学习到成功的经验,吸取失败的教训,而且还能培养坚忍不拔的意志品质和严谨认真的科学精神。

4 结语

本文介绍了“VLSI物理设计”课程的科教融合教学实践方法,教学中采用多种形式把科研成果转化为课程教学内容,不仅促进了科研与教学之间的良性互动,而且还丰富了课程教学资源,提高了教学质量,在连续两届研究生课程的教学实践中取得了一定的成果,今后还将继续改进和提高,在科教融合的教学实践中不断探索前进。