一种带有DAC失配整形的高精度Sigma-Delta调制器*

刘铭扬 ,王小松 ,刘 昱

(1.中国科学院微电子研究所,北京 100029;2.中国科学院大学,北京 100049;3.新一代通信射频芯片技术北京市重点实验室,北京 100029)

0 引言

由仪表放大器、抗混叠滤波器和模数转换器组成的模拟前端(Analog Front End,AFE)是可穿戴医疗设备中信息采集系统的重要组成部分[1]。实际信息采集过程中,外界环境中的非理想因素及皮肤与电极接触带来的可变动阻抗使仪表放大器得到的信号幅度变动极大,且存在很大的基线漂移[2]。面对这样一个频带窄、动态范围大的待处理信号,ADC 模块必须满足高动态范围、低失真的特性,以降低仪表放大器和后端数字处理单元的设计难度,保证信号的采集质量。

相较于流水线型(Pipelined)、逐次逼近型(SAR)、全并行型(Flash)等奈奎斯特采样率型ADC[3-4],采用过采样技术和噪声整形技术的Sigma-Delta 型ADC 更容易满足上述低失真、低功耗、高精度的需求[3]。Silva 等人提出一种全前馈结构,前馈支路直接连接到量化器的输入端[4],可以有效缩减积分器的输出摆幅,降低OTA的设计难度。

本文面向生理信号采集应用,对文献[4]中的全前馈结构进行了优化,设计了一种带前馈支路的三阶五比特高精度Sigma-Delta调制器,并引入二阶动态元件匹配算法,以解决多比特量化引入的电容阵列非线性问题。

1 Sigma-Delta调制器的结构选择

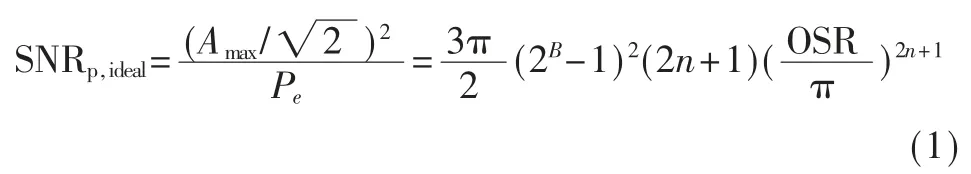

对于一个n 阶的Sigma-Delta调制器,若采用B 位量化,其理想峰值信噪比可表示为:

其中,过采样率OSR=fs/2fb。根据式(1),提高量化器位数B、环路阶数n 和过采样率OSR 皆可提高调制器的信噪比。但过度提高环路阶数n,会造成环路不稳定,且会增加了OTA的设计难度。提高量化器位数,会引入多比特的DAC 电容阵列,造成电路的非线性失真。过度提高OSR,会大大增加调制器的功耗[5]。

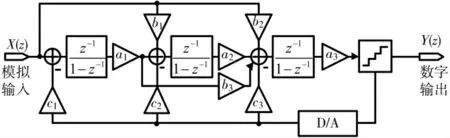

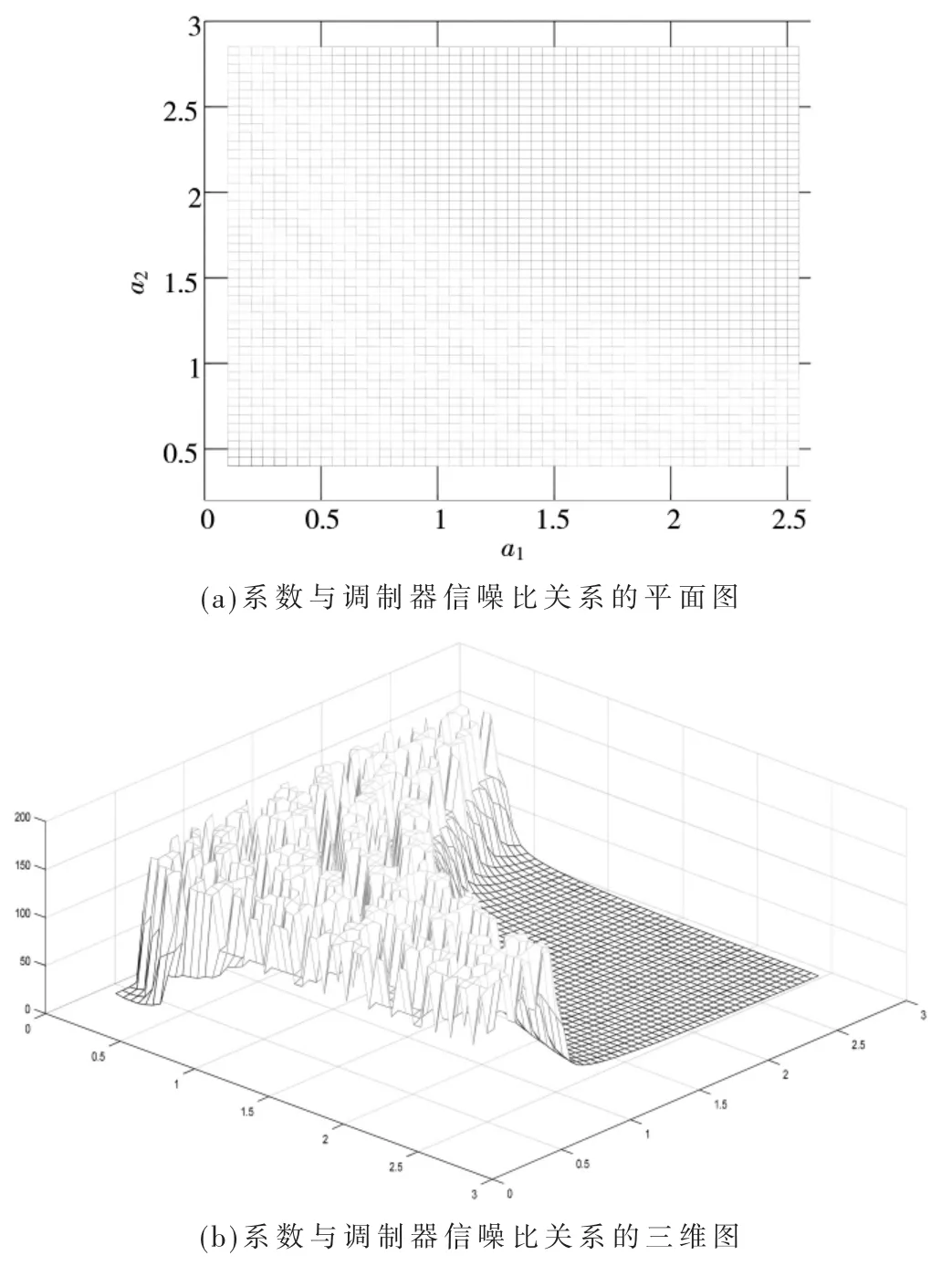

经折衷考量,本文的调制器采用图1 所示的三阶五比特全前馈等效结构,OSR=64,采样时钟为1 MHz。

图1 全前馈的Sigma-delta调制器的等效结构

令调制器的噪声传递函数达到理想的高通形式(1-z-1)3,推导调制器系数间的关系得:

选取a3=0.6、b3=1,在[0.1,2.55]、[0.4,2.85]的区间内扫描调制器系数a1a2与调制器信噪比间的关系,可绘制结果如图2 所示。在期望指标的范围内选择调制器系数a1=1.3,a2=1,a3=0.6,并在综合考虑开关非线性、热噪声、积分器增益、摆幅、压摆率、带宽等非理想因素后,使用MATLAB 对调制器进行行为级建模,仿真结果如图3所示。三级积分器输出摆幅如图4 所示,调制器的最大SNDR 为108 dB,有效位数接近18 bit。

图2 调制器系数与调制器信噪比间的关系

图3 行为级仿真结果

由图4 可知,前馈结构将第一二级积分器的输出摆幅控制在一个极小的范围内,大大降低了OTA 直流增益对调制器性能的影响。

图4 三级积分器输出摆幅

2 Sigma-Delta调制器的电路实现

2.1 总体结构实现

由式(2)、式(3)计算得出调制器的系数实现方案如表1 所示。

表1 调制器系数实现

选取第一级单位电容c1为200 fF,第二、三级单位电容c2、c3为50 fF,其总体电路结构如图5 所示。由于第一、二级积分器输出摆幅很低,对OTA的带宽和增益需求也得到降低,固选用简单的A 类运放进行设计;反馈DAC的参考电压设置为1.8 V 和0 V,以避免对额外电压产生电路的设计需求;5 bit 量化器采用异步逻辑的逐次逼近型量化器,以降低静态功耗、减小硬件开销和整体面积;第一级采样开关使用0.33 μm 沟道长度的MOS 管搭建CMOS 开关,加大MOS 管尺寸为64/0.33 μm,以减小管子的导通阻抗,同时避免开关导通电阻阻抗随输入信号幅度变化而引发的非线性失真;所有开关皆由两相不交叠时钟控制,Φ1相为采样相,Φ2相为积分相,以避免沟道电荷注入引发误差。

图5 调制器的整体电路实现

2.2 跨导放大器的设计

在设计中选用单极电流镜型结构的OTA 进行积分器的搭建,其结构如图6 所示,该结构引入一对交叉耦合的MOS 管构成正反馈,以提高增益和GBW。

图6 前两级OTA 结构

瞬态仿真下,积分器的输出波形如图7 所示,积分器的输出摆幅很小,稳定在共模电压附近,且在Φ1相和Φ2相皆可建立完全。

图7 第一级积分器的建立

2.3 5 bit 量化器的设计

采用动态逻辑可尽量减少高频翻转节点,以实现低功耗设计,固选择带异步复位的高速TSPC 触发器构成的寄存器链来产生异步SAR 逻辑。在Φ2相DAC 对第三级积分器的输出进行采样,而在Φ1相比较器的时钟控制信号CLK 由GATE 信号控制环振电路产生,同时,CLK控制比较器产生比较结果Q 和QB,也控制TSPC 触发器产生顺序控制信号S,继而使顺序选通信号SC 在时钟信号到来前翻转为高电平,以将锁存住的比较结果更快地反馈给DAC,其整体结构如图8 所示。在设计中需保证时钟信号产生环路的延时Tr大于比较器的复位时间。

图8 采用TSPC 逻辑构成的异步SAR 量化器

比较器采用低功耗动态比较器,其结构如图9 所示。CLK 为低电平时,比较器处于复位态,P、N 被充电至VDD;CLK 为高电平时,INP与INN 间的压差传导至锁存器,输出比较结果Q与QB。

图9 低功耗动态比较器

2.4 两阶动态元件匹配算法

量化器输出的5 bit 二进制码流转换为31 bit 温度计码。设反馈电容阵列的理想单位值是Caverage,出现失配的实际值为ci,电容阵列的失配误差传递函数为NTF(z)。定义指针p(z),在循环移位中,指针永远指向最后一个选通电容的下一位,而当前时间选通的电容个数为n(z),则DAC的输出可以表示为[6]:

构建DAC失配误差整形函数NTF(z),使NTF(z)有二阶高通形式(1-z-1)2,展开可得β0、β1、β2分别为1,-2,1。由此推导出指针p(k)的时域表达式为:

其中p(k)、p(k-1)、p(k-2)分别表示k+1、k、k-1 时刻的电容阵列的起始位置,当指针溢出31 位,令Sovfl(k)=0。

二阶动态元件匹配的移位示意图如图10 所示,算法逻辑框图如图11 所示。

图10 二阶DWA 移位示意图

图11 二阶DWA 算法逻辑框图

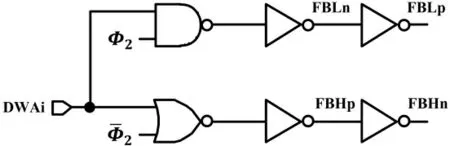

经由DWA 输出的加权平均码在Φ2相通过图12的控制逻辑产生反馈DAC的开关控制信号。

图12 反馈开关控制信号

3 仿真结果

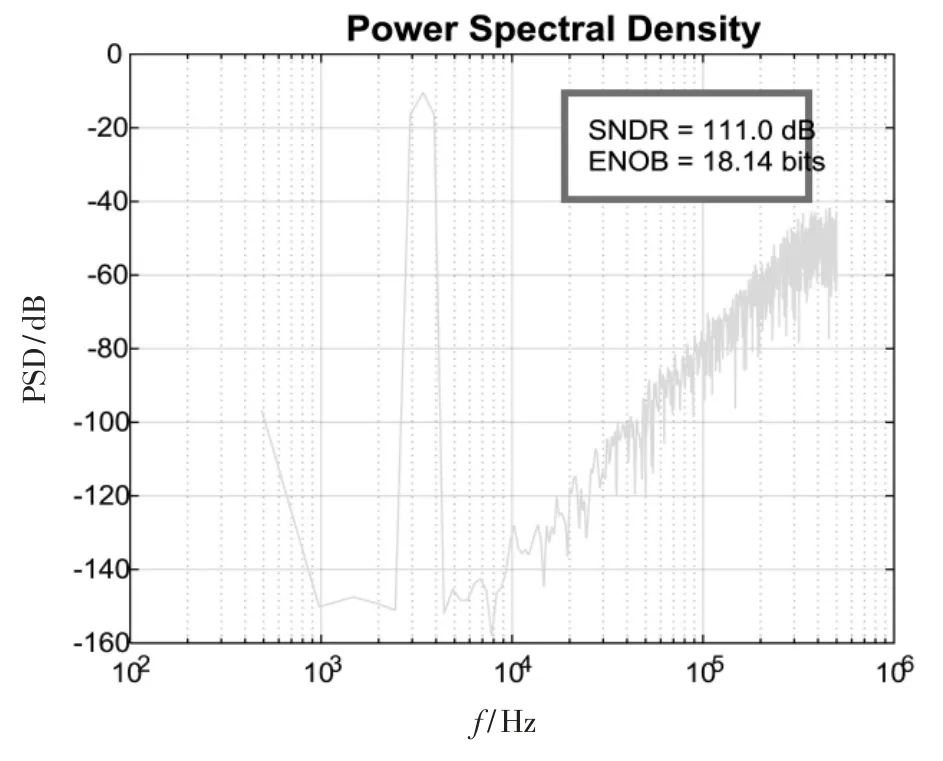

本文设计的带前馈结构的高精度多比特Sigma-Delta调制器使用SMIC0.18 μm的CMOS 标准工艺,电源电压为1.8 V,在1 MHz 采样率下,为加快仿真速度,保证OSR不变,调整相干采样点数,略微增大信号带宽,输入幅度为-10.4dBFS@3.41 kHz的信号,最终仿真得到信号噪声失真比(SNDR)为110 dB,有效位数(ENOB)为18 bit,输出频谱图如图13 所示。由于谐波失真很小,SNR 曲线与SNDR 曲线近似重合,可用SNDR 曲线计算调制器动态范围,动态范围测量曲线如图14 所示,动态范围(DR)约为120 dB。其功耗约为0.87 mW。

图13 调制器输出功率谱密度

图14 调制器动态范围曲线

FOM 值(Figure-of-Merit)综合考虑了ADC的精度、功耗和速度,是更为全面的性能指标,采用式(7)可计算出本结构的FOM 值为3.01 pJ/step,与其他已发表的同类Sigma-Delta调制器性能对比如表2 所示。由表2 可知,本文中的调制器综合性能更优。

表2 本文与其他已发表论文的性能比较

4 结论

本文设计的面向生理信号采集应用的Sigma-Delta调制器采用全前馈等效结构,减小调制器的输入输出信号幅度,大大降低了对OTA的直流增益和摆幅要求;在不过度增加OSR的前提条件下,增加量化器量化位数来提高调制器精度,并采用基于异步逻辑的逐次逼近型ADC 来实现五比特量化;最终采用二阶动态元件匹配算法来解决多比特量化引入的DAC 非线性失真问题。仿真结果表明,Sigma-Delta调制器信噪失真比(SNDR)为111 dB,动态范围(DR)为120 dB,有效位数为18 bit,整体功耗为0.87 mW,满足了生理信号采集应用中对ADC高精度、高动态范围的设计需要。