与Y2O3共同掺杂下Sb2O5掺杂量对SnO2陶瓷压敏电阻电性能的影响

郁培源,赵洪峰

(新疆大学电气工程学院,电力系统及大型发电设备安全控制和仿真国家重点实验室,乌鲁木齐 830046)

0 引 言

压敏电阻是一类半导体器件,具有非线性的电流-电压特性,能够迅速、反复地检测和限制瞬态浪涌,从而避免电路和电力系统遭到破坏[1]。ZnO、SrTiO3、TiO2以及SnO2等半导体陶瓷[2-3]常应用于压敏电阻中。其中SnO2陶瓷的微观结构简单,电流-电压曲线的非线性度高,金属氧化物的掺杂量少,抗降解性能高,有效势垒的数量多以及热导率高,是制备高性能压敏电阻的理想材料;同时高性能SnO2陶瓷压敏电阻的制造成本低,内部结构简单,对电力系统的安全和稳定运行起到重要作用。

残压为放电电流流过时避雷器两端的峰值电压,当残压超过并联在避雷器两端的用电设备的额定电压时,会导致用电设备损坏,引起大面积停电,甚至对操作人员的安全造成威胁。残压与晶粒电阻有关,晶粒电阻越大,残压越大。研究[4]表明,在SnO2陶瓷压敏电阻中掺杂钇时,晶粒间会形成阻碍晶粒生长的小颗粒,从而使得SnO2陶瓷压敏电阻的电压梯度增大,有利于减小避雷器尺寸,但晶粒电阻仍较高。据报道,在SnO2压敏电阻中掺杂钇可以增大电压梯度,掺杂锑可以降低晶粒电阻[5-7]。目前,关于在SnO2压敏电阻中单独掺杂锑和钇的研究较多,共同掺杂锑和钇的报道仍较少,为此,作者通过在SnO2压敏电阻中掺杂Y2O3和不同含量的Sb2O5,研究了锑含量对掺钇SnO2压敏电阻微观形貌和电性能的影响。

1 试样制备与试验方法

试验SnO2压敏电阻的原料组成(物质的量分数,下同)为x%Sb2O5,(98.85-x)%SnO2,1%CoO,0.05%Nb2O5,0.05%Cr2O3,0.05%Y2O3,x分别为0,0.05,0.10,0.15。在去离子水中将原料与聚乙烯醇(PVA)混合后在KQM-Y/B型行星式球磨机中球磨8 h,球料质量比为2…1。球磨后将浆液置于65 ℃的电干燥器中干燥10 h。将干燥后的浆料粉碎后过100目筛得到电阻原料粉,用Y41-25A型25 t单柱校正压装液压机将原料粉压制成直径25 mm、厚度2.5 mm的圆盘,压力为150 MPa。将圆盘置于KSS-1600 ℃型高温节能气氛炉中烧结,加热速率为2 ℃·min-1,烧结温度为1 300 ℃,烧结时间为2 h,冷却速率为5 ℃·min-1。烧结后在圆盘的侧面涂敷银浆,置于200 ℃的烤箱中固化30 min,制备得到SnO2压敏电阻片。

采用Novocontrol Concept 80型宽带介电和阻抗光谱仪测试压敏电阻的电容-电压(C-V)特性,测试频率为1 kHz,同时测试交流阻抗曲线,测试频率为1 Hz20 MHz,温度为250 ℃。采用Keithley Model 2410型源表测试压敏电阻的电流-电压(I-V)特性,换算成电压梯度-电流密度(E-J)特性曲线,换算公式为

J=I/S

(1)

E=V/d

(2)

式中:S为压敏电阻片的面积;d为压敏电阻片的厚度。

采用Hitachi 8010型扫描电子显微镜(SEM)观察压敏电阻的表面微观形貌。采用Model H/max 2500型X射线衍射仪(XRD)测试压敏电阻的物相组成。

2 试验结果与讨论

2.1 SnO2压敏电阻的微观形貌和物相组成

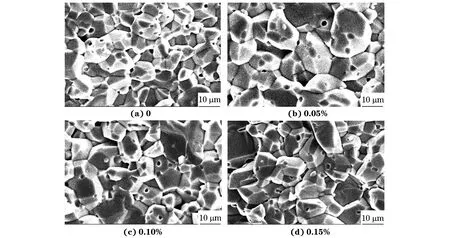

由图1和表1可以看出,Sb2O5掺杂量从0增加到0.15%时,晶粒尺寸先增大后减小,说明少量锑掺杂能够促进晶粒长大,过量锑掺杂则抑制晶粒长大,推测是由于过量的锑引起其偏析,阻碍了晶粒生长。由图2可以看出,不同Sb2O5掺杂量SnO2压敏电阻中除存在SnO2金红石相外,无其他物相存在,这是由于锑和钇的掺杂量较少,其相关衍射峰强度较弱。

图1 不同Sb2O5掺杂量SnO2压敏电阻的SEM形貌Fig.1 SEM morphology of SnO2 piezoresistor with different doping amounts of Sb2O5

表1 不同Sb2O5掺杂量SnO2压敏电阻的晶粒尺寸和电性能参数

图2 不同Sb2O5掺杂量SnO2压敏电阻的XRD谱Fig.2 XRD patterns of SnO2 piezoresistor with differentdoping amounts of Sb2O5

2.2 SnO2压敏电阻的C-V特性

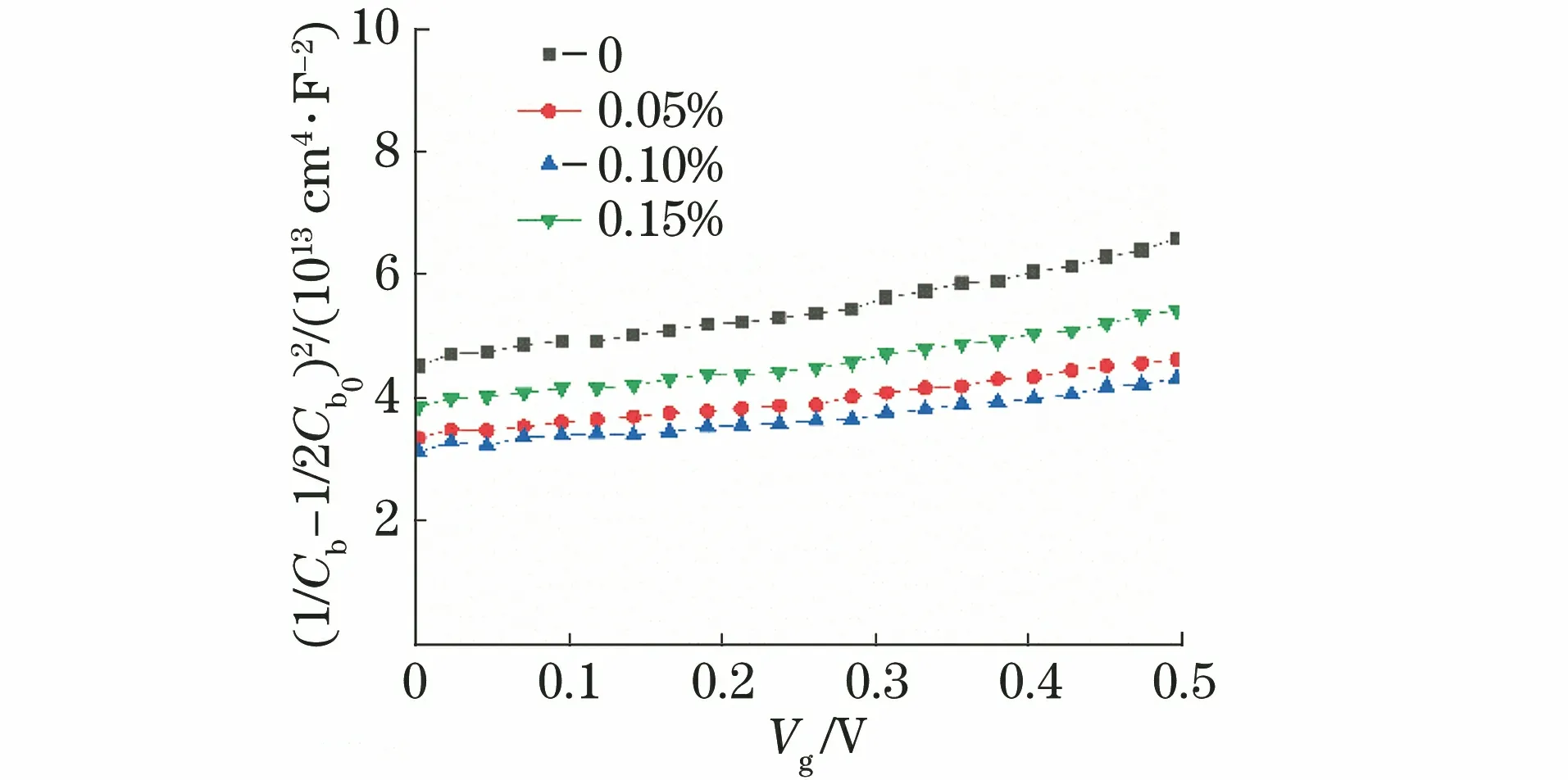

压敏电阻的电压与电容的关系式[8]为

(1/Cb-1/2Cb0)2=2(φb+Vg)/qεrε0Nd

(3)

式中:q为自由电荷;Vg为晶界电压;Cb为单位晶界面积的电容,Cb0为晶界电压为0时的单位晶界面积电容;εr为Sb2O5的相对介电常数;ε0为真空介电常数;Nd为供体密度;φb为晶界处的双肖特基势垒高度。

由式(3)可以看出,供体密度和双肖特基势垒高度分别与(1/Cb-1/2Cb0)2-Vg曲线的斜率和截距有关[9]。

由图3和表1可以看出:Sb2O5掺杂量从0增加到0.10%时,供体密度从2.5×1023m-3增加至4.4×1023m-3,晶界处的双肖特基势垒高度从1.12 eV增加至1.34 eV;随着Sb2O5掺杂量进一步增加,供体密度和晶界处的双肖特基势垒高度均降低,推测这是锑的偏析导致。

图3 不同Sb2O5掺杂量SnO2压敏电阻的C-V曲线Fig.3 C-V curves of SnO2 piezoresistor with differentdoping amouts of Sb2O5

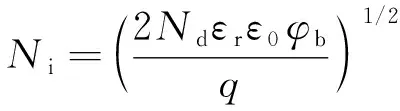

界面态密度Ni的计算公式为

(4)

2.3 SnO2压敏电阻的E-J特性

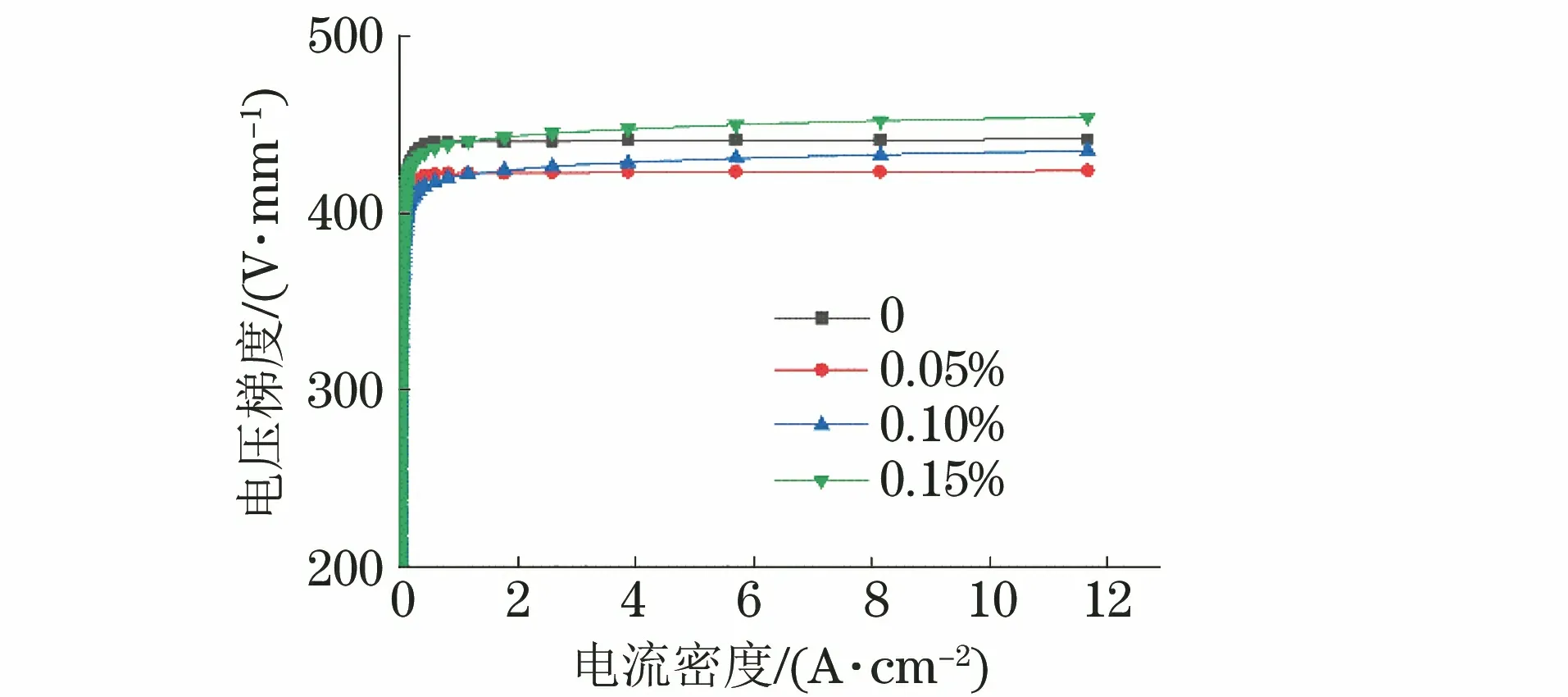

由图4可以看出,Sb2O5掺杂量从0增加至0.05%时,电压梯度从441 V·mm-1减小到423 V·mm-1,表明少量锑的掺杂降低了电压梯度。少量锑掺杂使得SnO2晶粒尺寸增大,单位长度SnO2晶粒数量减少,单位长度的势垒数量减少,导致电压梯度减小。随着Sb2O5掺杂量进一步增加,晶粒尺寸减小,导致电压梯度增大。

图4 不同Sb2O5掺杂量SnO2压敏电阻的E-J特性曲线Fig.4 E-J characteristic curves of SnO2 piezoresistor with differentdoping amounts of Sb2O5

取电流密度J1为1 mA·cm-2,J2为10 mA·cm-2,计算SnO2压敏电阻的非线性系数,表达式为

(5)

式中:α为非线性系数;E1和E2为电流密度分别为1,10 mA·cm-2时对应的电压梯度。

泄漏电流密度JL为0.75E1对应的电流密度。由表1可以看出,随着Sb2O5掺杂量增加,非线性系数和泄漏电流密度均先减小,掺杂量增加至0.15%时,非线性系数略微增大,但泄漏电流密度显著增大,掺杂量为0.10%时,非线性系数和泄漏电流密度分别为33和4.5 μA·cm-2。泄露电流密度的显著增加会大大降低压敏电阻的综合电性能,因此Sb2O5掺杂量不宜过高。

2.4 SnO2压敏电阻的交流阻抗曲线

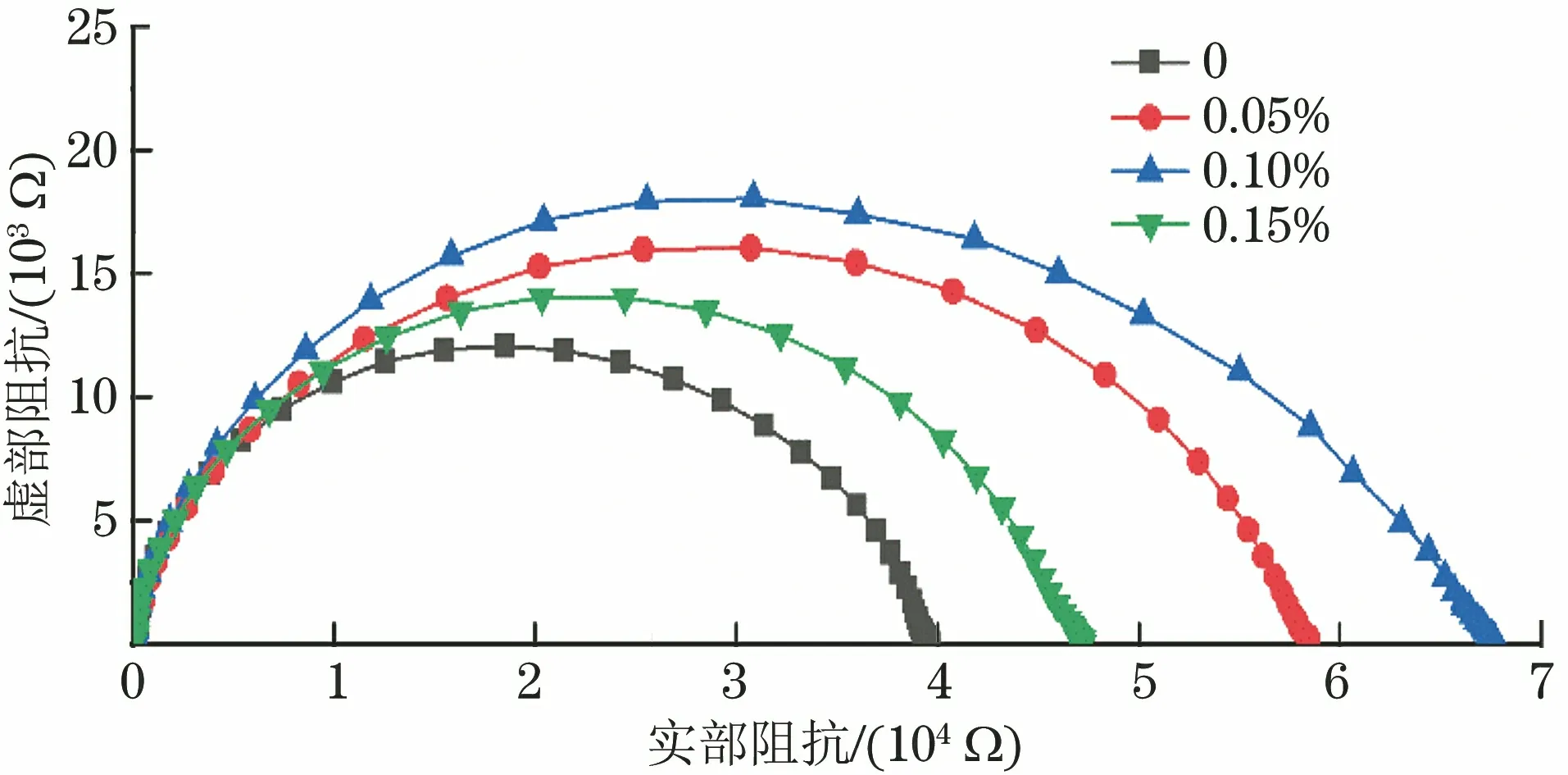

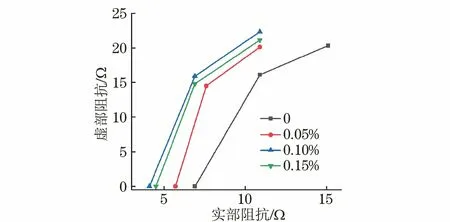

势垒的大小与晶粒和晶界之间的费米能级差有关,费米能级差越大,势垒越高[10]。图5实轴分量上的右截止点为晶界电阻大小,图6实轴分量上的左截止点为晶粒电阻大小,由图5和图6可以看出,Sb2O5掺杂量为0.10%时,压敏电阻晶粒和晶界之间的费米能级差最大,势垒最高,这与C-V曲线一致,此时压敏电阻的晶粒电阻最小,为4.1 Ω,晶界电阻最大,为67.7 kΩ,这有利于SnO2压敏电阻综合电性能的改善。

图5 不同Sb2O5掺杂量SnO2压敏电阻的交流阻抗曲线Fig.5 Alternating-current impedance curves of SnO2 piezoresistorwith different doping amouts of Sb2O5

图6 不同Sb2O5掺杂量SnO2压敏电阻高频范围内的局部交流阻抗曲线Fig.6 Local alternating-current impedance curves of SnO2 piezoresistorwith different doping amouts of Sb2O5 at high frequencies

3 结 论

(1) 随Sb2O5掺杂量增加,SnO2压敏电阻的晶粒尺寸、界面态密度先增大后减小,电压梯度、非线性系数和泄漏电流密度均先减小后增大,且泄漏电流密度的增幅明显,这不利于压敏电阻的综合电性能改善。

(2) Sb2O5掺杂量为0.10%时,SnO2压敏电阻的界面态密度最大,泄漏电流密度最小,晶粒电阻最小,综合电性能最好。