高功率太赫兹基波压控振荡器设计

傅海鹏 孙辉

摘 要:基于55 nm CMOS工艺提出了一款具有高输出功率的太赫兹基波压控振荡器(Voltage-Controlled Oscillator,VCO). 设计采用堆叠结构来克服单个晶体管供电电压受限导致输出摆幅较低的问题来有效提高了输出功率. 依据单边化技术在核心晶体管的栅漏之间嵌入自馈线来调整栅漏之间的相移和增益以最大化晶体管在期望频率下的可用增益,从而提高晶体管的功率输出潜力. 提取版图寄生后的仿真结果表明:在2.4 V供电电压下,VCO的输出频率范围为200.5 GHz~204.4 GHz,电路峰值输出功率为3.25 dBm,在1 MHz的频偏处最优相位噪声为-98.7 dBc/Hz,最大效率为8.1%. 包括焊盘在内的版图面积仅为0.18 mm2. 此次工作实现了高输出功率并具有紧凑的面积,为高功率太赫兹频率基波VCO设计提供了一种设计思路.

关键词:太赫兹;压控振荡器;高功率;高效率

中图分类号:TN752 文献标志码:A

Design of Terahertz Fundamental Wave Voltage-controlled

Oscillator with High Output Power

FU Haipeng SUN Hui

(School of Microelectronics,Tianjin University,Tianjin 300072,China)

Abstract:A terahertz fundamental Voltage-Controlled Oscillator(VCO) with high output power in 55 nm CMOS process is proposed in this paper. The stacked structure is adopted to solve the problem of low output swing caused by the limited supply voltage of a single transistor,thereby effectively increasing the output power. Based on the unilateralization technique,a self-feeding line is embedded between the gate and drain of the core transistor to adjust the phase shift and gain in order to maximize the available gain of the transistor at the desired frequency,thereby increasing the power output potential of the transistor. The simulation results after extracting the parasitic parameters of the layout show that,under a supply voltage of 2.4 V,the output frequency of this VCO ranges from 200.5 GHz to 204.4 GHz,the peak output power of the circuit is 3.25 dBm,the minimum phase noise is -98.7 dBc/Hz at the frequency deviation of 1 MHz,and the maximum efficiency of the circuit is 8.1%. The layout area including the pad is only 0.18 mm2. This work achieves high output power with a compact area and provides a design mentality for the realization of high-power terahertz fundamental VCOs.

Key words:terahertz;Voltage-Controlled Oscillator(VCO);high power;high efficiency

太赫茲频段具有穿透性、安全性、宽带性等独特优点,因此在无线通信、公共安全检测、成像等领域具有十分广阔的应用场景[1]. 而上述应用均需要具有较高输出功率的太赫兹振荡器. 但是由于太赫兹频率已接近硅基晶体管的最高振荡频率fmax,晶体管的可用增益会急剧下降,此外,在如此高的频率下,无源器件受趋肤效应、寄生等影响产生的损耗更加显著,这些因素使得基于硅基工艺的晶体管输出功率有限. 尽管使用Ⅲ-Ⅴ 族化合物半导体工艺可以使太赫兹频段的振荡器设计实现较优的性能[2-3],但是高昂的工艺成本令其目前无法大规模应用.

CMOS 工艺具有低成本、集成度高等优势,并且随着 CMOS 技术不断发展,CMOS 工艺可达到的fmax不断提高,CMOS工艺的性能也不断提升,因此采用 CMOS 工艺设计高性能太赫兹振荡器已成为可能. 由于太赫兹频带接近或超过大多数 CMOS 工艺的fmax,提取高次谐波实现太赫兹工作频率是目前基于 CMOS 工艺的主要选择[4-5],但由于提取高次谐波使得振荡器的输出功率相当有限. 为了解决谐波提取功率受限的问题,文献[6-9]采用多核耦合进行功率合成的方法实现了较高的输出功率和较优的相位噪声,然而功率合成会不可避免地导致高功耗和高损耗,从而使电路 DC-RF效率较低,并且会增加电路的设计复杂度,占用较大的面积.

直接利用基波实现太赫兹振荡器可以避免谐波提取导致的基波能量浪费,并且设计相对简单. 文献[10-12]对采用基波实现太赫兹振荡器进行了研究,并验证了采用基波实现太赫兹振荡器的可行性. 但是由于基波振荡频率接近工艺fmax以及受限于低供电电压,上述工作的输出功率十分有限,并且相噪性能与目前采用高次谐波进行功率合成实现的太赫兹振荡器相比仍有一定差距.

针对上述问题,本文提出了一种基于两级晶体管堆叠的基波压控振荡器. 堆叠结构的使用可以提高供电电压从而提高输出电压摆幅进而有效提高输出功率. 此外电路还采用了单边化技术来缓解太赫兹频率下晶体管性能迅速下降的问题. 版图电路后仿真表明设计实现了较高的输出功率和效率,并具有低相位噪声和紧凑的面积,验证了提出架构的可行性.

1 电路分析与技术

1.1 单边化技术

为了实现具有较高输出功率的基波振荡器需要晶体管在太赫兹频率下仍具有较高的可用增益.但是随着工作频率进入毫米波/太赫兹频段,晶体管的寄生效应也越来越显著,栅极寄生网络和栅漏寄生电容会引入额外的相移以及负反馈路径,使得晶体管增益降低,输入输出隔离度变差,从而使得晶体管在传统结构下难以发挥最大输出潜力. 因此提高输出功率可以通过抵消栅漏寄生电容和栅极寄生网络对晶体管造成的影响,使晶体管网络变得单向化来实现.

早在 1954 年,Mason就提出了晶体管单边化以获得最大化输出潜力的思想[13],他在文章中提出了晶体管单边功率增益(Unilateral Power Gain)U 的概念,并认为如果将晶体管视作一个线性二端口网络,那么该线性二端口网络嵌入到如图 1 所示的线性无损互易网络后,新构建的二端口网络的单边功率增益仍为 U,即 U 是晶体管的固有特性,而与嵌入的元件无关. 此外当新构建的等效二端口网络反向传输为零时即电路单边化时,U 即为晶体管所能达到的最大功率增益.文献[14]对文献[13]所做的工作进行了扩展,同样以图 1 为例推导得出在单向化的情况下产生最大基波输出功率晶体管需要满足以下最优增益和最优相位条件

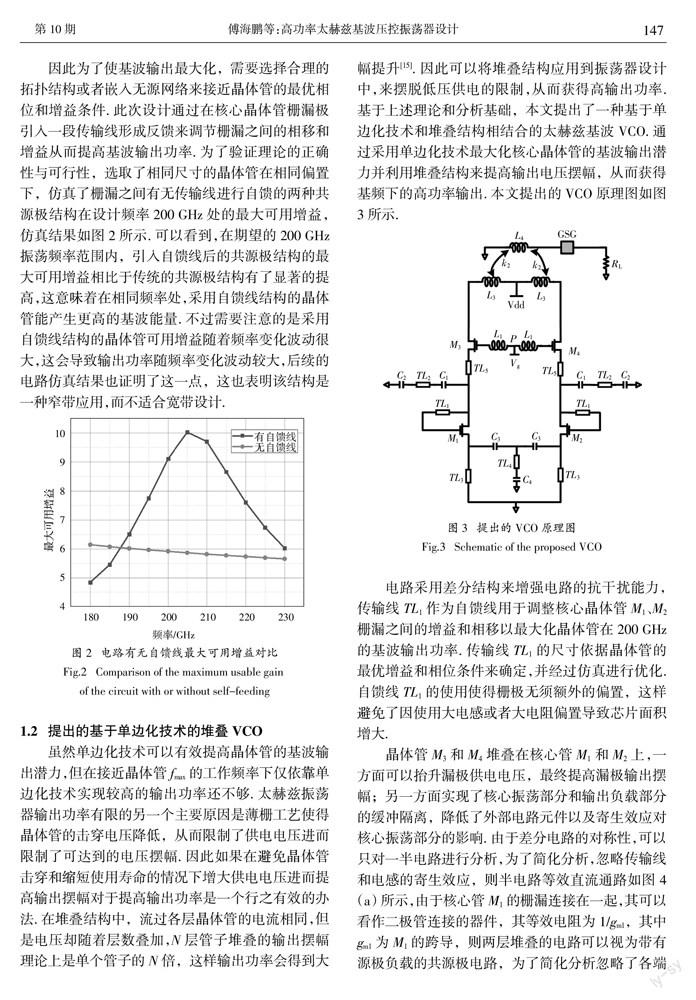

因此为了使基波输出最大化,需要选择合理的拓扑结构或者嵌入无源网络来接近晶体管的最优相位和增益条件. 此次设计通过在核心晶体管栅漏极引入一段传输线形成反馈来调节栅漏之间的相移和增益从而提高基波输出功率. 为了验证理论的正确性与可行性,选取了相同尺寸的晶体管在相同偏置下,仿真了栅漏之间有无传输线进行自馈的两种共源极结构在设计频率 200 GHz 处的最大可用增益,仿真结果如图 2 所示. 可以看到,在期望的 200 GHz 振荡频率范围内,引入自馈线后的共源极结构的最大可用增益相比于传统的共源极结构有了显著的提高,这意味着在相同频率处,采用自馈线结构的晶体管能产生更高的基波能量. 不过需要注意的是采用自馈线结构的晶体管可用增益随着频率变化波动很大,这会导致输出功率随频率变化波动较大,后续的电路仿真结果也证明了这一点,这也表明该结构是一种窄带应用,而不适合宽带设计.

1.2 提出的基于单边化技术的堆叠VCO

虽然单边化技术可以有效提高晶体管的基波输出潜力,但在接近晶体管fmax的工作频率下仅依靠单边化技术实现较高的输出功率还不够. 太赫兹振荡器输出功率有限的另一个主要原因是薄栅工艺使得晶体管的击穿电压降低,从而限制了供电电压进而限制了可达到的电压摆幅. 因此如果在避免晶体管击穿和缩短使用寿命的情况下增大供电电压进而提高输出摆幅对于提高输出功率是一个行之有效的办法. 在堆叠结构中,流过各层晶体管的电流相同,但是电压却随着层数叠加,N 层管子堆叠的输出摆幅理论上是单个管子的 N 倍,这样输出功率会得到大幅提升[15]. 因此可以将堆叠结构应用到振荡器设计中,来摆脱低压供电的限制,从而获得高输出功率. 基于上述理论和分析基础,本文提出了一种基于单边化技术和堆叠结构相结合的太赫兹基波 VCO. 通过采用单边化技术最大化核心晶体管的基波输出潜力并利用堆叠结构来提高输出电压摆幅,从而获得基频下的高功率输出. 本文提出的 VCO 原理图如图 3 所示.

电路采用差分结构来增强电路的抗干扰能力,传输线TL1作为自馈线用于调整核心晶体管M1、M2栅漏之间的增益和相移以最大化晶体管在 200 GHz 的基波输出功率. 传输线TL1的尺寸依据晶体管的最优增益和相位条件来确定,并经过仿真进行优化. 自馈线TL1的使用使得栅极无须额外的偏置,这样避免了因使用大电感或者大电阻偏置导致芯片面积增大.

晶体管M3和M4堆叠在核心管M1和M2上,一方面可以抬升漏极供电电压,最终提高漏极输出摆幅;另一方面实现了核心振荡部分和输出负载部分的缓冲隔离,降低了外部电路元件以及寄生效应对核心振荡部分的影响. 由于差分电路的对称性,可以只对一半电路进行分析,为了简化分析,忽略传输线和电感的寄生效应,则半电路等效直流通路如图 4(a) 所示,由于核心管M1的栅漏连接在一起,其可以看作二极管连接的器件,其等效电阻为1/gm1,其中gm1为M1的跨导,则两层堆叠的电路可以视为带有源极负载的共源极电路,为了简化分析忽略了各端口寄生电感和栅漏寄生电容的影响.其小信号等效电路如图 4(b) 所示

可以看到两层晶体管堆叠将二极管连接状态下的M1的输出阻抗提高了(gm1 + gm3 + gmb3)r03倍,高输出阻抗可以提高核心晶体管的屏蔽能力,减小外部输出网络对核心部分的影响,并且高输出阻抗也使得电路增益有了大幅提高,从而能够获得更大的电压摆幅提高输出功率.

为了确保电路的差分性,晶体管M3和M4的栅极偏置电感L1采用差分结构. 差分电感L1可以在虚地点P引入共模损耗来抑制共模振荡.此外传输线TL3、TL4以及差分电容C3构成了选频网络来加强对共模振荡的抑制,进一步增强差分稳定性. 传输线 TL3实现为相对于基频f0的四分之一波长传输线用以提供直流通路,并減小基波信号泄漏. 电容对C3用于与核心晶体管的寄生电容进行串联来减小谐振腔的等效容值来提高振荡频率. 传输线TL4实现为相对于基波f0的八分之一波长传输线,这样对二次谐波2f0呈现高阻特性,有助于降低相位噪声.

為了解决堆叠以后由于寄生导致的各层晶体管输出电压相位不一致从而导致输出功率下降的问题,级间采用电容C1和传输线TL2以及TL5来进行上下两级晶体管的相移和阻抗调整以改善两层之间的匹配,从而实现电压摆幅最大化叠加.大容值电容 C2和C4在基波f0下可视作短路来为传输线TL2和TL4定义交流地. 输出采用电感L3以及L4构成平衡-非平衡转换器(Balance-Unbalance,Balun)进行差分信号到单端信号的转换,并输出到射频焊盘进而驱动下一级电路的负载RL,采用 Balun 的好处一方面在于可以将两路信号合成转化为单路输出,有助于提高输出功率(理论上提升 3 dB);另一方面实现了交流信号和直流信号的分离而不需要额外设计隔直电容.

相位噪声是振荡器设计的一个核心指标,李森(Lesson)相位噪声模型[16]指出提高基波功率和提升谐振腔的Q值都可以降低相位噪声. 堆叠结构以及单边化技术的使用提高了基波输出摆幅,从而使相噪性能有了较好的改善. 此外可以通过提高无源器件的 Q 值来进一步降低相噪.

工艺厚层金属具有高电导率,欧姆损耗较低,因此Q采用最厚层金属实现提升Q值. 在高频电磁仿真软件中的建模如图 5(a) 所示,采用差分结构相比于单端结构能够实现更高的 Q 值,在满足工厂加工规则的前提下,L1设计为接近圆形的八边形结构来进一步提高 Q值,通过调整电感的半径、线宽以及金属地的开口大小在满足感值需求的情况下可以实现对Q值的优化. 最终L1的仿真结果如图 5(b) 所示,L1在设计频率200 GHz处的感值选取为 29 pH,优化后的 Q值为 27.6.

除电源线外,设计所需的传输线以及信号连接线均采用工艺的最厚层金属设计来降低损耗提高Q值. 为了方便版图布局并以较小的尺寸实现较高的耦合系数,Balun采用垂直结构来实现,并使用最厚的两层金属来提高Q值. 设计所用到的电容采用金属-氧化物-金属(Metal-Oxide-Metal,MOM)电容结构,并利用工艺的多层薄金属层堆叠来提高电容密度从而节约面积. 所有无源器件以及信号线连接线均采用高频电磁仿真软件进行建模分析以及优化,并将除电容和晶体管有源区以外的所有无源部分利用电磁仿真软件进行如图6所示的联合仿真来提高设计的可靠性和仿真准确性,并将整体仿真得到的数据导入到仿真软件与提取寄生后的晶体管进行联合仿真与优化.

2 结果与分析

本次设计采用55 nm CMOS工艺进行仿真设计,结合高频电磁仿真优化后,最终设计版图如图 7 所示,其面积仅为 0.18 mm2. 提取版图寄生参数后进行电路仿真,频率调谐通过改变栅极偏置电压来实现,在 2.4 V 的供电电压下,当栅极偏置从 1.2 V变化到 2.0 V时,VCO的振荡频率近似线性单调变化,VCO的振荡频率范围为 200.5~204.4 GHz,调谐带宽为 3.9 GHz (1.9% 的调谐比).

3 结 论

本文提出了一款基于堆叠结构的高输出功率、高效率太赫兹基波VCO. 设计采用两层管子堆叠来提高输出摆幅,并利用单边化技术来最大化管子的基波输出能力,从而使电路无需采用多核功率合成也能实现较高的功率输出. 后仿真结果表明电路具有3.25 dBm 的高输出功率,并具有高达8.1% 的效率,此次设计达到了目前工作频率在200 GHz 左右的CMOS基波振荡器的最好性能,并且与采用高次谐波进行多核功率合成的设计相比仍具有很强的竞争性,验证了所提出的结构的可行性.

参考文献

[1] SIEGEL P H. Terahertz technology[J]. IEEE Transactions on Microwave Theory and Techniques,2002,50(3):910—928.

[2] YUN J,YOON D,KIM H,et al. 300-GHz InP HBT oscillators based on common-base cross-coupled topology[J]. IEEE Transactions on Microwave Theory and Techniques,2014,62(12):3053—3064.

[3] KIM D,JEON S. A WR-3 band fundamental voltage-controlled oscillator with a wide frequency tuning range and high output power[J]. IEEE Transactions on Microwave Theory and Techniques,2019,67(7):2759—2768.

[4] HSIEH C L S,LIU Y C. A low phase noise 210-GHz triple-push ring oscillator in 90-nm CMOS[J]. IEEE Transactions on Microwave Theory and Techniques,2018,66(4):1983—1997.

[5] MENG X,CHI B,WANG Z. CMOS cross-coupled oscillator operating close to the transistor's fmax[J]. IEEE Microwave and Wireless Components Letters,2017,27(12):1131—1133.

[6] NIKPAIK A,MASNADI SHIRAZI A H,NABAVI A,et al. A 219-to-231 GHz frequency-multiplier-based VCO with~3% peak DC-to-RF efficiency in 65-nm CMOS[J]..IEEE Journal of Solid-State Circuits,2018,46(10):3217—3231.

[7] TOUSI Y M,MOMENI O,AFSHARI E. A novel CMOS high-power terahertz VCO based on coupled oscillators:theory and implementation[J]. IEEE Journal of Solid-State Circuits,2012,47(12):3032—3042.

[8] KANANIZADEH R,MOMENI O. Second-harmonic power generation limits in harmonic oscillators[J]. IEEE Journal of Solid-State Circuits,2018,53(11):3217—3231.

[9] JALILI H,MOMENI O. A 230-GHz high-power and wideband coupled standing wave VCO in 65-nm CMOS[J]. IEEE Journal of Solid-State Circuits,2020,55(3):547—556.

[10] WANG H,CHEN J,DO J T S,et al. High-efficiency millimeter-wave single-ended and differential fundamental oscillators in CMOS[J]. IEEE Journal of Solid-State Circuits,2018,53(8):2151—2163.

[11] KWON H T,NGUYEN D,HONG J P. A 219-GHz fundamental oscillator with 0.5 mW peak output power and 2.08% DC-to-RF efficiency in a 65 nm CMOS[C]// 2016 IEEE MTT-S International Microwave Symposium. San Francisco,CA,USA:IEEE,2016:1—3.

[12] NGUYEN T D,HONG J P. A high fundamental frequency sub-THz CMOS oscillator with a capacitive load reduction circuit[J]. IEEE Transactions on Microwave Theory and Techniques,2020,68(7):2655—2667.

[13] MASON S J. Power gain in feedback amplifier[J]. Transactions of the IRE Professional Group on Circuit Theory,1954,1(2):20—25.

[14] MOMENI O,AFSHARI E. High power terahertz and millimeter-wave oscillator design:a systematic approach[J]. IEEE Journal of Solid State Circuits,2011,46(3):583—597.

[15] WU C W,LIN Y H,HSIAO Y H,et al. Design of a 60-GHz high-output power stacked-FET power amplifier using transformer-based voltage-type power combining in 65-nm CMOS[J]. IEEE Transactions on Microwave Theory and Techniques,2018,66(10) :4595—4607.

[16] LESSON D B. A simple model of feedback oscillator noise spectrum[J]. Proceedings of the IEEE,1966,54(2):329—330.

——HeightsTM用高效率和智能化提升服务水平