宇航抗辐射加固集成电路技术发展与思考

赵元富,王 亮,岳素格,隋成龙,李同德

(1.中国航天电子技术研究院,北京 100094;2.北京微电子技术研究所,北京 100076)

0 引言

抗辐射加固集成电路是航天的核心基础技术,其发展追随着通用集成电路技术发展的脚步,但又有其独特性。首先,航天应用需求对集成电路的性能要求不断提升,同时集成电路在复杂空间环境下持续工作,又要求其具有抗辐射能力及高可靠性,即需要高性能的抗辐射加固集成电路。随着我国深空探测、载人航天等一系列重大宇航工程不断推进,对抗辐射加固集成电路的性能需求将进一步提高,新工艺、新器件、新方法和新手段将不断引入,新一代抗辐射加固集成电路研制面临许多新的挑战。本文总结了集成电路发展趋势和我国抗辐射加固集成电路发展现状,分析了抗辐射加固集成电路的未来发展需求,并对我国抗辐射加固集成电路需重点关注的发展方向进行了展望与探讨。

1 抗辐射加固集成电路发展

集成电路自20 世纪50 年代问世以来发展迅速,尤其是20 世纪80 年代以来,在国民经济、军事国防和日常生活中都起到了越来越重要的作用。同时,随着太空探索和利用的不断深入,抗辐射加固集成电路也取得了长足的进步。

1.1 集成电路发展趋势

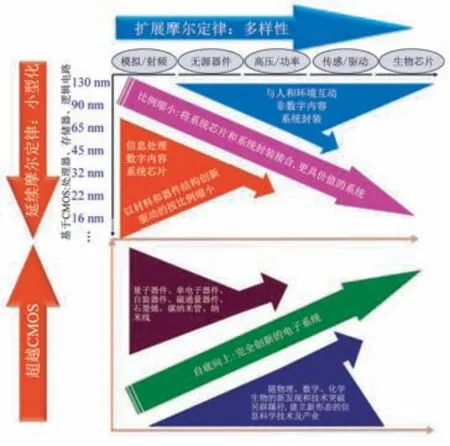

1965 年,英特尔创始人戈登·摩尔提出了著名的摩尔定律(Moore’s Law),对集成电路集成度成倍增长的现象做出预测,集成电路技术的发展虽然需不断克服各种技术瓶颈,但始终遵循该定律。随着集成电路工艺技术不断进步,近年来,集成电路技术的发展趋势又有了新的分支,大体形成了3 个发展方向[1],如图1 所示。

图1 集成电路技术发展的3 个方向(ITRS2.0)Fig.1 Three directions for integrated circuit technology development(ITRS2.0)

1)延续摩尔定律(More Moore)。由于材料技术、工艺能力的进步,实现特征尺寸持续等比例缩小,从而不断提高芯片集成度。伴随着关键技术的不断突破,集成电路特征尺寸不断减小,这些特征尺寸变化成为了全球电子产品整体性能不断进化的核心驱动力。基于台积电最新3 nm 工艺研发的芯片,晶体管密度是7 nm 的3.6 倍,达2.5 亿个/mm2。但这一方向的持续推进,带来了极大的资本壁垒,根据市场研究机构IBS 的数据,5 nm 芯片的设计费用超过5 亿美元,新建一条3 nm 产线的成本约150 亿~200 亿美元,同时,工艺开发费用约40 亿~50 亿美元,行业呈现寡头垄断。目前能够提供7 nm 及以下先进制程工艺的厂商仅有台积电、英特尔和三星。

2)扩展摩尔定律(More than Moore)。以系统级封装技术为基础,将数字和非数字、硅和非硅、CMOS 和非CMOS 等不同类型电路或电、光、微机械等异质结构器件,通过不同方式进行堆叠,实现更快的开发速度、更高的计算力、更低廉的成本。世界知名半导体企业均为系统级封装技术的主要参与者,台积电通过采用CoWoS 封装技术和LIPINCON 互连技术,将大型多核设计划分成多个小芯片一体封装,从而提供更高的良率和更好的经济性。英特尔也做到将不同IP、不同工艺的各种芯片封装在一起,从而省去漫长且成本颇高的重新设计、测试和流片过程。

3)超越CMOS(Beyond CMOS)。新理论、新材料、新结构正处于探索阶段,以取代面临极限的CMOS 器件,如自旋电子、单电子、量子、分子和单原子器件等。目前,以原子分子自组装技术为基础的纳米电子学正在蓬勃兴起,代表有量子点阵列、碳纳米管、石墨烯,其中,量子电子器件已在实验室条件下研制成功。这些技术将成为集成电路技术未来发展的持续动力。

1.2 抗辐射加固集成电路发展特点

抗辐射加固集成电路的开发主要由航天或国防需求驱动,其发展趋势受集成电路总体发展趋势影响,主要呈现以下特点:

1)多样化需求导致的产品方向多样化。为满足载人航天、行星探测、深空探测等多种任务需求,针对航天型号特定功能而开发的抗辐射加固集成电路也更加多样化。以星载计算机为例,典型单机中需要实现数据运算处理功能的处理器芯片、实现数据存储功能的存储器芯片、实现数据中继与传输功能的接口电路芯片和控制器芯片、实现数据转换功能的AD/DA 芯片等多种宇航用集成电路。另外,集成电路领域技术的进步,也推动着航天器部组件的更新换代,从而产生新的抗辐射加固集成电路需求。

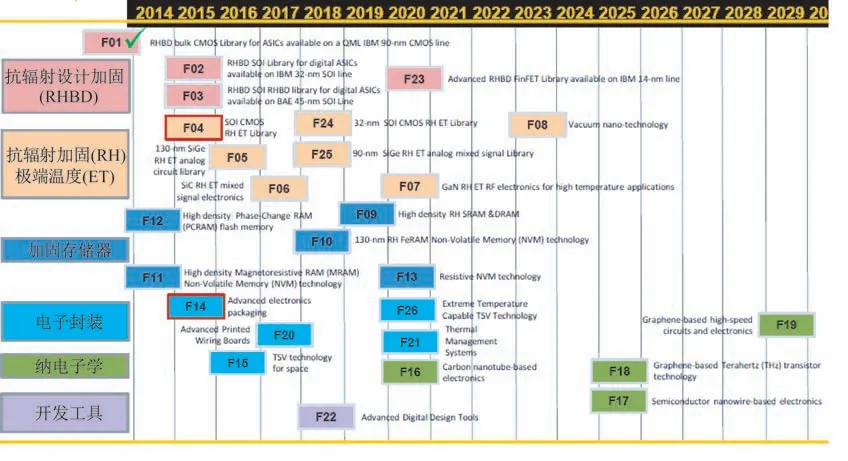

2)为绕开先进专用生产线建线的巨额投入,抗辐射加固技术路线从工艺加固转向设计加固。以美国为例,2003—2008 年先后建立了0.25 μm、0.13 μm等专用抗辐射加固工艺线。与此同时,由于意识到抗辐射加固集成电路的发展进入纳米工艺时代,斥资建立仅用于小批量生产的专用工艺线性价比太低,为此,美国国防部和国家安全局主导,开始实施可信赖集成电路战略计划,采用抗辐射设计加固的方式,直接在经过国防安全认证的商用工艺线上制造,将抗辐射加固集成电路的研制能力从0.15 μm 跨代提升到32 nm。图2 为美国国家航空航天局(NASA)航空航天电子设备发展路线中基础技术的发展路线,按照规划,目前使用32 nm SOI 工艺的设计加固技术已经成熟,而文件中也明确表示由于商用先进工艺已经可以提供较为充分的耐辐射能力和耐高温能力,因此,设计加固对比开发和维护专用的抗辐射加固工艺线具有明显成本优势[2]。

图2 NASA 航空航天电子设备发展路线——基础技术类Fig.2 NASA’s roadmap on avionics devices—fundamental technology

3)面向未来,绕开先进工艺下集成电路设计和制造的巨额投入,以高效、低成本为目标,重点探索依靠可重构/可编程芯片实现航天集成电路功能。随着军事智能化的不断发展,对高性能宇航集成电路的多样化需求层出不穷,传统抗辐射加固集成电路开发流程已逐渐无法满足目前需求,因此,必须要开发多功能、可重构、适应多种应用场景的宇航集成电路。以现场可编程门阵列(Field Programmable Gate Array,FPGA)为代表的可重构芯片,可通过灵活编程实现各种复杂的功能。从发展角度来讲,它可以替代目前宇航型号中诸多功能各异的集成电路,能够大幅节省各类宇航系统的研制时间与成本。

1.3 我国宇航抗辐射加固集成电路发展现状

综上所述,抗辐射加固集成电路是建设航天强国的重要基础之一。在国家的大力支持下,经过数十年的努力,我国抗辐射加固集成电路取得了长足发展,通过自主创新,攻克了多项重大技术难题,解决了型号瓶颈问题,满足了体系化、成批量的工程应用需求。

长期以来,我国宇航集成电路专用生产线少,工艺相对落后,难以满足航天发展对抗辐射加固集成电路的需求。为此,20 世纪90 年代末,北京微电子技术研究所率先采用“商用线+设计加固”的技术路线研制抗辐射加固集成电路,但必须解决设计加固面临的诸多挑战,如单粒子翻转导致集成电路功能紊乱、单粒子闩锁导致集成电路可靠性降低、一般设计加固方式导致集成电路功耗与面积开销过大等。为此,在国家的大力支持下,北京微电子技术研究所从集成电路辐射效应机理研究出发,经过潜心钻研和不懈攻关,攻克了单粒子翻转加固、单粒子闩锁加固、总剂量加固等关键技术,实现了设计加固路线下集成电路产品的高性能、高可靠与低开销。同时,开发了抗辐射加固集成电路研制平台,研制了以抗辐射FPGA、CPU等核心器件为代表的数百款产品,基本构建了我国抗辐射加固集成电路产品谱系,并体系化应用于各类宇航型号。设计加固技术路线使我国能够充分利用后发优势,实现宇航集成电路的跨越式发展。然而,可重构芯片由于硬件的复杂性和状态的多样性,抗辐射加固是一个难题,需要探索针对可重构芯片的新型抗辐射加固技术途径。

2 抗辐射加固集成电路发展需求

目前,航天技术的不断发展对抗辐射加固集成电路提出了新的需求。航天器具有两大发展趋势:1)从单一功能应用向多功能融合发展,常规的通信卫星、导航卫星、遥感卫星的功能不断增加,其定位从单一功能航天器向具有灵活载荷能力、支持多系统集成的空间平台发展[3-5];2)向低功耗、小型化、高集成度方向发展。

在航天器的信息感知、处理和传输等单元模块中,广泛利用微电子技术,将器件、单机甚至系统芯片化,大幅缩小应用单元的体积,提高了航天器的有效载荷率。随着宇航芯片工艺从180 nm 到65 nm,再到28 nm,宇航集成电路体积更小、功耗更低,为微小卫星的研制提供了有利条件,美国、欧洲都提出并实施了利用微小卫星组成低轨星座的各种项目,并且在小卫星上逐步集成多种功能芯片,诸如集成激光通信功能等,以支持更多的空间应用[6-7]。总体上看,高效能计算能力和高压大功率是其中最显著的共性需求。

2.1 高效能计算

集成电路的发展与现代军事变革息息相关。21 世纪初,信息化成为军事变革的核心,战争形态也由机械化战争转化为信息化战争[8]。随着人工智能等技术快速发展,现代战争形式也从信息化战争逐步转变为智能化战争。以在轨卫星为基本单元的智能化天基互联网将成为未来智能化战争中的核心,海量的战场信息通过传感器获取,并由天基互联网络实时处理和传输,天基网络与地面系统互联互通,形成一个天、空、地立体交联的时空动态网络[9-10]。天基卫星网络对航天器提出了大带宽通信、海量数据处理、支持人工智能等功能要求,而这些功能都依赖于先进集成电路,尤其是先进的抗辐射加固集成电路实现。

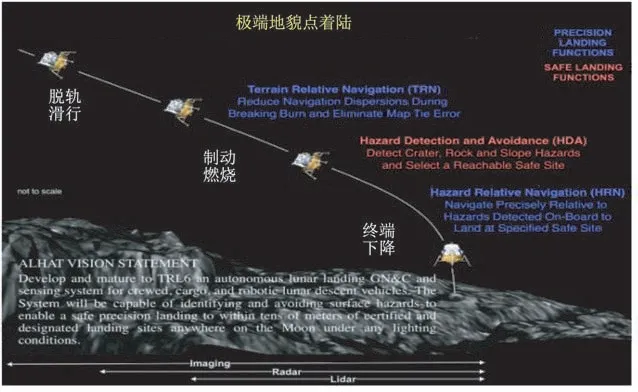

除了军事应用之外,在气象、遥感、导航、通信等民用航天领域,也产生了对抗辐射加固集成电路的不同需求。美国太空探索技术公司(SpaceX)发起了旨在向全球提供免费高速互联网服务的“星链”(Starlink)计划,计划部署数万颗卫星,所有卫星具有大带宽、低时延、广连接的通信功能。同时,随着小行星探测、深空探测等项目的不断发展,亟需发展具备自主观测、自主决策、自主导航能力的航天器,需要对行星表面气象、地理等数据实时观测,并对数据进行实时处理,在短时间内调整航天器姿态和降落策略。如图3 所示,NASA设想的航天器在极端地形情况下精准登月着陆过程[11]。在整个着陆过程中,综合应用了图像传感器、雷达、激光雷达等设备,实时检测、决策并调整航天器姿态,自动完成整个着陆过程。为此,新一代航天器对宇航集成电路的需求主要体现在信息处理能力的提升、通信能力的提升和智能化等需求。

图3 航天器自主着陆过程[11]Fig.3 Autonomous landing of a spacecraft[11]

按照摩尔定律,随着集成电路工艺的不断提升,处理器的集成密度不断提升,主频不断提高,相对功耗不断降低,而这也推动着处理器计算效能的提升。对于航天器上使用的抗辐射加固处理器,通常比商用处理器性能落后一至两代,且差距越来越大,如图4 所示。如今,美国最先进的计算单机模块是美国BAE 系统公司开发的RAD5545 模块,其核心采用了先进的45 nm 抗辐射加固SOI 工艺,但是总体性能远远落后于商用处理器[12-13]。

图4 美国航天计算平台与商用处理器性能对比与发展趋势Fig.4 Comparison between the roadmaps of commercial and radiation-hardened processors

针对目前航天器计算性能瓶颈,NASA 在2013年启动了“高性能航天飞行计算”项目(HPSC),目的是开发颠覆性的航天用处理器,并显著改进航天器计算能力。该项目计划由波音公司提供抗辐射加固多核、可重构计算处理器Chiplet 模块,每个小芯片都包含8 个通用ARM 内核,以及与存储器和外围设备的接口,并将灵活地定制处理器性能、功耗和容错能力,最终取得相对目前先进平台性能近百倍的提升,以满足未来广泛变化的航天任务需求。以火星探测任务为例,预计项目完成后,该项目成果将带来更大带宽数据传输能力以及数据处理能力,并保障包括航天器的自主进入、下降与着陆、自主交会与对接等在内的多项航天任务顺利实施[14]。该项目中,明确地对其开发的下一代宇航用高性能计算平台的抗辐射指标和可靠性指标进行了规定[11],可见抗辐射加固仍是未来宇航用集成电路的重点技术之一。

在专用卫星领域,高效能的计算能力可为高分辨遥感观测卫星、高通量通信卫星、高精度导航卫星等高性能卫星的发展提供保障。对于高分辨率遥感卫星,空间中获取和处理的数据量激增,现有宇航集成电路难以满足大数据实时处理的需求。欧美等航天强国一直重视在轨信息处理技术的研究、开发与应用,积极开展航天大数据实时处理和高精度处理的应用研究。近年来,随着卫星技术的不断发展,欧美又进一步布局超高性能计算技术在空间环境中的应用。

在军事应用上,天基计算能力成为了未来获得战场优势的关键。美军在2018 年发布了低轨小卫星星座BLACKJACK 项目,目的是使用具有较小尺寸、较轻重量、较低功耗和成本、具有机动功能的小型通信和监视卫星,建立用于太空态势感知、通信和预警一体化的低轨星座[15]。

该项目还计划使用集成人工智能和机器学习技术的高性能信息处理系统,在小卫星内部建立强有力的互联,并将使星座具有在轨处理海量数据的能力。该项目的关键点和星链项目高度重合,即利用卫星链路构建新型太空网络,谋求未来在太空战场中的绝对优势。每个卫星既是信息处理中心,又是高速传输中继,要实现这些目标,离不开高效能计算芯片的支撑。

2.2 高压大功率

目前,航天器能源系统呈现能源系统集成化、能量供给多源化、能量收集自主化、能量信息一体化等趋势,为提高能源利用率,支持空间新技术应用,发展高压大功率宇航集成电路以提高传输效率、降低传输损耗成为了未来航天器的必然需求。

在电推进等新型航天技术发展应用过程中,高压大功率器件是重要的技术支撑之一。电推进技术又称电力离子推进技术,主要技术思想是使用电能驱动工质喷射而产生动力,具有整体质量小、省燃料、比冲高等优点。电推进的应用一方面是电火箭应用方向,目前,美国火箭实验室(Rocket Lab)开发了瞄准于小卫星发射的“电子”火箭,成功执行了多次发射任务;另一方面,电推进目前也逐渐成为小卫星的主要动力系统。以星链为例子,每颗“星链”卫星质量约为227 kg,装有多个高通量天线、一个太阳能电池组和高精度导航系统,使用以氪为工质的霍尔推进器提供动力。星座组网后,每个节点(卫星)都具有动能变轨能力。在美国的相关演习中,“星链”成功实施了对洲际导弹的动态拦截,这一切得益于先进电推进技术提供的机动能力。霍尔电推进是目前主流的电推进技术之一,目前更高的比冲是霍尔电推进的重要发展方向之一,为了满足未来更大型的深空探测任务的需求,电推进的比冲必须增大,实现高比冲最直接的途径是高电压[16],而太空中的高电压应用则必须考虑功率器件的加固问题,以保证电推进器更高效、更可靠、更长寿命。

宇航用高压功率集成电路技术进步使宇航电子设备呈现出高性能、轻型化和小型化的发展趋势,而航天领域前沿技术的需求会加快这一趋势。目前,以宽禁带、耐高压为特征的GaN、SiC 等新一代半导体器件在民用领域快速发展,并逐渐在航天领域中开展应用[17]。在空间新应用领域,空间激光通信、空间太赫兹高速通信等技术的实现依赖于高压驱动。而在未来的航天前沿技术中,空间太阳能电站、基于超导磁体的太空辐射屏蔽装置都将使宇航用高压、大功率器件的需求大幅度提升。

3 我国抗辐射加固集成电路需重点关注的发展方向

长期以来,美国在宇航集成电路研发与应用领域一直处在领先地位。随着近年来我国宇航集成电路的发展步伐不断加快,美国又开始进行新一轮的规划和布局,依托“电子复兴”等系列计划,结合民营航天科技力量,从高性能宇航集成电路开发、商用高性能芯片评估等领域入手,谋求和扩大宇航抗辐射加固集成电路技术的领先优势。近年来,美国民营航天企业业务不断扩展,宇航用抗辐射加固集成电路也朝着成本更低、性能更高、技术迭代更快的方向发展。

目前来看,我国与美国在宇航集成电路全领域内尚存差距。跟随先进航天器技术发展趋势,为适应载人航天、探月工程、深空探测等多种航天任务的需求,我国宇航抗辐射加固集成电路应重点突破软加固的天算芯片、高压功率器件加固、单粒子效应仿真等三个发展方向。

3.1 软加固的天算芯片

为满足新一代航天智能化信息处理需求,必须采用基于先进工艺的高性能集成电路,但开发专用芯片成本极高,且开发周期极长。因此,我们预计未来宇航用核心芯片将是集智能、可重构和超算于一体的芯片,我们称其为“天算芯片”。天算芯片是一种通用的可重构芯片,其功能可以通过基于编程代码的二次设计来实现,以满足宇航集成电路的高性能、低成本和快速设计的需求。

然而,天算芯片功能强大、结构复杂、规模极大,若采用传统的工艺加固、设计加固等硬件加固方法研制,必然导致芯片性能严重下降,功耗严重增大,且设计难度、开发周期和成本都将难以承受。为此,针对天算芯片需要探索新的加固技术途径。采用芯片级软加固研制天算芯片是一种可行的办法。所谓芯片级软加固,有2 个层次的内涵:

1)软IP 加固:设计基于电路结构加固的IP,利用可重构芯片,应用于芯片功能的实现过程中,同时,通过将冗余、纠检、容错等手段融入到代码设计和综合实现中,使芯片的抗辐射加固能力得到提升。例如,在对FPGA 编程时,对关键逻辑模块进行3 模冗余设计,对关键存储模块进行纠检错设计,可有效提升最终电路的抗单粒子效应能力。

2)软件加固:基于已完成编程/重构的芯片硬件,通过增加软件手段,实现对芯片单粒子故障的识别、诊断、容错或自恢复,提高芯片应用的可靠性。

3.2 高压功率器件加固

离子、霍尔等电推进技术的空间应用,新型的空间激光通信设备、空间攻防武器的研制,空间太阳能电站、超导磁体屏蔽太空辐射等新设想要想付诸实践,其关键之一就是改良高压大功率电源技术。

然而,高压功率电源系统采用高压功率器件,这类器件的高压主要依靠高耐压的耗尽区承受。当粒子穿过耗尽区时,电子空穴对形成瞬间的导通通道,使高电压直接作用于栅氧等薄弱区域,导致器件烧毁等严重损伤。高压功率电源系统的抗辐射加固尤其是单粒子加固是一个世界性难题,但必须得到解决。

为此,首先需要研制抗辐射加固高压功率器件。面对百到千伏级电压需求,需采用GaN、SiC 等新型材料功率器件,而这些新型功率器件的抗辐射加固成为必须攻克的技术瓶颈;其次需要研究集成了高压功率器件的电源模块的抗辐射加固方法,通过多层级、全方位的加固,确保电源系统在轨可靠运行。

3.3 单粒子效应仿真

高效能计算依赖于高性能芯片,随着宇航集成电路集成度和复杂度越来越高,其加固设计难度和单粒子加固性能的全面准确评估变得非常困难,且成本极高。

一方面,目前尚缺少针对超大规模集成电路单粒子效应仿真的软件,导致单粒子性能无法在设计阶段预估,仅能通过试验验证,设计风险大,为减小风险必须采用保守的加固方案,难以实现高效能;另一方面,对高度复杂集成电路的试验评估变得异常困难。NASA 研究表明:对于1 GB SDRAM 器件,全模式单粒子试验评估需要66 096 h,约7.5 年,这种遍历式的评估不可能实现,且难以确定最劣情况。因此,非常有必要开展集成电路单粒子效应仿真研究,依靠计算机仿真软件完成芯片抗辐射性能的评估。

一方面,需要解决芯片单粒子效应的仿真方法和建模问题,打通从器件级仿真到芯片级仿真的关键技术;另一方面,需要开发支持超大规模集成电路单粒子效应仿真的软件,为实现芯片抗单粒子能力的预估和高效评估提供关键技术手段。

4 结束语

抗辐射加固集成电路作为宇航核心技术,是航天技术发展的关键基础之一。随着智能化天基卫星网络、深空探测等航天工程的开展,高效能计算和高压大功率成为未来对抗辐射加固集成电路的重要需求。结合集成电路技术发展趋势和未来宇航型号需求,充分探索和利用集成电路前沿技术,谋划确定重点发展方向,在软加固的天算芯片、高压功率器件加固和单粒子效应仿真等技术方向超前布局,在满足航天发展需求的同时,实现抗辐射加固集成电路的创新发展和技术引领。