优化的μC/OS-III实时内核中断管理机制

冯 冲,吴尧辉,吴昊珍

(1.河南理工大学 电气工程与自动化学院,河南 焦作 454150;2.河南理工大学 许继电气股份有限公司煤矿井下智能供电系统实验室,河南 焦作 454150;3.郑州工商学院,河南 郑州 451400)

嵌入式实时系统具有时间约束性、可预测性、可靠性等特点,其中实时性是衡量系统优劣的关键因素。嵌入式实时系统一般通过中断的方式对外部异常事件进行处理,其实时性能关乎中断的处理方式。

传统嵌入式实时系统外设中断优先级均高于操作系统内部任务优先级,在未关闭硬件中断的情况下,外设中断发生就立即响应并执行ISR(Interrupt Service Routines)。μC/OS-III实时操作系统可以选择以线程的方式处理中断,中断发生后仅在ISR中做简单处理(例如向任务发布消息、信号量等),然后调用中断服务并以任务的方式进行处理。两种中断执行模式都有各自的优缺点[1-3]。

1 μC/OS-III中断管理机制

μC/OS-III实时操作系统具有源代码公开、可裁剪、可固化等优点,其第三代内核的优点更为突出,不仅无任务数量限制,还可以直接向任务发送消息并支持时间片轮转调度[4-6]。

1.1 μC/OS-III两种中断模式

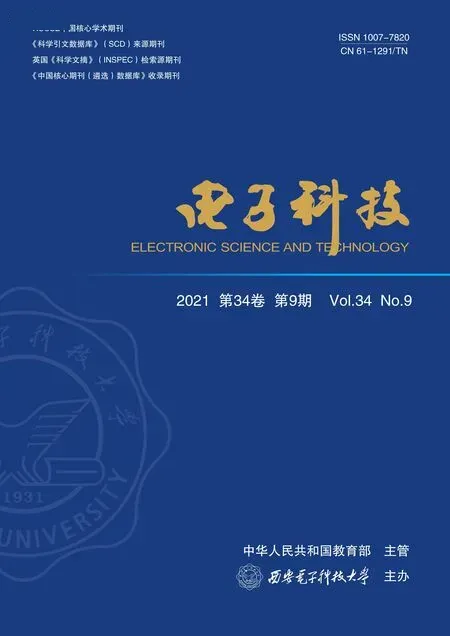

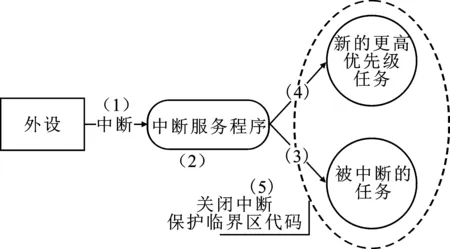

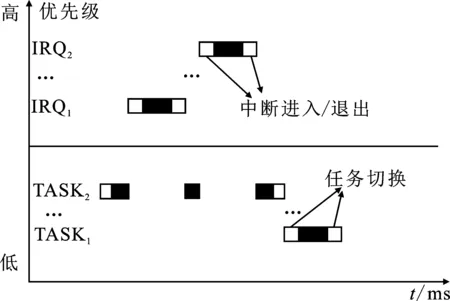

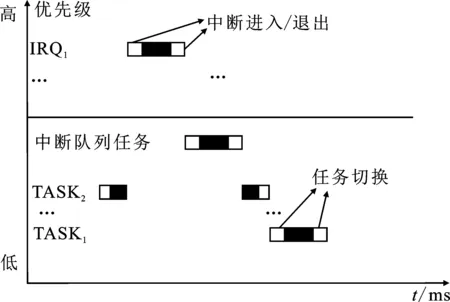

μC/OS-III实时操作系统提供两种中断模式,如图1和图2所示。通过OS_cfg.h文件,将OS_CFG_ISR_POST_DEFERRED_EN置0或1。置0时使用直接发布模式,在未关中断情况下,外设只要产生IRQ(Interrupt Request)信号,无论此时IRQ信号优先级处于何种级别,都会立即执行该ISR。置1时使用延迟发布模式,当中断发生后执行ISR。但该模式仅仅是向中断队列OS_INT_Q发送信号,异常事件的处理仍需转向IST中详细处理[7-11]。

图1 直接发布模式Figure 1. Direct release mode

图2 延迟发布模式Figure 2. Delayed release mode

μC/OS-III中断直接发布模式如图1所示,外设中断产生IRQ并调用ISR,在ISR中详细处理可能使某任务处于就绪态,处理完成后由中断退出调度。通过比较该任务和被中断任务优先级选择执行,从中断退出调度到优先性更高的任务执行期间,μC/OS-III均以关中断的方式对临界段进行保护。

μC/OS-III中断延迟发布模式如图2所示,外设中断产生IRQ并调用ISR,但ISR只向中断队列OS_INT_Q发送信号,随后中断处理任务OS_IntQTask就绪。又由于该任务在系统中的任务优先级为0(最高优先级)立即运行,发布信号量或消息给对应任务。若发布的任务优先级比被中断的任务优先级高,则立即抢占CPU执行权,反之则返回被中断任务继续执行。关闭中断时间段只在这一极短的过程中,大量的临界段代码处理过程则被放在了OS_IntQTask任务中,此处可开启锁定任务调度来确保临界段代码的完整执行。中断延迟发布模式将IRQ通过ISR处理转为IST处理方式,缩短了中断关闭时间。

1.2 μC/OS-III中断模式缺点

虽然μC/OS-III增加中断延迟发布模式可以将ISR(Interrupt Service Thread)转为线程方式处理,减少中断关闭时间,但是此种中断处理方式也有不足之处。由于中断队列OS_IntQTask任务在系统中为最高优先级任务,中断以IST方式处理情况,并没有细分,以至于处理粒度较粗,进而导致低优先级的ISR仍会干扰紧急任务的执行。μC/OS-III实时操作系统没有完全基于优先级剥夺CPU执行,外设中断任务始终高于系统管理任务的优先级,这将会影响紧急任务的执行。

2 优化μC/OS-III中断管理机制

针对章节1.2提出的μC/OS-III中断模式缺点,本研究优化了μC/OS-III中断管理机制,优化后的中断管理机制能够实现高优先级IRQ的快速响应并缩短紧急任务的截止期。本文以任务的最大响应时间来比较优化前后μC/OS-III中断管理机制的性能。

2.1 完全优先级剥夺原则

无论是μC/OS-III中断处理粒度较粗还是低优先级外设中断对紧急任务执行造成的干扰,一定程度上是μC/OS-III实时操作系统对外设中断的管理不到位造成的。因此,改进μC/OS-III中断管理机制,使其完全基于μC/OS-III优先级剥夺原则,可实现优先级的统一分配。

在系统任务设计时,将每一个IRQ分别对应ISR和IST。该IRQ以ISR或IST方式执行取决于当前正在执行任务优先级是否高于中断任务。

情况1中断任务低于当前执行任务的优先级则以IST方式执行。IRQ调用ISR并向对应的IST发送信号量,在IST得到信号量后处于就绪态,等待高优先级的当前执行任务结束后,再根据该IST任务和其他任务的优先级剥夺CPU使用权;

情况2中断任务高于当前执行任务的优先级,则以ISR方式执行。IRQ直接调用ISR并立即剥夺当前执行任务的CPU使用权。虽然这种情况会出现中断响应时间增加,以及紧急中断不能及时响应等传统中断管理模式的缺点,但是该模式可以满足高优先级ISR及时响应并尽可能减少中断任务对其他任务的干扰[12-15]。

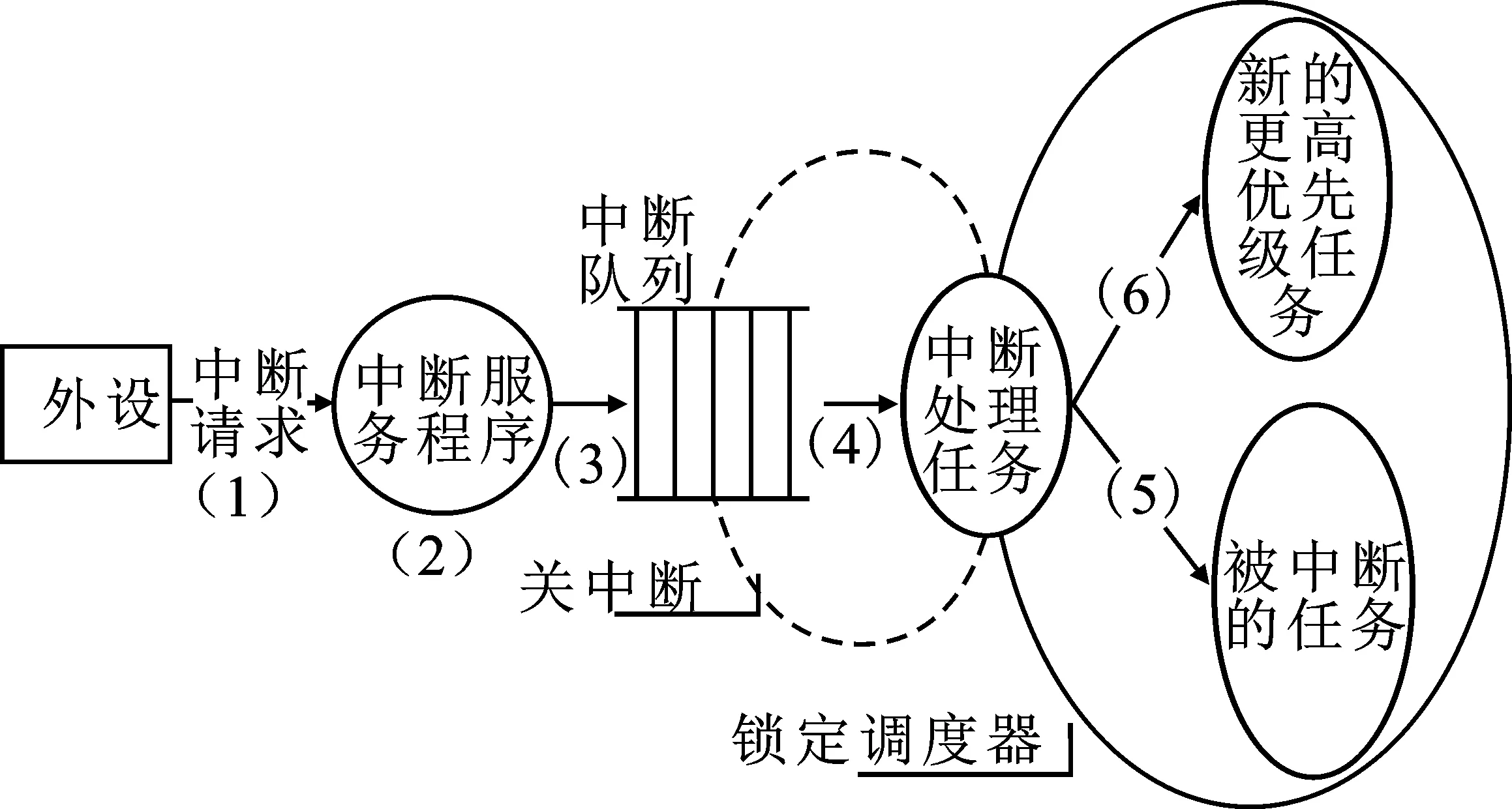

2.2 优化后中断处理过程

在尽量不更改内核代码的情况下进行过程优化,主要涉及正在执行任务优先级和中断任务优先级的获取和比较。优化后的中断模式处理如图3所示,具体过程为:(1)当中断发生时,首先获取此IRQ的ID,并通过此ID获取中断源。通过IRQ_Prio=INT_PRIO[ID]来获得中断任务优先级;(2)获取最高级别就绪任务的Prio,当中断发生时读取并赋值给Current_Prio;(3)比较判断IRQ_Prio与Current_Prio的优先级,优先级值越低优先级越高。中断以ISR执行还是以IST执行并不是一成不变的,具体要与当前正在执行的任务优先级比较。若IRQ_Prio的值大,则中断优先级越低,给对应IST发送信号量使其处于就绪态,反之则立即执行对应的ISR;(4)获取最高级别就绪任务Prio后赋值给Current_Prio并执行此任务,该任务可能是普通任务也可能是IST。

图3 优化后的中断模式处理流程图Figure 3. Flowchart of optimized interrupt mode processing

3 中断模式理论分析

由于高优先级IRQ比当前正在执行任务的优先级还高,产生后会立即执行,改进中断模式与μC/OS-III直接发布模式的任务响应时间一样,所以本文不做讨论。本文主要讨论在μC/OS-III中断管理模式下的低优先级IRQ,对比直接发布模式、延迟发布模式和改进后模式中任务最大响应时间,进一步验证改进后模式的优化效果。

3.1 直接发布模式中任务最大响应时间

在μC/OS-III中选择直接发布模式时的任务调度如图4所示。优先级较高的TASK2运行时发生IRQ1和IRQ2,并立即执行对应ISR1和ISR2。在ISR2运行后使TASK1处于就绪态,由于TASK2优先级比TASK1优先级高,执行完TASK2后任务切换执行TASK1任务。

图4 直接发布模式时任务调度Figure 4. Task scheduling in direct release mode

在直接发布模式下,TASK2任务的最大响应时间为

(1)

式中,Ti=ti+δ。Ti为TASK2执行时间总和,包括实际执行时间ti和任务切换时间δ;tISRm是IRQ2执行时间;α1是ISR2运行后使TASK1处于就绪态的时间;β1是进入和退出中断进行现场保护时间;m是执行任务过程中发生中断数目。

3.2 延迟发布模式中任务最大响应时间

在μC/OS-III中选择延迟发布模式时任务调度如图5所示,高优先级的TASK2运行时发生IRQ1,并立即执行对应ISR1,ISR1只向中断队列OS_INT_Q发送信号。随后中断处理任务OS_IntQTask就绪并以最高优先级立即运行,发布信号量或消息给对应任务TASK1使其处于就绪态。TASK2以较高优先级执行完后任务切换执行TASK1任务。

图5 延迟发布模式时任务调度Figure 5. Task scheduling in delayed release mode

在直接发布模式下,TASK2任务的最大响应时间为

(2)

式中,TISRm=tISRm+δ。α1是ISR1向中断队列OS_INT_Q发送信号时间;γ是中断处理任务OS_IntQTask发送信号使TASK1处于就绪态的时间;其他变量和式(1)中的变量相同。

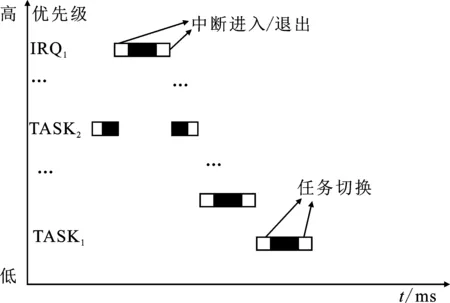

3.3 改进模式对任务最大响应时间

μC/OS-III改进模式的任务调度如图6所示。在TASK1执行过程中发生IRQ1,IRQ1仍会执行ISR1,但是主要以IST方式处理,IST处理后向低优先级的TASK1发送信号量或消息。

图6 改进模式时任务调度Figure 6. Task scheduling in improved mode

在改进模式下,TASK2任务的最大响应时间为式(3)。

(3)

由于IRQ1以IST方式处理,并且优先级低于TASK2,所以不会占用TASK2的执行时间,因此消除了ISR消耗tISRm时间。

(4)

(5)

式(4)和式(5)均大于0,验证了优化后的中断模式能够缩短高优先级任务TASK2的任务截止时间,也可以看出在3种模式中,优化后的μC/OS-III中断模式对任务响应时间最少。

4 实验与结果分析

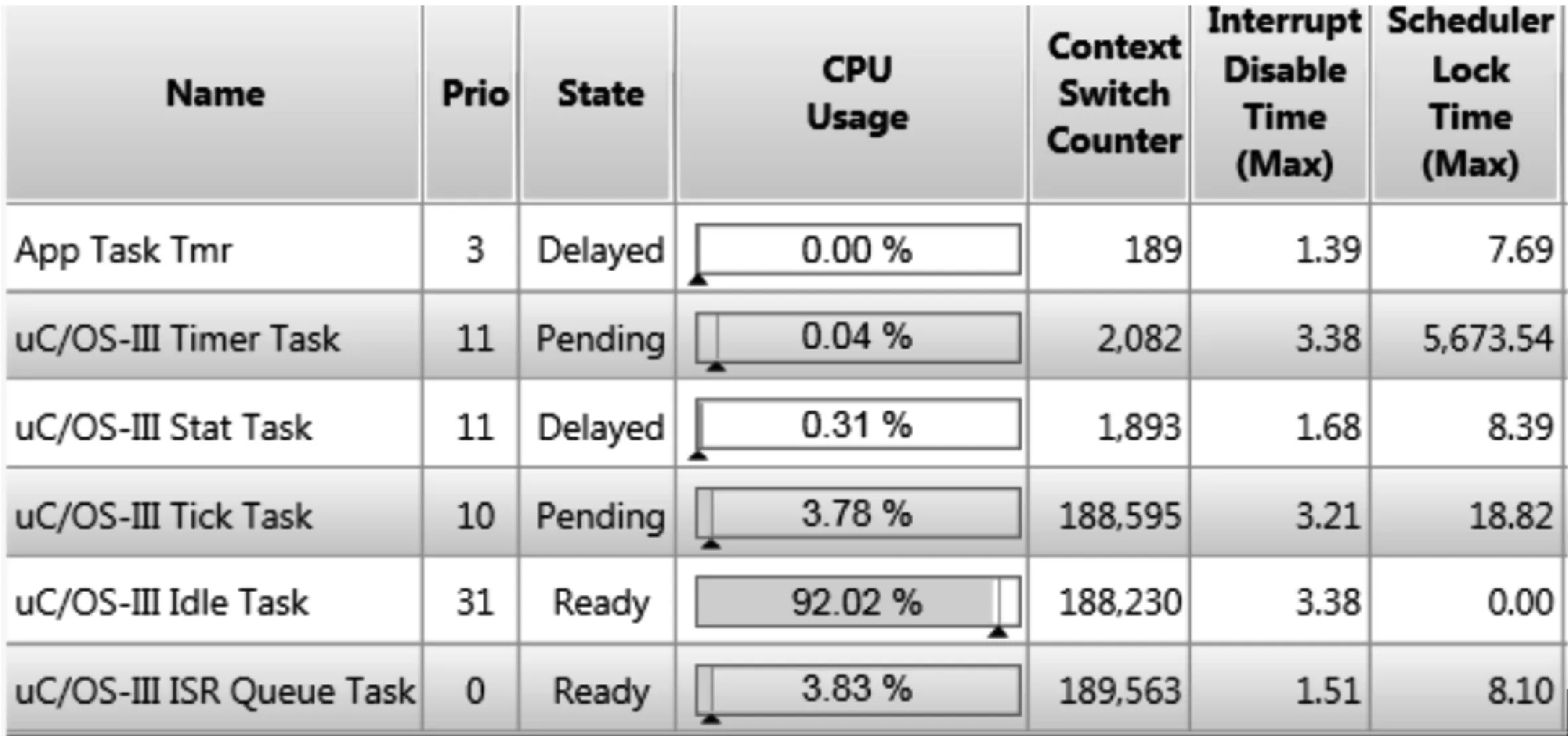

仿真实验使用带有ARM的STM32处理器,MUC选择高性能且低功耗,主频为72 MHz的Cortex-M3作为主芯片[16-17]。硬件Systick定时器为μC/OS-III提供时钟节拍任务,可根据应用任务要求更改时钟节拍频率,使频率至少是50 Hz,另外将频率设置为整数倍,此处为200 Hz。按照章节2.2对μC/OS-III部分内核进行修改[18-19],实现具体功能。实验主要讨论低优先级中断对紧急任务截止期的影响。

通过设计定时器任务和时钟节拍任务,可以得到周期性的中断信号。定时器任务优先级高于时钟节拍任务,一般都将时钟节拍任务设置成中等优先级。设置定时器任务执行周期为100 ms,任务执行期间可发生多个时钟节拍中断。

通过μC/Probe对系统运行检测,如图7所示,图中能够显示任务状态、任务优先级、切换频率和任务堆栈等。由图7可知,优化后的μC/OS-III实时操作系统能够稳定运行。由于高优先级中断为ISR立即执行方式,中断的及时响应减轻了CPU负载能力,改进后CPU利用率为28.32%,相较于直接发布模式和延迟发布模式降低了约5%,且随任务数量的增加优化效果会更加明显。定时器任务的切换次数和锁任务调度器时间明显减少,这是因为低优先级中断对高优先级任务的干扰有所减少。但是,最大中断关闭时间有所增加,也正是牺牲了低优先级中断任务的及时响应才换来了紧急任务的截止期缩短,不过对于一些特别紧急的任务,增加的时间是可被接受的。

图7 系统运行检测Figure 7. System operation detection diagram

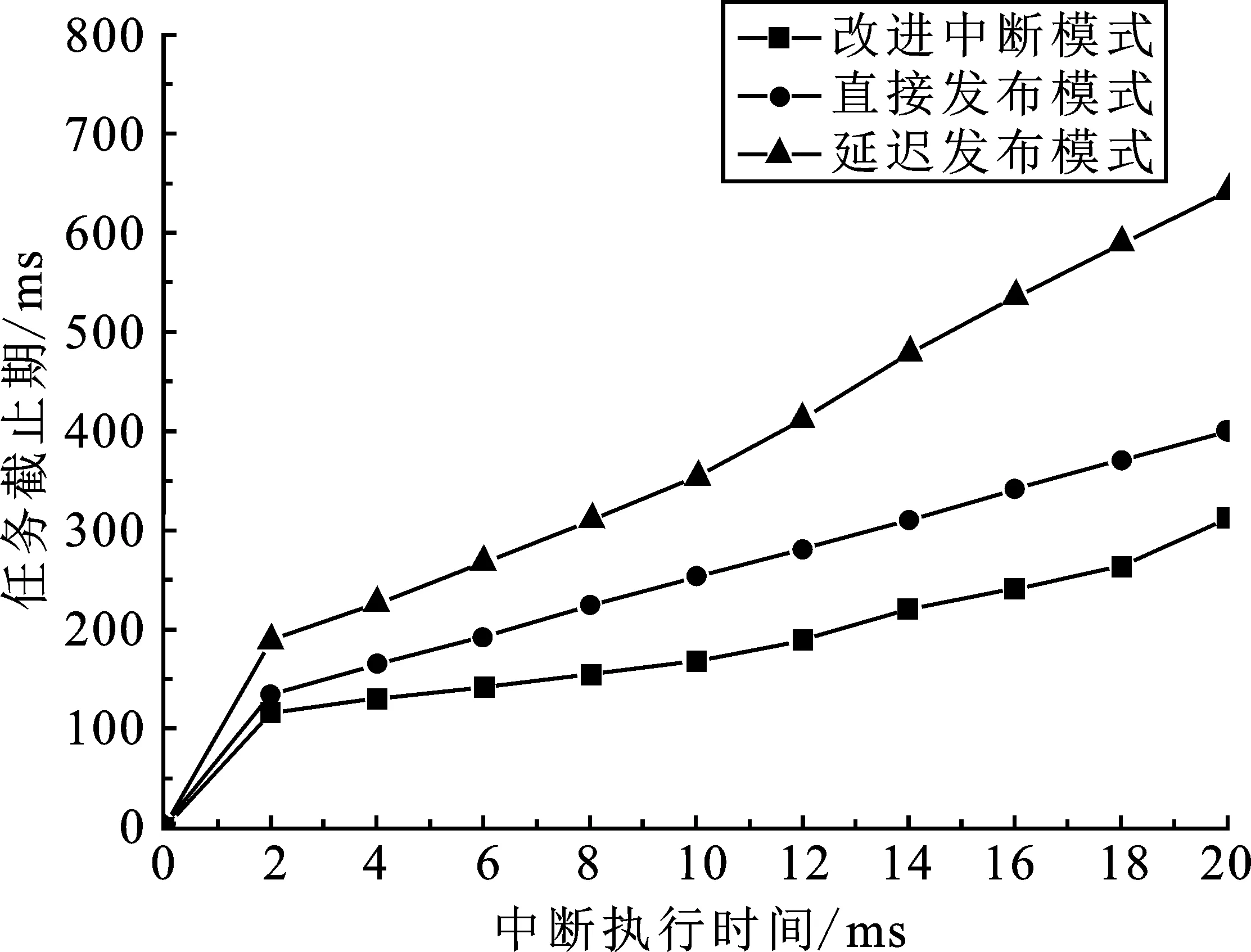

通过如图8所示的串口助手接收数据可知,对应3种中断模式下定时器任务截止期数值。直接发布模式和延迟发布模式中定时器任务随着中断执行时间的增加变化较大,这也要求中断ISR尽可能短小简单的原因。改进中断模式中的低优先级中断以IST任务执行,而IST任务优先级较低不会剥夺CPU执行权,对紧急任务的截止期没有影响,所以随着中断执行时间的增加变化并不大。

图8 紧急任务截止期数值Figure 8. Urgent task deadline value

5 结束语

本文通过3种中断模式理论分析以及实验与结果表明,中断任务和内核管理的普通任务在基于完全优先级剥夺原则下,可以使紧急任务的截止期缩短,降低优先级中断对紧急任务的干扰。虽然基于完全优先级剥夺更加符合任务优先运行的实际情况,但是改进中断模式会导致中断响应时间增加,并且可能造成中断的丢失。因此,后续工作应该优化中断对任务的影响,并进一步缩短中断响应的时间。