基于FPGA的数码喷墨印花系统

力雪梅,季诚昌,孙以泽

(东华大学机械工程学院,上海 201620)

数码喷墨印花对印花图片的数据处理速度、进布与喷头小车运动控制有较高要求。市面上的数码喷墨印花系统采用ARM 处理器处理印花图片数据,控制印花过程,效果较好,但处理速度较慢。因此需开发可满足高速印花数据处理与较好控制效果的系统架构。FPGA 为现场可编程门阵列,能解决定制电路不足的问题,克服原有可编程器件门电路数有限的缺点,使硬件易于操作,应用于数码喷墨印花系统时能简化系统结构。本研究以PC 机与FPGA 技术相结合处理印花图片与控制印花过程。

1 数码喷墨印花系统架构

数码喷墨印花首先将计算机或印前输入设备产生的彩色图文信息传递到喷墨设备,在计算机控制下计算相应的通道墨量,喷墨成像装置控制墨滴以一定速度由喷嘴喷射到承印物表面,最后通过油墨与承印物的相互作用,使油墨在承印物上再现稳定的图文信息[1]。数码喷墨印花系统整体架构如图1 所示。从计算机获取待印花图像,利用PC 机完成前期处理,生成可用于印花的图片数据格式,FPGA 控制板接收图像信息并控制印花喷头,驱动喷头与进布机构相互配合进行印花。

图1 数码喷墨印花系统的整体架构

为保证印花精度,需要保持喷头印花速度与进布速度同步。采用伺服电机控制进布,控制板根据印花速度和位置的反馈信号相应调整伺服电机的转速与印花速度匹配,完成打印。本系统主要通过设计FPGA 控制板的软硬件完成图像前期处理、数据传输与存储,控制喷头实时喷墨印花等,确保系统在喷墨印花过程中稳定、准确地还原印花图像,精准印花。

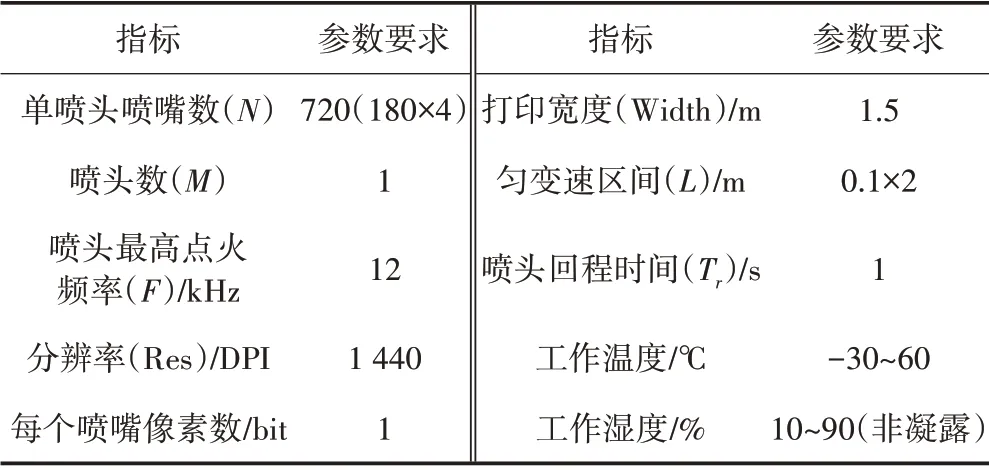

2 数码喷墨印花系统的需求

了解系统需求是系统设计的前提。由表1 可知,印花过程中,喷头在印花介质两端存在匀变速阶段,使喷头在开始印花时达到正常的喷印速度,结束印花时速度减慢,每个匀变速区间长度为0.1 m,因此每一行的匀变速区间长度=0.1 m×2=0.2 m。在一行印花数据喷印完成后,喷头需回程并开始下一行喷印,为了提高印花效率,应尽可能提高喷头的回程速度,缩短回程时间。不同印花系统因结构与控制方法不同,喷头回程时间不同。在本印花系统中,喷头回程时间为1 s,相比其他印花系统时间较短。喷头在匀变速区间及回程中不喷墨,只在匀速期间喷墨印花。

表1 系统喷印参数要求

数码喷墨印花系统设计主要体现在图片数据容量及数据传输速率两个方面。本系统用一个四色喷头进行印花,由表1可知,打印宽度(印花幅宽)为1.5 m,则一次扫描中,印花横向宽度计算式[2]如下:

本系统采用的印花喷头每列含有180 个喷孔,因 此单次印花所需内存空间计算式如下:

一个四色喷头一个印花行程所需内存空间计算式如下:

在实际印花过程中,为保证印花数据不丢失,数据传输与存储准确,系统选用的存储器应大于以上数值且有富余,便于日后系统的调试与升级。

在系统运行过程中,光栅频率应小于喷头最高点火频率F,因此,喷头小车匀速运动的最快速度(V匀速)计算式如下:

喷头在喷印单行印花图片时所需的时间(T单行)计算式如下:

印花图片处理系统需要在单行印花的9.96 s 内完成下一行印花数据的处理与传输,同时做好数据准备。因此,要确保印花数据的传输速度大于图片数据的输出速度,印花图片数据处理最低速度(Vs)的计算式如下:

在设计数码喷墨印花系统时,除了使系统满足以上图片数据容量及数据处理、传输速度要求外,还应使系统的运行具有较高的稳定性及可靠性。

3 硬件设计

在数码喷墨印花系统中,FPGA 模块的主要功能是利用USB 接口接收PC 机处理后的印花图片数据,并进行图像数据存储、读取等处理,然后将图像数据同步传输到印花喷头接口进行喷印,故FPGA 控制板的硬件模块设计主要包括对USB、DDR3 SDRAM、SPI FLASH 以及喷头驱动模块等的电路设计和整合。FPGA 控制板具体硬件结构框架如图2所示。

图2 FPGA 控制板硬件结构示意图

图2 中,SPI FLASH 为控制板上电时存储启动代码,上电启动后,喷墨印花图片数据通过USB 传输给FPGA 控制板接收器并缓存在DDR3 SDRAM 中,待印花小车达到某印花行时,通过FIFO 将该行印花数据输出给印花喷头,喷头驱动模块驱动喷头进行喷印处理,蜂鸣器与指示灯状态反应印花系统运行状态。

3.1 电源电路

电源的电路根据FPGA 控制板上各个模块以及芯片的具体需要设计。本系统选用的芯片主要包括FPGA 芯 片XC6SLX16、USB 芯 片CY7C68013A-56、DDR3 SDRAM 芯片MT41J64M16LA-187E 以及D/A转换芯片AD5424 等,供电电压分别为1.14~1.26 V、3.00~3.60 V、1.50 V、2.50~5.50 V,结合供电电压设计针对性的电源电路。

选用5 V 直流电源为电路板提供供电电压信号。通过电压转换芯片将5 V 直流电源转换成本系统芯片所需的1.5、3.3、1.2 V 等电压信号。选用MPS 公司的开关电源MP2143 实现电压转换,输入电压可以为2.5~5.5 V,最大能支持3 A的负载电流,开关频率可达1.2 MHz[3]。MP2143 有两个管脚(上电使能管脚EN、电压输出正常时指示管脚PG),通过对两个管脚的控制可以控制其上电时序,具体电压分配如图3所示。

图3 电源模块分配示意图

由图3 可知,以5 V 直流电源作为MP2143 输入电压,3.3 V_EN、1.2 V_EN 分别为3.3、1.2 V 电压信号的使能管脚,经MP2143 转换后,分别生成系统所需的1.5、3.3、1.2 V 电压信号。

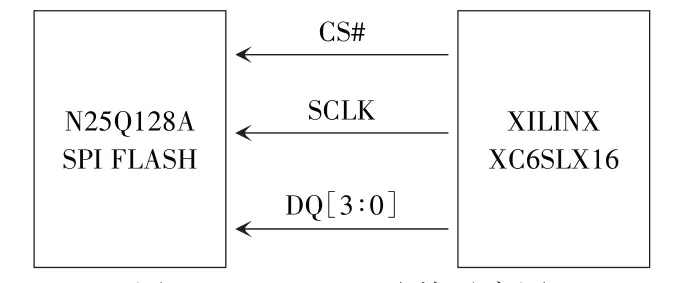

3.2 SPI FLASH

FPGA 控制板在上电启动时需要从外部存储来加载代码。本系统采用SPI FLASH 作为外部存储器,成本较低,电路设计也更加简单,但是读写速度比总线FLASH 慢[4]。本系统对FPGA 控制板的启动加载速度没有特定要求,因此选用成本更低的SPI FLASH 作为程序存储器。

FPGA 启动代码存储器采用N25Q128A FLASH芯片(Micron 公司),容量大小为128 Mb,最高可以支持108 MHz的时钟频率。N25Q128A SPI FLASH 与XILINX XC6SLX16 芯片的连接如图4 所示,通过对引脚的配置最终实现FPGA 从SPI FLASH 启动。

图4 SPI FLASH 连接示意图

3.3 喷头驱动

在实际的数码喷墨印花过程中,FPGA 控制板在接收PC 机预处理的图片数据后,同时产生两路信号,其中一路信号将喷印数据与控制命令发送给喷头接口模块进行印花,另一路信号为高压点火脉冲,但FPGA 控制板产生的信号为数字信号,需通过D/A转换芯片转换成模拟信号以输出印花喷头工作时所需的高压点火脉冲[5],数码喷墨印花系统的喷印喷头驱动控制电路模块构成如图5所示。

由图5 可知,喷印喷头的驱动控制电路模块主要由FPGA 模块、D/A 转换模块、功率放大器模块、喷头接口模块构成。其中,D/A 转换模块主要负责将FPGA产生、用数字串表示的高压点火脉冲信号转换成可被喷印喷头识别的模拟信号,再将该信号发送给功率放大器,最后将放大后的电压信号发送给喷印喷头进行点火印花。

选用芯片AD5424 作为系统D/A 转换芯片,适用于2.5~5.5 V 的电压环境,是8 位电流输出数模转换器(DAC),其转换后的输出信号为电流信号。系统选用压电式喷印喷头,因此,选用驱动能力较好的SN10501芯片能将电流信号转换成电压信号。AD5425 型D/A转换器功能图如图6所示。

图6 D/A 转换器功能图

图6 中,IOUT1代表经D/A 转换器转换后输出的电流,IOUT2一般连接系统的模拟地,GND 代表接地引脚,RFB表示反馈电阻的接入引脚,VDD表示输入引脚的供电电压,VREF为输入的参考电压,DATA INPUTS 为数据输入端口,DB0~DB7 为数字输入端口,单极代码表如表2所示。

表2 单极代码表

表2 反应了数字输入编码与对应输出电压间的关系,喷头点火脉冲信号经D/A 转换器转换后生成模拟信号,但高压点火脉冲波形功率较小,达不到驱动喷头点火所需的规定值,因此需将信号发送给功率放大器模块放大。用OPA548 型功率放大器,可接受的单端供电电压为8~60 V,可输出较宽的电压波动。

4 软件设计

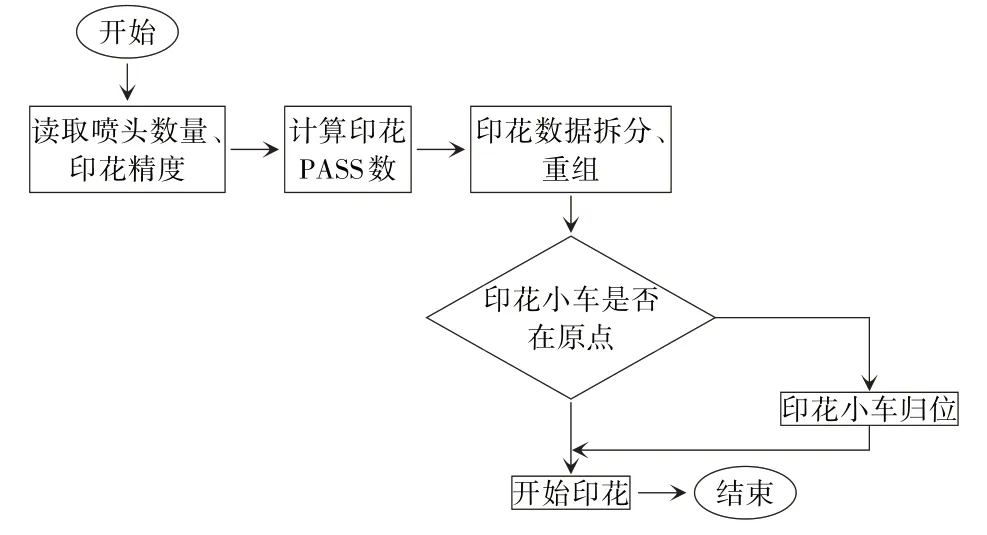

数码喷墨印花系统的软件实现主要包括印花图片的数据处理及印花过程控制。印花过程控制包括读取印花图片信息、设置印花参数,根据印花参数对图片进行数据处理、设置印花起始点,接收单次印花行程数据后进行X 方向的点火印花,完成该印花行程后进行Y 方向的进布操作,再进行下一行程点火印花。具体控制过程如图7所示。

图7 印花控制过程

印花图片数据处理过程如图8 所示。开始印花时,读取喷头的数量及印花精度要求,按照读取数据计算印花PASS 数,根据计算结果对印花图片数据进行拆分、重组,生成印花喷头能识别的点阵信息[6],调整喷头小车的位置开始印花。

图8 印花图片数据处理过程

在某一行印花行程中,读取该行的印花数据需通过FIFO 模块保证印花图片数据的发送与印花进程同步。本系统采用XILINX 公司的FPGA 芯片,其内部提供大量的存储资源,通过这些存储资源可生成FIFO存储逻辑,进行深度以及位宽配置[7]后,利用ISE 开发平台的IP 核生成项设计异步FIFO 模块,生成FIFO模块示意图如图9所示。

图9 FIFO 模块接口示意图

设置好FIFO 模块后,对其读写操作进行仿真验证。选用的印花喷头每列含喷孔180 个,一次印花数据量为180×8 bit,因此,在进行位宽为16 bit 的写操作时,为保证写入数据量与一次印花数据量同步,将可编程满信号prog_full门限定义为90(写入数据达到90)时有效,此时不能再对FIFO 模块进行写操作。对FIFO 模块进行写数据仿真,结果如图10所示。

由图10 可知,在对FIFO 模块进行写入数据时,写入使能置一,当数据量达到prog_full 的门限值90(一次印花数据已全部被写入)时,prog_full 值被置1,不能再对FIFO 模块进行数据写入操作,保证一次印花数据大小与实际印花所需大小相同。

图10 FIFO 模块写数据仿真

由图11 可知,在读使能rd_en 被置1 后,对FIFO模块进行读取数据操作,同时,代表可读数据量的rd_data_count 值也在减小,直到将FIFO 内的数据全部读出为止。

图11 FIFO 模块读数据仿真

5 实验验证

基于本文设计的数码喷墨印花系统,在完成整体设计后对整个系统进行实验验证,测试其运行过程,分析其印花效果。影响最终印花质量的因素有很多,例如印花时室温较低、喷墨墨管不干净、保养不当、印花数据丢失等都会影响最终印花效果。针对上述情况,清洗印花机的喷墨管,对出现堵塞的喷头进行吸墨清洗,以保证印花环境适宜,印花实验结果如图12 所示。由图12 可知,各测试线条均排列整齐,未出现断裂、错位及消失等缺陷,且印花线条连续,印花不缺失,印花质量较高,由此可推断,在印花过程中,各喷孔喷墨顺畅并无堵塞。

图12 喷嘴状态测试条

在保证各喷嘴状态良好的情况下,还需对喷头平行度进行测试,主要是为了保证在水平方向上,喷头与喷印小车的导轨保持平行,否则会导致同一行喷嘴的不同颜色不在同一直线上,影响最终的印花质量。喷头平行度测试条如图13 所示,当喷头与喷印小车的导轨不平行时,黑色与红色线条不在同一直线上,此时可以调节喷头架上的微调器,直到在同一直线上为止。

图13 喷头平行度测试

完成以上测试后对喷墨印花机进行整图印花测试,结果如图14 所示。印花图片宽幅1.5 m,印花精度360×720 DPI。从印花结果可以看出,该数码喷墨印花机可以满足工业生产需求。

图14 印花机整图测试

6 结语

印花图片的数据处理以及印花过程控制影响最终的印花质量,因此要求印花图片的数据处理系统能够准确、快速地对印花图片数据进行拆分、重组,最终生成可供印花的图片数据的点阵信息形式。针对印花过程中的数据处理与控制过程进行基于FPGA 的软硬件设计,并对相关模块进行仿真分析。调试与实验验证表明该喷墨印花系统可对图片数据进行高效传输,并且能准确地用于印花工作。