集成电路检验/失效分析过程芯片去层制备方法

汪小青,虞勇坚,马 勇,刘晓晔,吕 栋

(中科芯集成电路有限公司,江苏无锡214035)

1 引言

集成电路的芯片制造过程是通过掩模、光刻、离子注入、气相沉积、电镀、化学机械研磨(CMP)、腐蚀等多达几十、上百道工序,在硅衬底表面生长出有着特定逻辑功能的物理图形,这些物理图形从材质上包括Al、Cu、Ti、TiN和W等金属材料,以及单晶Si和多晶Si、SiO2和Si3N4等非金属材料[1]。

集成电路在制造、试验和应用过程中不可避免地会因为制造工艺、测试和环境应力、用户使用、寿命损耗等各种因素发生失效[2]。失效分析工程师需要通过各种方法定位失效位置,查找失效原因,剖析失效机理,在失效分析过程中需要对失效的集成电路进行去层解剖分析。芯片去层制备是在了解集成电路芯片制造工艺的基础上,采用化学腐蚀、机械研磨、离子刻蚀等技术手段逐层去除芯片各物理层次结构的过程。

在GJB548B-2005《微电子器件试验方法和程序》方法2018.1“扫描电子显微镜(SEM)检查”3.3节“样品准备”中规定:“适用时,应采用不损伤其下层待检查的金属化层的腐蚀工艺(如化学或等离子腐蚀)去除芯片表面的玻璃钝化层。”GJB4027A-2006《军用电子元器件破坏性物理分析方法》和GJB5914-2006[4]《各种质量等级军用半导体器件破坏性物理分析方法》4.3.5.4节“扫描电子显微镜(SEM)检查”中,均将样品制备的方法指向GJB548B-2005中的相应章节。在GJB3233-98[2]《半导体集成电路失效分析程序和方法》5.2.12和5.3.1.2.5节概要性地给出了去除钝化层和PN结染色的方法。在以上标准中仅给出了对检验分析样品的制备处理要求,并未提供具体的处理方法。除个别商业公司外,国内检测机构很少具备集成电路芯片去层制备能力,并且因为商业秘密保护,可查询获取的相关资料很少,这就使得检测机构在开展检验试验或失效分析过程中缺乏参考依据,使得标准的相应内容缺乏可参考和可操作性。本文对集成电路芯片的物理层次进行了解剖分析,选用实际产品制备满足检验要求和失效分析的各物理层次,样品制备方法可以对GJB548B-2005、GJB4027A-2006以 及GJB3233-98进行补充,使其具有可操作性。

2 芯片的物理层次结构

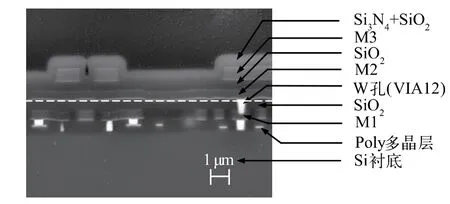

芯片的物理层次结构从表面往下通常包括玻璃钝化层(一般由Si3N4+SiO2构成)、所有金属化层(Al或Cu)、所有的中间介质层(一般为SiO2及其包裹的通孔或接触孔)、多晶(Polysilicon,一般简称Poly)层以及有源区层(衬底,大多为P型)。对于一个具有N层金属布线的芯片来说,样品制备过程中通常可以获得N+2个用来观察的物理层次,即N个金属层、1个多晶层和1个有源区层。

在获取用于观察的物理层次时,需要选定一个合适的解剖层面,以保证样片图像中能够同时观察到多个层次信息。图1为一个具有3层金属、双层多晶的集成电路芯片纵切面照片,当需要观察第一层金属(M1)及以下层次时,应在去除M2层后停止(图中虚线位置),保留M1层上方的SiO2层和M1、M2层之间的通孔(W孔)。此时在光学显微镜下可以同时观察到M1层、W孔(VIA12)及以下其他层次,这有助于判别失效发生的具体层次。

图1 具有3层金属布线的芯片物理层次结构(纵向切片)

3 去层制备方法

集成电路芯片的去层制备过程包括对表层玻璃钝化层的去除、金属化层的去除、阻挡层的去除、中间介质层的去除、底层多晶层的去除和有源区的制备。根据制造工艺和材料的差异,可以选用离子刻蚀、化学腐蚀和机械研磨等方法。

3.1 离子刻蚀法

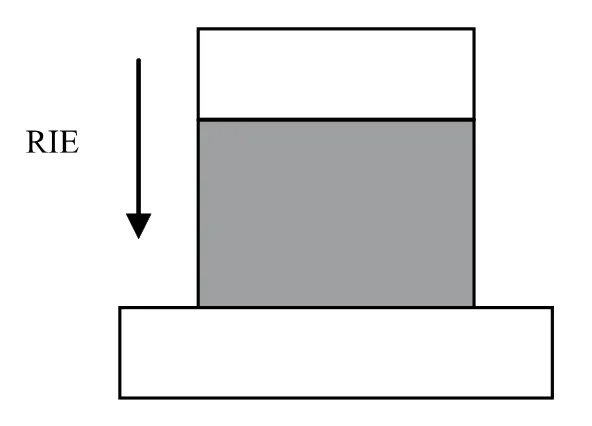

离子刻蚀一般称为干法刻蚀[3],去层制备过程最常用的是反应离子刻蚀(RIE),RIE的原理是辅助刻蚀气体(如CF4、SF6)在工作腔体内电离后,在电场作用下与被刻蚀样品之间发生的物理化学过程。RIE因气体流量与腔体压力不同,刻蚀效果可以是各向异性也可以是各向同性的。各向异性刻蚀使同一种材料沿单一方向均匀刻蚀(一般为平行电场方向),并因刻蚀气体的选择对不同材料具有不同的刻蚀速率,RIE较高的刻蚀选择比能够保留所需要的关键层次和图形,见图2。

图2 RIE各向异性刻蚀

在去层制备过程中,去除集成电路芯片表面的玻璃钝化层和中间介质层推荐选用离子刻蚀,这些层次的材质一般为Si3N4、SiO2。对于具有多层金属化层的集成电路芯片,各层介质层的离子刻蚀时间可以通过介质层厚度与离子刻蚀速率之比计算获取。

3.2 化学腐蚀法

化学腐蚀又称为湿法刻蚀[9],是通过化学溶剂与芯片表面的材料之间发生的化学腐蚀反应,生成可溶性物质或气体,达到去除芯片表面材料的目的,原理如图3所示。

图3 湿法刻蚀原理图

影响化学腐蚀速度的因素主要有4个[5]:溶液浓度、反应时间、反应温度和溶液搅拌方式。高的溶液浓度、反应温度和溶液搅拌可以加快化学反应速度,但过快的腐蚀速度会发生严重的“底切”“钻蚀”现象[6],导致难以控制腐蚀过程和终点,这就导致化学腐蚀法的应用局限性大大增加。

化学腐蚀法去层一般用于去除具有终点自停止的层次,例如去除具有阻挡层和W通孔的Al金属化层。

3.3 机械研磨法

机械研磨去层法是3种去层方法中相对稳定的1种,是通过研磨机、研磨剂和抛光垫对芯片表面逐层去除的方法。相对于离子刻蚀和化学腐蚀法,机械研磨法具有更高的可控性,机械研磨法的另一个优点是检验和分析人员能够在观察过程中很好地识别区分层次,因处理后与上层金属化层之间的通孔(W)呈现显著的亮白色,而下层通孔(接触孔)呈现暗色。

但是由于机械研磨法是同步去除芯片表面各区域和各类材料,并且局限于人工操作,对个人的技术要求更高。对于深亚微米芯片,金属布线的材料、层数、线宽等是制约研磨去层通用性的因素。

4 去层制备试验

本文以某型号集成电路芯片为例进行样品去层制备试验,该芯片具有3层铝金属化层,双层多晶、0.35 μm工艺制程,玻璃钝化层材料为Si3N4+SiO2的复合结构。

4.1 玻璃钝化层的去除

玻璃钝化层作为芯片表面的保护层,一般为Si3N4层和SiO2层的双层次结构。推荐选用离子刻蚀(RIE)去除玻璃钝化层,常见的辅助刻蚀气体为CF4和O2的混合气体,CF4对于SiO2和金属铝的刻蚀具有高选择比,可以快速刻蚀SiO2而保留金属铝。经验值为当射频功率为80 W、CF4∶O2配比为2∶1、气压为15 Pa的情况下,刻蚀时间选择3~5 min即可完全去除玻璃钝化层。

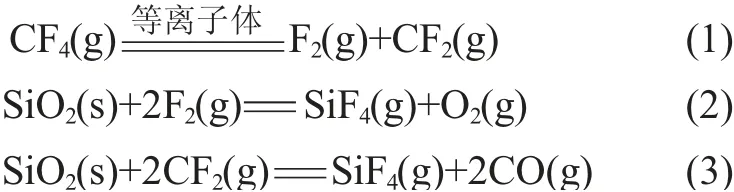

反应化学过程见式(1)~(4)[7]。

在CF4的等离子体中加入少量O2,氧原子与CF4反应生成CO、CO2以及少量COF2,将消耗掉等离子体中的C原子,可以大大增加F原子浓度,从而加快对SiO2的刻蚀速率。

以图1中的样品为例,本次试验中顶层Al金属化层(M3)去除玻璃钝化层前后的照片见图4,去除玻璃钝化层后M3裸露呈现亮白色。金属化层之间的介质层成份一般为SiO2,介质层的去除可以同样采用离子刻蚀法。

图4 钝化层图像(左)与去除钝化层后的图像(右)

4.2 金属化层的制备和去除

金属化层的制备和去除分为Al和Cu两种金属化层的制备和去除。

对于采用铝作为金属化层的集成电路,推荐采用离子刻蚀法去除玻璃钝化层(Si3N4+SiO2)和金属化层中间的SiO2介质层后,再通过以下两个步骤完全去除金属化层。以图1中案例为代表说明制备和去除M2层、M1等中间金属化层的步骤。

4.2.1 化学腐蚀

图4 的案例通过离子刻蚀暴露出顶层Al金属化层(M3)后,可以采用化学腐蚀法去除金属化层,腐蚀液一般采用商品铝腐蚀液或者稀释后的30%硫酸(H2SO4)或30%盐酸(HCl),以上腐蚀液均可有效去除Al而不腐蚀SiO2介质层,Al与盐酸反应的化学方程式为[6]:

反应过程中产生的气泡会附着在铝的表面,有可能局部抑制刻蚀的进行,造成刻蚀不均匀,可以在反应过程中通过增加搅拌或震动来避免或减轻刻蚀不均匀的问题。当M3层的金属Al完全腐蚀后露出下方的Ti/TiN阻挡层时自动停止。

4.2.2 研磨去层

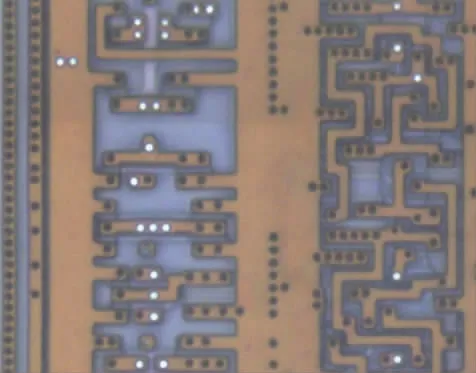

阻挡层的材质一般为Ti/TiN,去除阻挡层可以采用离子刻蚀也可以采用机械研磨法,推荐采用机械研磨法去除阻挡层,图5为光学显微镜(OM)下0.35 μm制程的芯片M1金属化层的研磨法制备效果图。

图5 0.35 μm工艺M1层图像(OM)

对于0.18 μm以下采用Al或Cu工艺制程的集成电路芯片,一般全程采用机械研磨法制备中间所有的层次,当需要通过扫描电子显微镜(SEM)观察Al或Cu金属化层表面损伤或异常形貌时,则在去除上层金属化层后,采用低氧或无氧离子刻蚀去除SiO2介质层直至下层金属化层裸露,经表面蒸镀导电材料后在SEM中进行失效位置观察和识别。图6为0.18 μm工艺制程金属化层制备的SEM实际效果图。

图6 0.18 μm工艺M1层图像(SEM)

4.3 多晶硅层的制备和去除

集成电路芯片上的多晶硅层一般用来制备CMOS管的栅极、电阻或者电容的极板。多晶硅层的制备推荐采用化学腐蚀法配合机械研磨法,化学腐蚀法去除金属化层(M1),机械研磨法去除金属化层下的阻挡层,可以保证多晶层和接触孔的制备效果。图7为集成电路芯片内部的多晶层数字单元照片,要求制备后的多晶栅极边界、接触孔、有源区边界等关键位置无损伤、易区分。

图7 多晶硅层制备效果图

多晶硅层的去除主要采用化学腐蚀法,利用稀氢氟酸(HF)溶液进行刻蚀,反应过程为:HF将多晶硅层上下的SiO2介质层腐蚀掏空,多晶硅从芯片表面自然掉落去除,刻蚀速率可通过氢氟酸与去离子水的比例来调整。其化学反应方程式为[7]:

4.4 有源区层的制备

CMOS集成电路的数字单元是由PMOS管和NMOS管耦合组成,对于P型衬底硅集成电路,NMOS管直接在衬底上生长,而PMOS管则生长在N型阱内。在样品制备过程中,有源区层可以通过PN结染色法来制备,可以区分出P型衬底、PMOS管、NMOS管、N阱区边界。这是由于PN结染色液对P型注入区刻蚀较快并腐蚀出微孔洞,微孔洞产生光陷阱效果而呈现深色,而N型注入区由于刻蚀速率慢、表面保持光滑而呈现出白色,两者之间对光照呈现显著的反射率差异,造成颜色上的反差[8]。

GJB3233-98《半导体集成电路失效分析程序和方法》第5.5.1.2.5磨角染色中给出了PN结染色显示液的配方,见表1。

表1 PN结染色方法

实践证明Cu染色液配方在操作过程中不易控制,推荐采用Dash腐蚀液配方可以获得更好的染色效果,通用性也更好[6]。

实际上,PN结染色技术不仅可用于判断CMOS管和阱区边界,还适用于P-、P+和N+等轻、重掺杂浓度区域的定性判断。PN结染色技术同样适用于模拟元件的区分和提取,例如PNP晶体管、NPN晶体管和阱电阻识别。图8给出了数字单元有源区的阱及MOS管的染色效果。

图8 有源区PN结染色制备效果图

综上所述,在芯片去层制备方法中,离子刻蚀法适用于去除玻璃钝化层(Si3N4+SiO2)和金属化层中间的SiO2介质层,机械研磨法适用于金属化层和阻挡层的去除;多晶硅层的制备推荐采用化学腐蚀配合机械研磨法,PN结染色推荐选用Dash腐蚀液进行刻蚀。

5 总结

本文探讨了集成电路芯片内部各层次的去层制备方法,为满足集成电路检验和失效分析对芯片内部各层次的制备需求,分别从玻璃钝化层去除、金属化层制备与去除、多晶层制备与去除、有源区染色4个方面提出了具体的制备方法,通过实例说明了选用离子刻蚀、化学腐蚀和机械研磨法的物理层次、材料和试验条件。本文的成果为GJB548B-2005、GJB4027A-2006以及GJB3233-98中相应检验和分析过程提供了具体实施方法,有助于推动标准中相应条款的实际应用。