Ka 波段频率源建模分析与设计*

江润东,姚金杰,姬娜娜,李嘉浩

(中北大学 信息探测与处理山西省重点实验室,山西 太原 030051)

0 引言

在固定频率多普勒雷达体制的Ka 波段交会参数探测单元中,高频率发射信号的产生对系统极为重要。输出信号要求功率高、相噪低。通常为了获得低相噪的输出信号,常常采用锁相环与直接数字式频率合成器(Direct Digital Synthesizer,DDS)混合使用的方式,这样可以实现很低的相噪[1-2]。但是由于本文是对于需要小型化的交会参数探测单元,这样的方式显然并不适用,在这样的情况下,低相噪不得不对小型化做出让步。本文使用锁相环输出与倍频相结合的方法[3-4],通过对锁相环进行建模分析,对锁相环的参数进行了分析确定,最后设计制作了一个Ka 波段的频率源,并完成了对频率源的调试。

倍频频率源通常的产生方式通常为对锁相环或者DDS 的输出信号进行倍频。对于锁相环的设计,现在通常采用软件设计直接给出锁相环的参数[5-7],对于这样的设计方法,在课题组的几次设计中使用芯片公司软件给出的电路参数进行设置,发现锁相环容易失锁,使用示波器观察环路滤波器的输入信号发现为一频率稳定的正弦波,锁相指示信号仅在上电最初的时候给出环路锁定的信号。针对环路失锁的现象,本文针对锁相环的各个部分建模,对环路进行定性分析,最后使用锁相环输出倍频方式实现稳定Ka 波段信号输出。

1 频率源建模分析

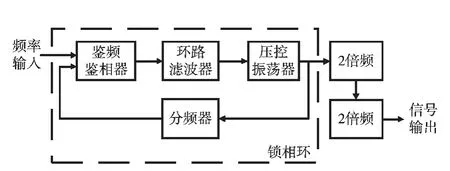

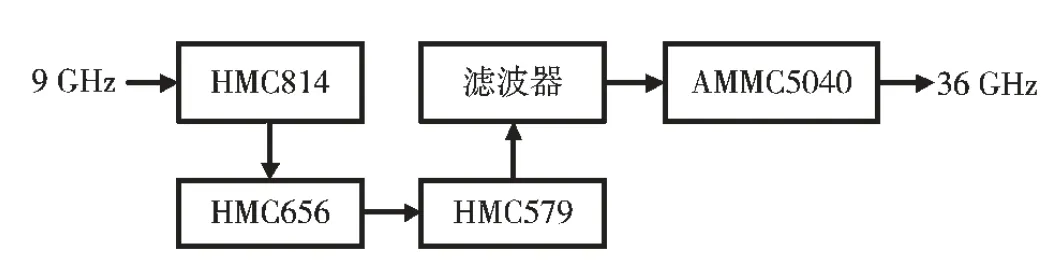

在对晶体管单管振荡、DDS 以及锁相环比较之后,由于小型化和较高的频率输出要求,决定采用锁相环作为基频信号的产生。结构如图1 所示。

图1 频率源结构框图

使用锁相环LMX2594 输出9 GHz 固定频率低相噪信号,然后使用两次二倍频,分别将9 GHz 倍频到18 GHz和36 GHz。

锁相环从结构上主要分为外部参考频率源,即晶振、鉴频鉴相器、环路滤波器、压控振荡器和分频器5 部分,已在图1 中虚线框内标出[8]。

锁相环的频率输入通常使用晶振输入,也有使用DDS的输出作为锁相环的输入,以求获得更低相位噪声的频率输出。鉴频鉴相器的作用是将锁相环的输出分频后的信号与系统的输入信号进行相位的比较,然后输出一个带纹波的直流信号。环路滤波器尽量将该信号中的交流成分滤除,从而获得稳定的直流信号作为压控振荡器的输入信号,最后得到稳定的频率输出。分频器的作用是将输出信号分频到尽量与输入信号同频的信号,以方便鉴频鉴相器进行比较。

整个系统为一负反馈结构,当输出信号稳定后,输出信号经过分频后的信号与输入信号保持恒定的相位差,以至于压控振荡器的输入信号为一稳定直流信号。这样的系统就能保持输出信号频率的稳定,并且在输出信号出现偏差后具有一定自动调节的能力。

1.1 鉴频鉴相器

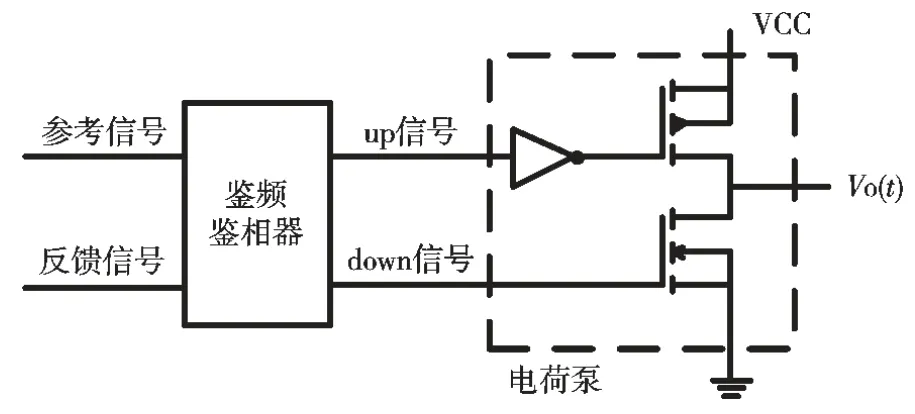

鉴频鉴相器通常为数字式,由两个D 触发器、与门和延时部分构成[9];电荷泵鉴频鉴相器简化原理图可以看成是参考信号和反馈信号两个信号分别控制2 个MOS 管的通断,来实现对电容的充放电,如图2 所示。

图2 电荷泵鉴频鉴相器

对图2 所示的框图的输入与输出的时序图进行分析,分别为参考信号超前和参考信号滞后两种情况。在参考信号和反馈信号都为低电平时up 和down 信号以及输出的电平为,即高阻态[10-11]。

对于图2 所示的简化电荷泵鉴频鉴相器,以参考信号滞后的情况为例,输出电平为:

式中,t2-t1为参考信号和反馈信号的时间差,θ 表示两个信号的相位差。将上式用电流的形式进行表达,如下式所示:

式中,Ip为电荷泵电流,Id为电荷泵输出电流。于是电荷泵鉴频鉴相器的增益可以表示为:

1.2 环路滤波器

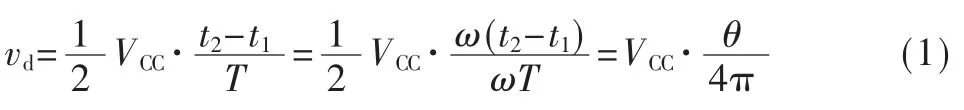

环路滤波器的本质是低通滤波器,用于给压控振荡器(Voltage-Controlled Oscillator,VCO)提供低纹波直流控制信号,以使得压控振荡器产生低相位噪声信号。环路滤波器的带宽影响着环路的锁定时间和信号的相位噪声。带宽越宽,锁定时间也越长,输出信号的相位噪声也越大;反之,带宽越窄,锁定时间越长,输出信号相噪越小。需要在二者之间找到一个平衡点。图3 为TI 公司官方软件提供的4 阶环路滤波器原理图。整个滤波器网络为一电阻性低通滤波网络。

图3 4 阶环路滤波器

对图3 所示的环路滤波器进行分析,在C1、C2、R2节点上的电压在复频域上可以表示为[12]:

环路滤波器的传递函数可以表示为:

由式(6)可以看出这是一个电阻性的滤波网络。

1.3 压控振荡器

压控振荡器振荡器根据控制电压的大小输出对应频率的信号。压控振荡器的输入输出关系可以表示为:

式中,△ω 为相位变化率即频率,θv(t)为瞬时相位,Kv为压控振荡器的压控增益,单位为MHz/V,通常由芯片手册中给出;vc为压控振荡器控制电压。对式(7)两端进行拉氏变换,得到压控振荡器的传递函数为:

1.4 分频器

分频器在锁相环中的作用为将输出信号分频,然后将信号送至鉴频鉴相器同输入信号的相位进行比较。根据输入输出关系有:

式中,N 为分频系数,ωi为输入频率,ωo为输出频率。则分频器的传递函数可以表示为:

1.5 环路特性

由上面的分析,对系统闭环回路进行分析,有:

式中,θe为相位差,有:

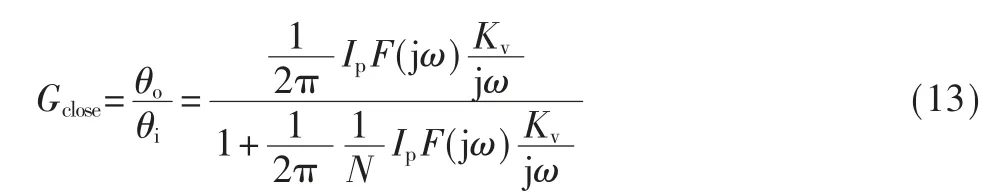

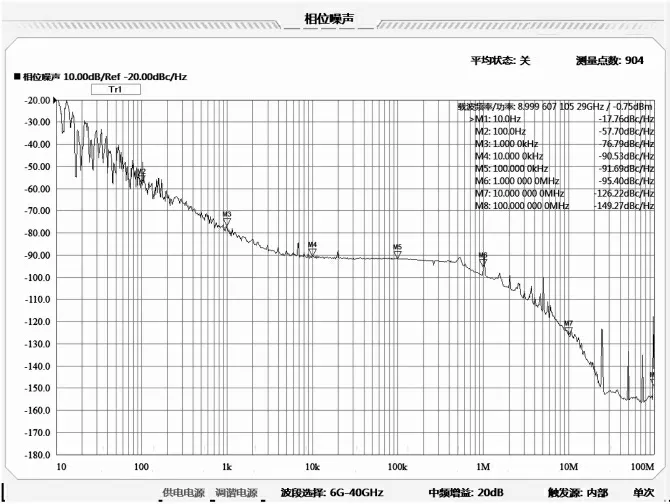

将式(11)、式(12)联立,可以得到频域形式的闭环增益为输入输出相位之比,即:

根据负反馈放大器的环路幅频和相频特性发现,当式(13)右边项的分母为0 时会出现闭环增益无穷大的情况,负反馈会变成正反馈,从而导致锁相环失锁。闭环回路产生正反馈的临界条件为:

为了使锁相环保持稳定,需要对系统的幅频和相频特性进行修正。

2 X 波段频率源设计改进

2.1 系统分析

首先对X 波段频率源进行设计。在引言中已经提到,现在存在的问题是使用TI 的软件给出的环路滤波器参数设计电路会产生短暂锁定后失锁的情况。根据式(14)从系统角度对原因进行分析。

环路的目标输出信号频率是9 GHz,使用到的VCO核为VCO2。根据手册上的经验公式,估算出在9 GHz 处VCO 的增益为:

式中,f1、f2、KVCO1、KVCO2分别为该VCO核在工作的起始和终止频率以及在该频率上的VCO 增益。

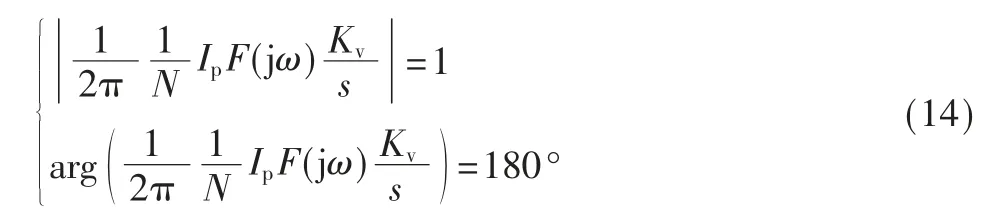

按照芯片手册中推荐的图3 所示的环路滤波器的参数,系统其他参数为:Icp=15 mA,分频器分频系数为N=360,鉴频鉴相器的频率为25 MHz。根据这些参数绘制出系统的幅频和相频特性曲线,如图4 所示。

图4 系统的幅频和相频响应

从图4 中可以看出,环路的相位裕度为25.94°。通常来说,闭环控制系统的相位裕度至少要有45°,这样的系统才不容易发生相位翻转。所以在之前提到的锁相环容易出现失锁的情况有可能就是由于相位裕度不够造成的。增大系统相位裕度能够使锁相环更稳定。

2.2 改进方案

对于本设计,即X 波段频率源来说,根据频率源的闭环传递函数,可以改变的参量有电荷泵电流Ip、环路滤波器的传递函数F(s)和分频器的分频比,其中修改分频比需要对输入信号频率进行修改。通过对这些参数的调节来对系统的增益和相位信息进行改善,本文主要采用对环路滤波器进行修改的方式来实现。

根据图4 中的相位下降速度来看,相位下降速度较快,对于低通滤波器带外的相位,滤波器的阶数越高,带外相位下降速度越快。这样可以通过将环路滤波器的阶数降低的方式来减缓相位降低的速度,从而达到提高相位裕度的目的。

将环路滤波器换成二阶滤波器之后,即修改分频比和去掉图3 中R2、R3、C3、C4,其他参数保持不变,鉴频鉴相器的频率改为100 MHz,然后在MATLAB 中重新仿真,仿真得到的数据较之前有较大改善,如图5 所示。图中,P2 和P1 两点分别为增益为0 的点和增益为0 的点对应的相位。该环路的相位裕度约为63.524°,对于工程应用来说,该相位裕度能够满足需求。

图5 改进后的环路幅频和相频特性曲线

2.3 改进设计结果及分析

在完成之后,对实物进行改进和测试。实物中,使用的晶振为25 MHz 温补晶振,标称频率误差1~2 ppm;使用的基板为RO4350,板厚0.254 mm;锁相环由单片机通过模拟SPI 总线进行控制。在测试时,当单片机对锁相环的初始化完成之后,锁定指示一直为高电平,说明锁相环实际工作时能够稳定锁相。

对X 波段频率源输出的频谱进行测试得到的结果如图6 所示,使用是德N9010A 信号分析仪利用探针对输出进行测试,测得信号的功率约为-2 dBm,在Ka 波段使用探针进行频谱测试的衰减约有5 dB,实际输出功率约3 dBm,达到设计需求。

图6 改进后的锁相环输出信号频谱

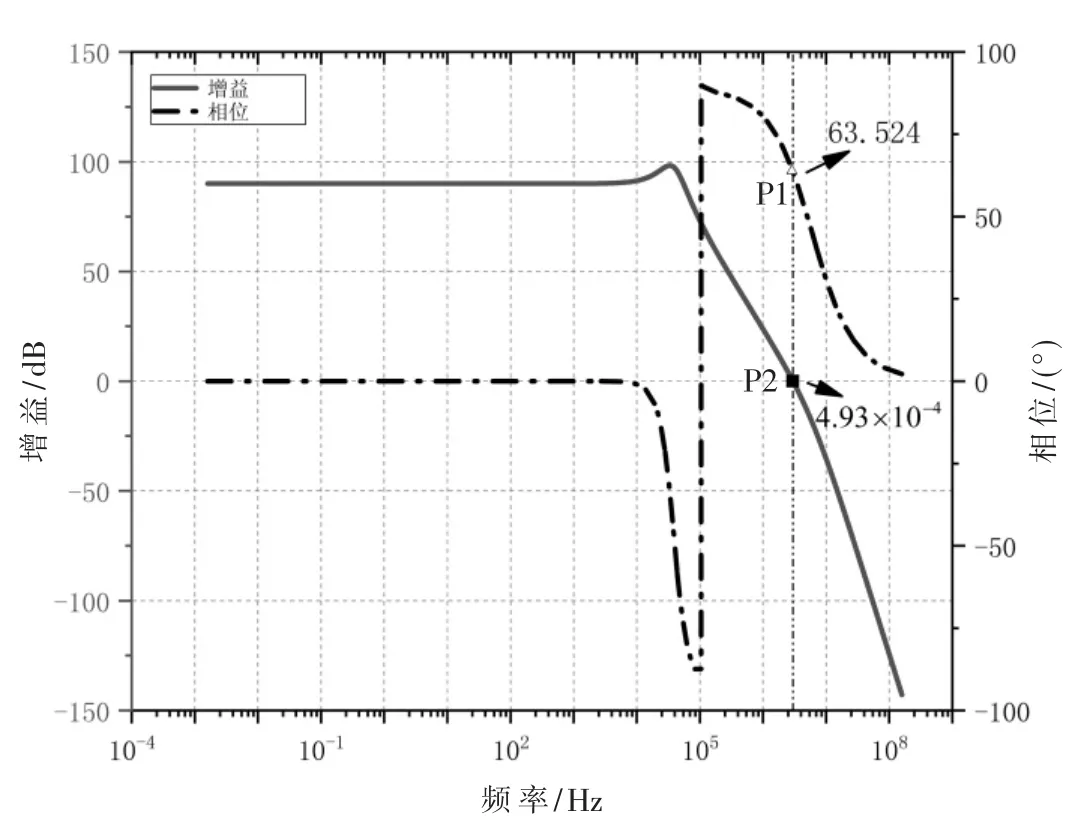

系统输出信号相位噪声如图7 所示,数据由思仪4141F 信号源分析仪测试得到。从图中可以看到,在10 kHz处的归一化相位噪声为-90.53 dBc/Hz,达到设计要求。但从图中可以看出近端的相位噪声恶化迅速,究其原因,在对电路其他部件进行分析之后,发现晶振的相位噪声对系统的影响较大。

图7 改进后的锁相环输出信号相位噪声

由于振荡器频率的牵引效应,当外部信号频率和振荡器的频率接近时,振荡频率受到外部信号的牵引,所以晶振的信号对输出信号会具有牵引效应,晶振的相位噪声会对输出信号产生影响。为了进一步减小输出信号的相位噪声,针对已使用的晶振的相位噪声,必须更换相位噪声更低的信号源,以及提高鉴频鉴相器的频率[13-14]。

3 倍频电路

倍频电路如图8 所示,锁相环输出的信号经过HMC819完成第一次二倍频,由HMC814 的输入输出特性,输出18 GHz 信号功率大于15 dBm,对于第二级二倍频芯片HMC579 来说该功率较大,所以使用HMC656 进行5 dB的衰减。最后使用滤波器滤除谐波,并完成功率放大。

图8 倍频模块框图

倍频部分使用RO5880 基板,板厚为0.254 mm,微带线宽度为0.75 mm 左右。倍频部分均使用裸芯片实现,在基板上放置芯片的位置开孔,将裸片放到孔中,使用导电胶将芯片与腔体粘合,芯片与微带线使用金丝连接。RO5880 基板与RO4350 基板使用金带连接。实物如图9所示,图9 尺寸仅为Φ30 mm。腔体还留出一部分空间用于雷达接收支路的装配。使用频谱仪对信号进行测试,得到如图10 所示结果。在Ka 波段使用探针产生的损耗有18~20 dB,所以实际输出信号功率大于15 dBm。

图9 实物图

图10 36 GHz 信号测试

4 结论

本文通过对锁相环各个部分进行分析从而建立数学模型,根据锁相环的数学模型对锁相环系统的电路参数进行了修改,环路的幅频和相频特性曲线从图4 优化到图5 所示的结果。通过对锁相电路的实际信号测试,锁相环能够实现稳定的基频信号输出,最后使用微组装的方式完成了倍频电路部分的设计,实现了36 GHz、大于15 dBm 的信号输出。频率源的大小仅为Φ30 mm,并且能长期稳定工作。对比同类小型化频率源设计,本设计具有频率高体积小、相位噪声较低的特点,有很好的性能表现[15]。