双向3D图像传感器及其逻辑算法

蔡兴旺,韩岭,梁发云

(南昌大学机电工程学院,江西 南昌 330031)

高端显示技术要求真实地还原三维世界,达到临场感、浸入感和真实感的视觉属性[1-2]。人类使用双目获取视觉信息从而感受3D效果,因此,获取具有视差的左右眼图像是形成3D视频的重要前提。对于视差图像的获取,伍能举[3]、刘助奎[4]首先拍摄单一角度的2D视频,然后通过绘制虚拟视点或者2D视频转3D视频软件转换出具有视差的图像,但以此类方式生成的视差图像与真实三维场景的深度信息存在偏差。文献[5-6]设计了两视点和多视点3D视频采集系统,但是这种拍摄设备只能获取单一方向的3D图像,不便于多个方向3D视频图像的同步获取。对于左右眼视差图像的处理,张春雨等[7]研究了以软件方式处理数据的方法。本文根据双眼视觉机制构建双向3D图像传感器,可以实时采集具有左右眼视差的图像信息。构建便携化的双向3D图像传感器,可以满足汽车前后方向同步监控等场合的需求。并使用FPGA芯片构建数字化、微型化图像处理系统,利用FPGA高速并行处理数据的能力提高系统运算效率。双向3D图像传感器可应用于需要同步获取两个方向3D图像的场合,四目同帧等系统逻辑算法可为航拍多方向3D图像采集、监控等系统的设计提供参考和支持。

1 3D仿生原理

人的左、右眼存在大约65 mm的水平间距,双眼观看同一物体时在视网膜上形成具有视差的左右立体对图像,经过大脑融合使人们产生3D视觉。根据视差3D原理,3D图像传感器可以采用两个相同型号的CMOS图像传感器及其镜头组模拟人的双眼,相隔一定间距安装在同一水平线上,能够获取具有左右视差的立体对图像。3D图像或视频由左眼图像和右眼图像构成[8],从仿生学角度来说,人眼的机能可以保证同步获取图像并经视觉神经传送至视觉中枢形成三维图景。3D图像传感的采集示意图如图1所示。

图1 3D图像传感器的采集示意图Fig.1 Schematic diagram of 3D image sensor acquisition

2 双向3D图像传感器的系统构成

在3D图像传感器的基础上进一步构建双向3D图像传感器,其硬件系统主要包括:FPGA、两组双摄像头模组、缓冲存储器SDRAM以及视频输出接口。在两个方向分别配置双摄像头模组,FPGA作为主控芯片,使用微电子方式实现两个方向3D图像的同步获取,通过数字逻辑方法完成四路视频流的合帧处理并输出,系统构成如图2所示。

图2 系统结构框图Fig.2 System structure block diagram

根据系统结构的规划,初步研制出双向3D图像传感器样机用于逻辑算法的调试和实验。选择具有丰富逻辑资源和足够I/O引脚的FPGA开发板,完成双向3D图像传感器的构建[9]。由于该开发板的接插引脚排列在L形侧边,所以,首先将两组双摄像头模组呈L形配置,拍摄夹角为90°的两个方向,如图3所示。也可以使用软排线连接其中一组双摄像头模组,从而改变该组双摄像头模组的位置和拍摄方向,使两组摄像头拍摄方向呈前后排列,用于同步采集前后方向的视差图像。

图3 双向3D图像传感器Fig.3 Bidirectional 3D image sensor

3 系统逻辑算法

基于FPGA设计系统逻辑算法,双向3D图像传感器通过FPGA芯片控制3D图像输入到输出过程。系统上电后自检无误,图像传感器配置模块同步启动,配置寄存器组参数确定每个CMOS型图像传感器的工作模式,如分辨率、帧率、图像数据格式等[10]。配置结束后触发图像传感器工作,按照帧同步、行同步和像素脉冲的时序输出视频图像数据。图像数据采集模块捕捉3个同步信号,并根据脉冲时序把图像数据传输至下级模块。

由于图像传感器与输出显示设备所用时钟不同且帧频不匹配,因此设计轮序缓存算法解决跨时钟域问题。设计4个写FIFO和4个读FIFO,与SDRAM缓存器构成“4个写FIFO+SDRAM+4个读FIFO”的三缓冲池缓冲结构。4个图像传感器采集的图像数据首先存入写FIFO缓存,再按次序输出到SDRAM中,下级四目同帧控制模块需要数据时,按照时序要求从读FIFO中输出数据,以此完成系统的跨时钟域处理[11]。

考虑到双向3D图像传感器工作状态的实时检测,设置视频显示的接口用于连接外部监视器或显示屏,从而保证系统采集的视频数据能够准确呈现。双目3D图像传感器采用四目同帧的合帧视频,在视频帧中均分为四目图像区[12]。L1、R1区分别显示同一方向两个摄像头采集的左右眼视差图像,L2、R2区分别显示另一方向两个摄像头采集的左右眼视差图像。摄像头视频帧的分辨率可根据实际情况设定,在此以3 840×2 160的分辨率为例规划四目同帧视频输出格式。

图4 四目同帧左右格式Fig.4 Format of four items in the same frame

将图像数据写入SDRAM时需要进行精确的地址控制,这是影响四目同帧格式正确输出的关键。因此,根据图像输出像素位置准确计算突发写入SDRAM的起始地址。B表示SDRAM一次突发写入的数据个数,EL表示L1、L2区一行结束的像素计数,SL表示L1、L2区一行开始的像素计数。C表示一个区的一行像素数据需要写入的完整突发计数,Y表示不足一次完整突发的余量。由于L1、R1、L2、R2各区分辨率相同,因此完整突发次数C以及突发余量Y相等。可计算出:

C=(EL-SL)/B

(1)

Y=(EL-SL)%B

(2)

根据每个区的完整突发次数C以及突发余量Y,进一步计算突发写入SDRAM的起始地址,保证四路视频的精确拼接。VL1、HL1分别表示当前帧已经写入SDRAM的数据对应四目同帧拼显示中的行、列计数,AL1为L1区正在写入的行已经完成的完整写突发数,WL1为L1区的写突发起始地址。由此计算出:

WL1=B×(HL1+(2C+2)×(AL1+VL1))

(3)

WR1=B×((C+1+HR1)+(2C+2)×(AR1+VR1))

(4)

WL2=B×((C+1+HL2)+(3C+3)×(AL2+VL2))

(5)

WR2=B×((C+1+HR2)+(4C+4)×(AR2+VR2))

(6)

计算出L1、R1、L2、R2各区每次突发写入SDRAM的写起始地址,通过对SDRAM的地址进行控制,以此实现双向3D图像传感器四目同帧格式的精确拼接。根据SDRAM地址依次读出,即可输出四目同帧的视频格式。

4 调试与实验

根据3D视频处理的要求,使用硬件描述语言编写图像传感器同步配置模块、图像数据采集模块、轮序缓存控制模块、四目同帧控制模块、监控显示控制模块。使用Quartus Ⅱ进行编译,以JTAG方式下载至FPGA,通过调试之后,可以在监控显示器上观察到四目同帧的视频图像。

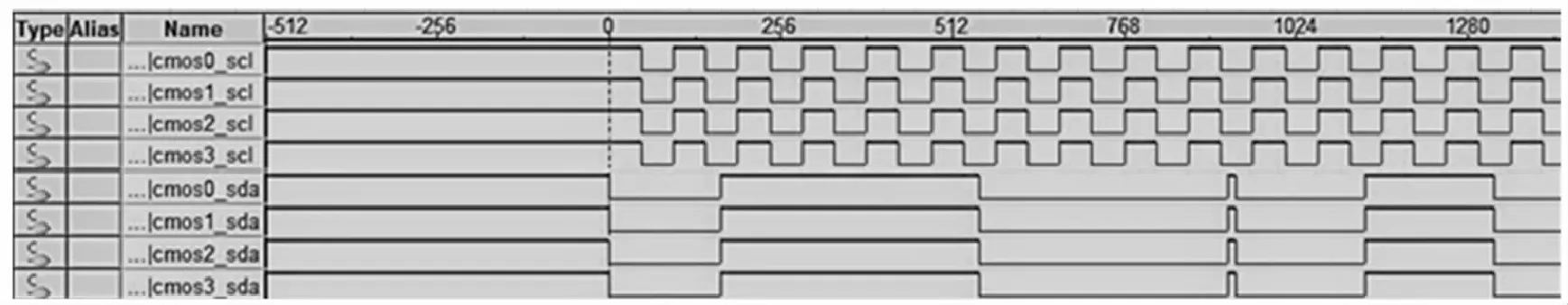

使用SignalTap Ⅱ工具获取寄存器配置时序如图5所示。4个图像传感器配置总线的时钟信号和数据信号时序完全同步,表明4个图像传感器配置同步,保证了图像数据的同步采集。

图5 同步配置时序图Fig.5 Timing chart of synchronous configuration

寄存器配置完成后开始采集图像,通过SignalTap Ⅱ获取4个图像传感器输出的行同步和场同步脉冲时序,如图6所示,可见4个图像传感器的视频输出完全同步。

把双向3D图像传感器放置在四周遮挡的实验箱内,并在两组3D图像传感器前方分别放置飞机模型和布偶。使用大尺寸电视机作为输出显示设备,双向3D图像传感器通过VGA接口输出2个方向的视差图像,系统上电后稳定运行,四目同帧视频输出如图7所示。

(b)场信号时序图6 行场同步Fig.6 Horizontal and vertical synchronous signals

图7 四目同帧3D视频Fig.7 Four eyes 3D video at the same frame

通过电视机屏幕可以观看到3D视频图像,屏幕上半部分显示区的两个窗口显示一组3D图像传感器采集的左右眼图像,下方两个窗口分别显示另一方向3D图像传感器采集的左右眼图像。

5 结束语

本文提出了微型化双向3D图像传感器的系统构成方法,研制了双向3D图像传感器样机,研究了轮序缓存和四目同帧硬件逻辑算法,规划了3D视频帧的结构。该双向3D图像传感器能够同步采集两个方向的3D图像,并输出3D合帧视频,能够解决当前3D拍摄设备的不足之处。实验表明,硬件设计方法合理且数字逻辑算法正确,可为全向3D图像传感器的研制提供参考,可促进3D视频处理集成电路(IC)的产业化。