一种高吞吐率低功耗的AES-CCM 硬件实现

崔 超, 赵 云, 肖 勇, 林伟斌, 徐 迪

南方电网科学研究院有限责任公司, 广州 510663

1 引言

2004 年, IEEE 无线标准小组公布了802.11i 无线局域网安全补充标准[1], 其中定义了基于AES 的全新加密协议CCM 协议, 满足了当时无线局域网安全性的迫切需求, 推动工业4.0、物联网、智能家居、智能驾驶等技术从概念阶段逐渐走向成熟. 目前AES-CCM 加密协议已广泛被802.11、802.15、802.16、Bluetooth、Zigbee 等无线通讯协议采用.

CCM 协议主要由经典的密文块连接CBC 分组模式和计数器CTR 分组模式构成. CBC 分组模式主要用于生成消息完整性校验值(MAC), CTR 分组模式主要用于对传输数据加解密. 因此AES-CCM 加密协议同时具备验证数据完整性、真实性和保障数据安全性的功能.

基于上述安全高效的优点, AES-CCM 加密协议已普遍实现于可穿戴设备、车载网络设备, 智能监控设备中. 然而现在无线网络传输速度不断提高, 2013 年发布的802.11ac 通讯标准推出4×4 多输入多输出(multiple input multiple output, MIMO) 技术, 将传输速率提高到1.3 Gbps, 2019 年发布的802.11ax通讯标准使用8×8 MIMO 技术, 在5 GHz 频段上可以带来高达4.8 Gbps 的第6 代Wi-Fi 连接速度, 而适用于无线VR 头戴和流媒体投屏应用的802.11ay 标准在60 GHz 的频段下, 传输速率可高达20 Gbps,这使得AES-CCM 加密协议处理数据的速度成为无线网络高速发展的瓶颈之一.

此外, 无线终端设备诸如可穿戴设备、智能报警设备等普遍为低功耗设备, 链路层数据加解密以及认证产生的功耗会成为设备的主要功耗. 很多IP 设计者会在数据发送前或接收后, 对数据加解密, 以降低峰值功耗, 这就产生额外的存储和速度开销. 因此AES-CCM 加密协议的低功耗、小面积硬件实现成为无线终端设备在实际应用场景中的另一个技术瓶颈.

为了攻克以上技术难点, 国内外在AES-CCM 的高吞吐率、低功耗实现方面做了很多研究[2–4].Nguyen 等人将CBC 和CTR 并行计算, 提出了双AES 核、高吞吐率的电路实现, 在269 MHz 的最高频率下, 吞吐率能达到2.69 Gbps[5]. 然而该文献并没有注意到CBC 和CTR 具备相同密钥的特性,粗粒度的并行实现致使电路中存在大量的冗余计算, 增加了功耗和面积的开销. Hoang 等人给出了8-bit单核AES-CCM 的超低功耗实现[6], 但是该方案的AES 计算周期数太大, 仅能适用于低速、低功耗产品. Pammu 等人提出9-Core 并行方案[7], 在数据加密时多路并行计算; 在校验值生成时, 利用有限域GF(28) 上的乘法将每16×128 比特转换为128 比特再送进CBC 模块计算校验值, 如此使得原标准中的每128 比特一反馈, 转换为每16×128 比特一反馈, 打破了由于密文反馈导致CBC 不能并行计算的局限性, 将数据处理速率提高至8.32 Gbps. 但是该方案改变了AES-CCM 加密协议的标准, 并不具备通用性.

本文对AES-CCM 加密协议作了深入研究, 利用其链路加密与解密都只用到AES 加密模式的特点,提出了5-Core AES-CCM 高吞吐率低功耗硬件实现方案, 该实现支持半双工通讯方式以及全双工同步计算通讯方式. 在全双工通讯方式下, 5 个Core 参与计算, 吞吐率可达4.23 Gbps. 同时该方案利用其链路加密与解密过程中验证值生成和数据加解密密钥相同的特点, 提出多Core 轮密钥共享方案, 有效减少了冗余电路的实现和计算,与传统实现方式相比,AES-CCM 的电路面积和功耗分别减少14.88%和20.00%.此外, 为了降低功耗, 在S 盒实现时, 该方案利用同构映射, 将复合域GF(28) 上的求逆运算逐步映射到GF(((22)2)2) 上, 并对GF((22)2) 域上的逻辑表达式化简, 使得电路中仅涉及与或非基本单元库, 同时将相邻同构逆映射和仿射变换相结合化简, 从而降低功耗, 缩小关键路径的延时.

本文结构如下: 第2 节介绍了AES-CCM 加密协议、AES 加密算法;第3 节阐述了5-Core AES-CCM加密协议的实现方案; 第4 节给出AES 加密算法的S 盒实现方案; 第5 节介绍仿真环境与结果以及综合环境与结果, 并将本方案与其他方案作对比分析; 第6 节对方案进行总结.

2 预备知识

本节第一部分简要介绍AES-CCM 加密协议并概述其特点; 第二部分介绍AES 加密算法.

2.1 AES-CCM 加密协议

无线通讯网络的安全性保证包括三方面: 密钥管理、数据验证以及数据保密.

密钥管理一般结合随机数的生成与传输, 利用根密钥、读取密钥、会话密钥三级密钥体制实现主从设备的身份验证、密钥分发以及会话密钥的更新.

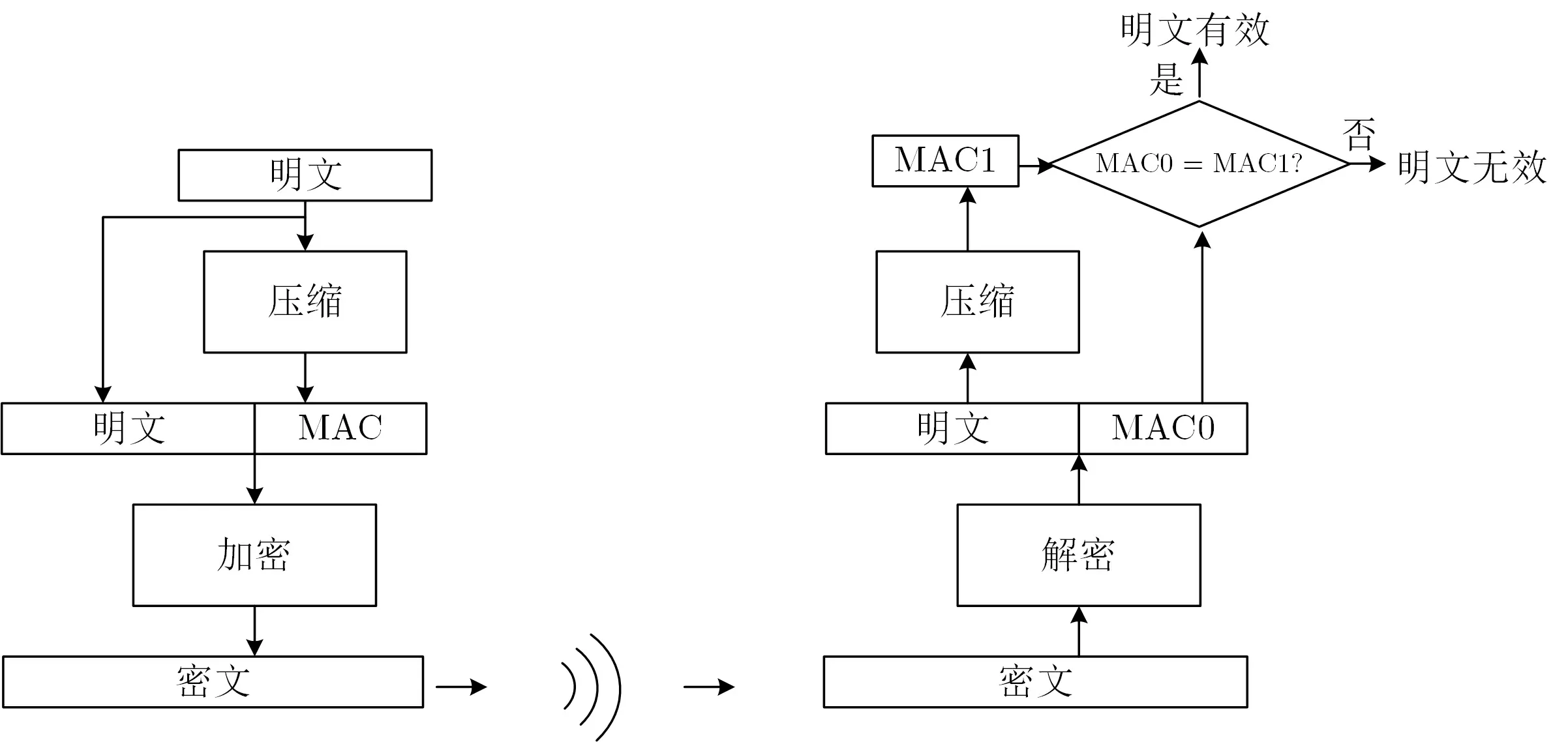

数据验证一般由哈希函数或者对称加密算法的特定分组模式构成, 如图1 所示, 数据发送前, 发送方对明文数据压缩, 生成消息验证码MAC 值附于明文后, 发送给接收方. 接收方收到数据后用同样的算法压缩明文得到另一个MAC 值, 并将两个MAC 值比较, 若一致, 则接收数据无误.

数据保密一般由加密算法结合分组模式共同实现对数据的分组与加解密, 在图1 中, 发送方将明文数据和MAC 值拼接起来并分成等长度的数据组, 接收方接到密文数据后用同样的加密算法和分组模式的逆过程, 以及相同的密钥对数据进行分组解密, 以得到明文和MAC 值.

图1 链路层数据验证与数据保密Figure 1 Validation and confidentiality of link layer data

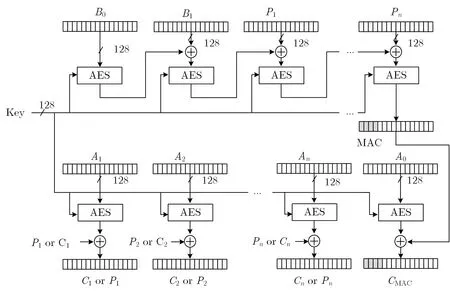

AES-CCM 主要用于保护物联网的数据安全传输, 由AES 分组密码算法和CCM 分组模式构成.CCM 是一种比较新的分组模式, 主要由CBC 分组模式和CTR 分组模式构成. 其结构如图2 所示.

随着教学改革的步伐不断迈进,老师在课堂中不但要传授学生知识,还需要把学生的探索精神与创造能力培养起来,但是由于受到根深蒂固的传统教育观念所影响,很多的老师在教学过程中并没有把提升学生的综合素质重视起来。在教学的过程中老师必须改变这种传统的教学观念,充分应用新课改背景下的现代化教学理念,尊重学生学习过程中的主观能动性,引导每个学生都能够主动深入思考,并能够展现自己的个性。

图2 AES-CCM 结构图Figure 2 AES-CCM architecture

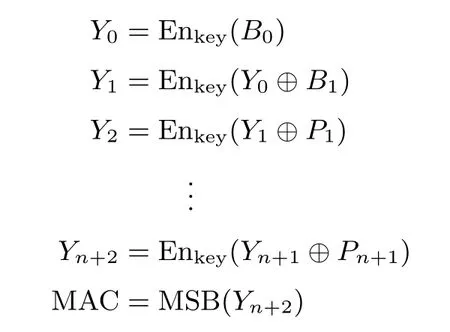

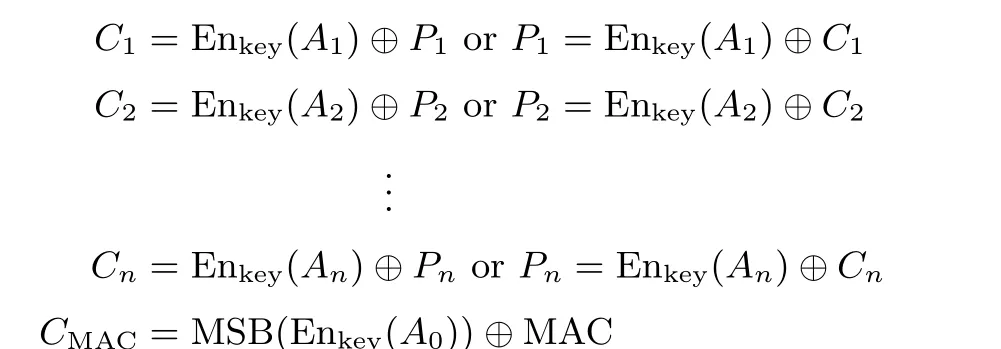

MAC 值主要借鉴CBC 分组模式生成, AES 的输入为包含数据包头、数据长度、数据明文等信息的特定分组与前一组AES 密文输出Yi−1的异或值. 其计算过程如下, 其中B0、B1为包含数据包头和数据长度的128 bits 数据,Pi为128 bits 的明文分组.

数据的加解密主要借鉴CTR 分组模式完成, 该分组模式的加密流程和解密流程完全一样. AES 的输入为包含数据组计数值信息的数据Ai, AES 的密钥key 同生成校验值使用的密钥key 相同, 其计算过程如下:

2.2 AES 加密算法

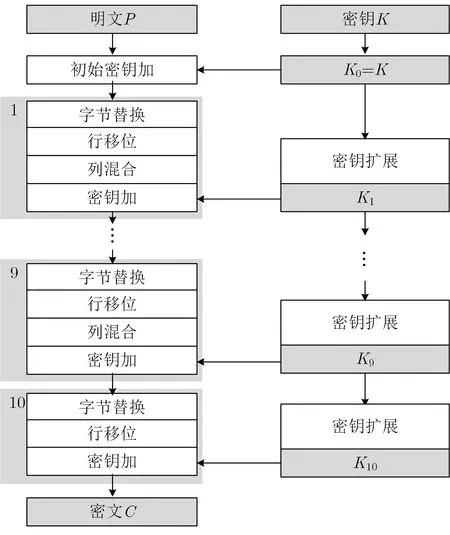

AES 是美国国家标准技术局(NIST) 于2001 年发布的一个新的分组加密算法, 用来取代DES 算法.分组长度固定为128 比特, 密钥长度在128、192、256 中可选, 分别对应AES-128、AES-192、AES-256.AES-128 的加密流程如图3 所示, 总体由两部分组成: 密钥扩展和轮迭代. 每一轮的轮密钥扩展由移位操作、异或操作和字节替换操作构成; 轮迭代由字节替换、行移位、列混合、密钥加组成.

图3 AES 算法结构Figure 3 AES architecture

3 5-Core AES-CCM 加密协议的实现

通过对AES-CCM 加密协议进行分析, 我们归纳出该协议的3 个特点:

(1) 无论设备作为数据的发送方还是数据的接收方, AES-CCM 加密协议中仅用到AES 的加密模式,因此硬件实现中为减小设备的功耗和面积可以省去AES 解密模式的实现.

(2) AES-CCM 加密协议中MAC 值的生成和数据的加解密可以并行计算.

(3) AES 在MAC 值生成以及数据加解密时所用到的密钥相同, 因此为减小功耗, 多个轮迭代函数可以共享一个密钥扩展模块.

根据以上AES-CCM 加密协议的特点分析, 本文实现了5-Core AES-CCM 硬件模块, 该模块以高性能5-Core AES 加密模块为运算核心, 在外围CCM 模块的协同控制下来实现AES-CCM 加密协议.

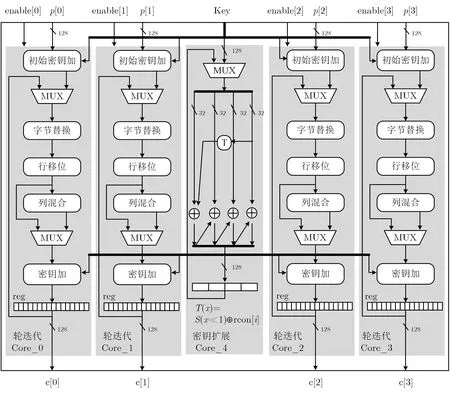

3.1 5-Core AES 模块硬件实现

5-Core AES 模块的模块结构如图4 所示, Core_4 实现密钥扩展的轮操作, Core_0–Core_3 为4 个完全一样的轮迭代函数, 并行实现4×128 比特的数据加密. 5-Core AES 模块根据需要可配置为2-Core、3-Core、4-Core、5-Core 模式, 用于AES-CCM 半双工或全双工同通讯场景下, 也可用于非CCM 模式的AES 多路并行加密场景.

图4 5-Core AES 结构图Figure 4 5-Core AES architecture

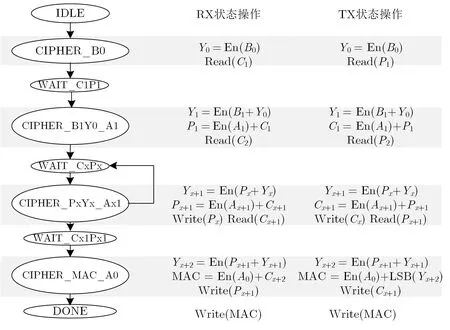

3.2 CCM 模块硬件实现

CCM 模块主要由状态机构成, 在半双工通讯方式下, 仅实现RX 状态操作或TX 状态操作, 其状态跳转和状态操作如图5 所示, 各状态含义参照图2 AES-CCM 结构框图理解, CIPHER_B0 状态表示对B0数据加密, 调用一个加密核, 将5-Core AES 加密模块配置成2-Core 模式; CIPHER_B1Y0_A1状态表示对B1⊕Y0数据和A1计数值加密, CIPHER_PXYX_AX1 状态表示对Px ⊕Yx和计数值Ax+1加密, CIPHER_MAC_A0 状态表示对最后一组明文Pn ⊕Yn加密生成MAC 值, 同时对A0加密.CIPHER_B1Y0_A1 状态、CIPHER_PXYX_AX1 状态、CIPHER_MAC_A0 状态调用两个并行的加密核, 将5-Core AES 加密模块配置成3-Core 模式. 每个加密状态的跳出条件为加密完成, 每个WAIT状态的跳出条件为数据获取完成.

图5 半双工通讯方式CCM 状态控制Figure 5 CCM state control of half-duplex communication

在全双工通讯方式下, RX 数据包处理和TX 数据包处理并行实现, 状态跳转如图6 所示. CIPHER_0 状态加密一组数据, 将5-Core AES 加密模块配置成2-Core 模式; CIPHER_01 状态同时加密两组数据, 将5-Core AES 加密模块配置成3-Core 模式; CIPHER_012 状态同时加密三组数据, 将5-Core AES 加密模块配置成4-Core 模式; CIPHER_0123 状态同时加密四组数据, 将5-Core AES 加密模块配置成5-Core 模式.

状态跳转有4 种情况, 其状态跳转如图6 的右侧所示. 1 为先处理一个数据包, 随后又开启另一个数据包的处理, 两个数据包同时结束的情况; 2 为先处理一个数据包, 随后开启另一个数据包的处理, 两个数据包不同时结束的情况; 3 为两个数据包同时开始, 同时结束的情况; 4 为两个数据包同时开始, 不同时结束的情况. flg_packet0_cmp 信号和flg_packet1_cmp 信号分别代表两个数据包处理中的指示信号, 根据以上4 种情况, 结合每个数据包的分组长度和计数值Ax产生高电平信号. 状态跳转条件在flg_packet0_cmp 和flg_packet1_cmp 不同值下结合加密完成信号和数据获取完毕信号产生.

4 AES 算法S 盒的低代价实现

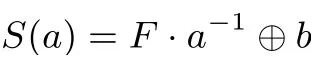

S 盒在RTL 实现时主要有查找表方式和基于有限域运算方式[8]. S 盒的查找表方式快捷直接, 但是电路面积非常大, 不适合高速低功耗应用实现. 有限域实现S 盒, 计算公式为:

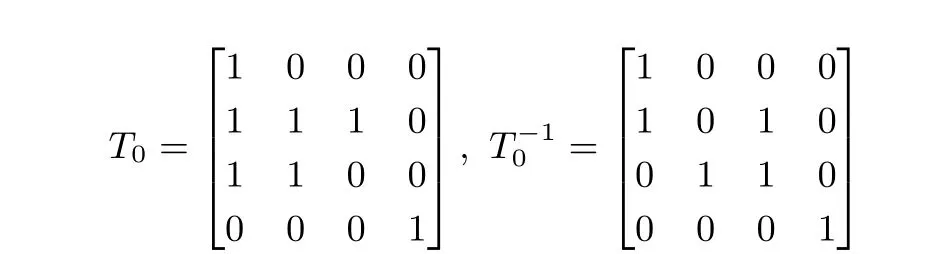

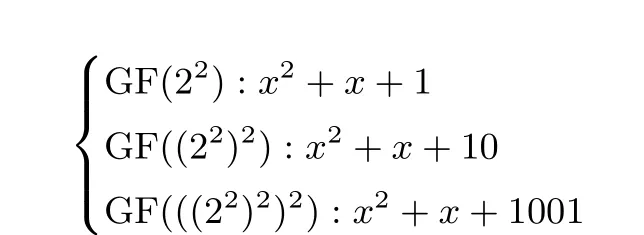

先将a在有限域GF(28) 上进行乘法逆运算, 再对其乘法逆元进行仿射变换. 该种方式实现的S 盒电路结构紧凑, 资源消耗少[9,10], 但是其关键在于有效实现有限域GF(28) 上的乘法逆元. 本文利用复合域的同构映射, 将GF(28) 上的运算逐步映射到GF(((22)2)2) 上进行, 以降低运算的复杂度. 方案中GF(28) 和GF((24)2) 之间的同构映射为:

GF(24) 和GF((22)2) 之间的同构映射为:

各复合域中的不可约多项式为:

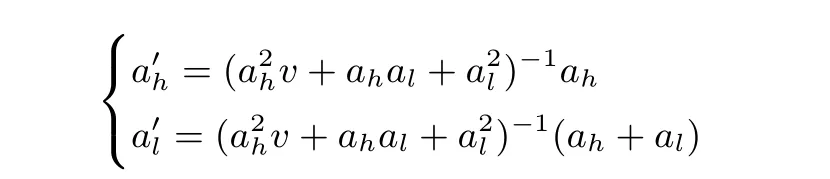

在以上代数背景下得出(ahx+al)−1在GF((24)2) 上的乘法逆元a′hx+a′l为:

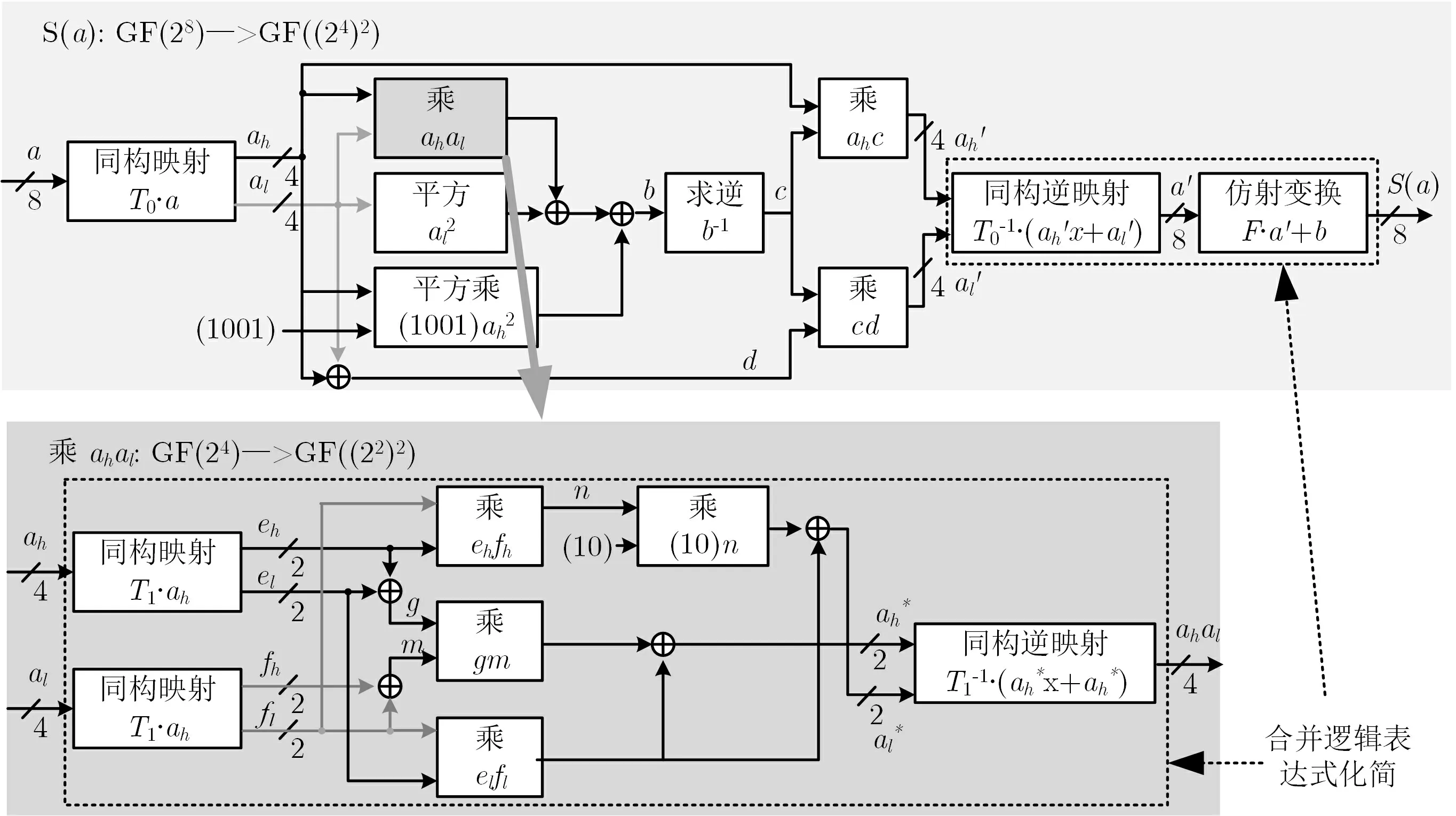

上式中v={1001}, 从上式可以看出GF(28) 上的求逆运算经过同构映射转化为GF(24) 上的求逆运算、乘法运算、平方运算、平方乘运算和异或运算. 利用同样的计算方式可以将GF(24) 上的运算同构映射到GF((22)2) 上进行, 从而将逻辑表达式逐步分解. 图7 给出GF(28) 上求逆和GF(24) 上乘积的电路结构.

图7 GF(28) 上的乘法逆元电路和GF(24) 上的乘法电路Figure 7 Circuits of multiplicative inverse in GF(28) and multiplication in GF(24)

为了简化电路的运算路径, 本方案将GF(24) 与GF((22)2) 之间的同构映射T1、同构逆映射分别与GF((22)2) 上的乘积运算、逆运算、平方运算、平方乘运算的逻辑表达式结合化简, 得到GF(24) 上的求逆运算、乘法运算、平方运算和平方乘运算简化后的逻辑表达式如下所示:

5 实验结果与分析

为了对方案的功能进行验证, 我们对方案进行RTL 代码实现, 利用VCS 仿真软件结合Testbench 验证脚本和测试激励, 完成各模块的前仿功能验证.

由于 5-Core AES 模块由 4 个完全一样的轮函数并行实现, 故我们在此只需分析一个轮函数的仿真结果, 设置加密密钥为: 66c6_c227_8e3b_8e05_3e7e_a326_521b_ad99, 明文输入为:0400_deaf_babe_badc_ab24_0000_0000_0101, 实验结果仿真的密文输出为: d824_88ba_3df3_896d_bfb0_ba38_e55e_5e26. 为了验证RTL 代码功能正确性, 我们对算法进行了软件实现, 并将RTL仿真结果与软件加密模型对比, 经对比密文输出一致, 轮函数功能正确. 同时通过仿真可知完成AES-128的完整计算需要11 个周期.

CCM 模块在状态机的控制下完成数据读写以及5-Core AES 模块的数据和使能配置,使其完成AESCCM 协议的数据处理.

在半双工通讯方式下, 假设需要发送或接收的数据包有效数据长度为256×128 比特, 完成256×128比特的RX_DATA 或TX_DATA 数据传输需要加密(2×(256+1)+1)×128 比特的数据, 至少需要12×(256+2) 个周期(每组数据需要11 个周期的加密, 至少1 个周期的数据获取). 故在200 MHz 的时钟频率下, 吞吐率为(256×128)×200 M/(12×(256+2))=2.12 Gbps.

在全双工通讯方式下, 若传输设备需要发送和接收各256×128 比特数据, 由于发送数据包和接收数据包存在3.2 节描述的四种情况, 故吞吐率不恒定. 考虑最差的情况, 两个数据包仅交叠128 比特,则CIPHER_0 状态执行1 次, CIPHER_01 状态执行255×2 次, CIPHER_012 状态执行1 次, CIPHER_0123 状态执行1 次, 完成2× 256× 128 比特的rx_data 和tx_data 数据传输至少需要12×(1+255×2+1+1) 个周期. 故在200 MHz 的时钟频率下, 吞吐率为2×256×128×200 M/12×(1+255×2+1+1) = 2.13 Gbps. 考虑最好的情况, 两个数据包完全同步, 则CIPHER_01 状态执行1 次,CIPHER_0123 状态执行256+1 次, 完成2×256×128 比特的RX_DATA 和TX_DATA 数据传输至少需要12×(1+257)个周期. 故在200 MHz 的时钟频率下,吞吐率为2×256×128×200 M/12×(1+257)=4.23 Gbps. 因此全双工通讯方式下的吞吐率在2.13 Gbps 和4.23 Gbps 之间, 该协处理器能达到的峰值吞吐率为4.23 Gbps.

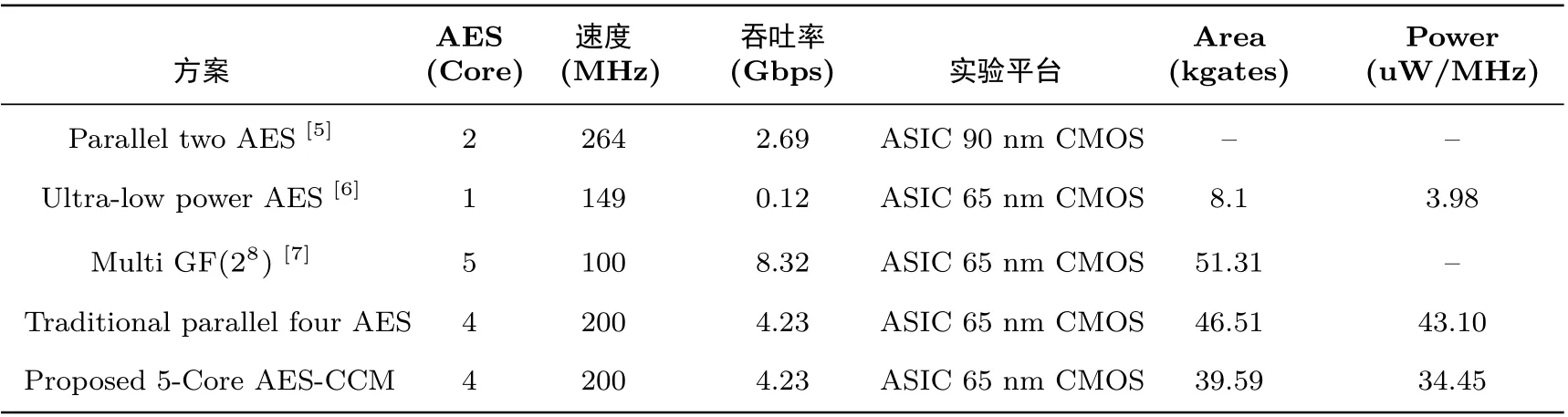

将该方案与其他方案的性能进行对比, 结果见表1, 对比发现Multi GF(28) 方案[7]的数据处理速度最快, 但是该方案将不可并行的CBC 分组模式做了调整, 将128 比特分组改为16×128 比特分组, 并对16×128 比特数据在GF(28) 上压缩成128 比特, 再送入CBC 分组模式, 以此提高数据并行处理的速度, 实际上这种方式已经改变了标准的AES-CCM 加密协议, 并不具备广泛的适用性. 其他方案中的最高吞吐率方案为Parallel two AES[5], 考虑到实现工艺不同, 我们对该文献做了最大相似度电路实现, 并在TSMC 65 nm、tt_1p0v_25c 的工艺下综合, 发现其最高频率能达到320 MHz, 对应吞吐率为3.26 Gbps,故本论文方案是其他方案中归一化后最高速率3.26 Gbps 的1.30 倍.

表1 5-Core AES-CCM 方案与其他方案AES-CCM 的性能对比Table 1 Comparison of proposed 5-Core AES-CCM with other AES-CCM techniques

为了对方案的功耗和面积进行评估, 我们在TSMC 65 nm、tt_1p0v_25c 的工艺下用Design Compiler 软件对AES-CCM 模块进行综合,在200 MHz 的时钟约束下,综合所得电路面积为39.59 kgates,功耗为6.89 mW. 为了对比, 我们对传统非轮密钥共享, 粗粒度4 个AES 并行实现AES-CCM 加密协议方案进行了电路实现(外围CCM 控制模块基本不变, 5-Core AES 模块替换成4 个并行的AES 模块), 并在相同工艺和约束下进行综合, 电路的面积为46.51 kgates, 功耗为8.62 mW, 具体各模块的面积和功耗分布情况如表2 所示. 因此本方案中的密钥共享方案能够使电路的面积和功耗分别减小14.88% 和20.00%.

表2 5-Core AES-CCM 方案与Traditional parallel four AES 的功耗面积对比Table 2 Comparison of proposed 5-Core AES-CCM with traditional parallel four AES

6 结论

本文根据AES-CCM 链路层数据加密与解密都只用到AES 加密模式, 且数据校验值生成与数据加解密密钥相同的特点, 给出5-Core AES-CCM 加密协议的硬件实现方案, 方案采用4 个轮函数并行计算的方式同时实现TX 与RX 两个数据包的处理, 提高了数据吞吐率. 同时方案采用轮密钥共享机制, 以及AES 算法S 盒复合域化简实现方法, 有效去除冗余电路, 减小了电路面积和功耗.