基于FPGA 和DSP 的星载软件动态重构设计

马传干

(中国西南电子技术研究所,四川成都 610036)

采用FPGA 和DSP 架构的卫星载荷设备,在空间环境中,软件的可靠性设计是一个难题[1-2]。传统的解决方法采取在轨更新升级,主要有3 种方式:1)利用一次性编程的反熔丝型FPGA 作为控制节点,完成其他节点FPGA 软件的重构功能[3];2)通过预留钩子函数,利用增量编译链接的特性,实现DSP 软件部分功能的在轨修复[4];3)基于操作系统引导加载的原理,系统启动并正常工作后,通过指令二次引导应用程序加载,实现软件更新升级的功能[5-7]。然而,这3 种方法都有一部分程序功能是固定的且无法修改。这种基于部分功能软件可重构的设计方式,其功能的可扩展性不全面,难于适应不断增长的差异化需求。因此,针对现有技术存在的不足之处,基于SRAM 型“双FPGA+DSP”的硬件架构,提出了一种具有安全启动特性,硬件实现更简单、功能重构更灵活,且全功能FPGA 和DSP 软件可实现在轨动态重构的解决方案,并对该方案的硬件实现原理和相关技术进行了分析和设计。

1 硬件实现原理

在星载传感器系统中,功能软件集中部署在载荷功能单元的可编程逻辑芯片FPGA 和数字信号处理器DSP 内部。

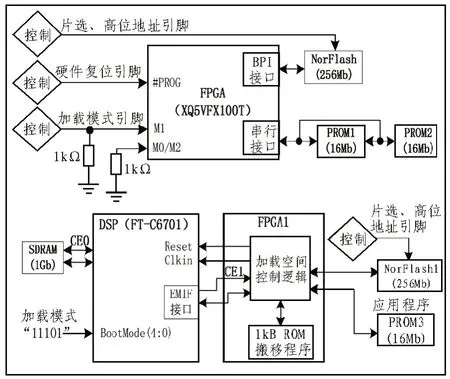

基于SRAM 型“双FPGA+DSP”架构的载荷功能单元,其总体框图如图1 所示,图中虚线框为与该功能单元密切关联的设备[8-10]。

图1 载荷功能单元总体框图

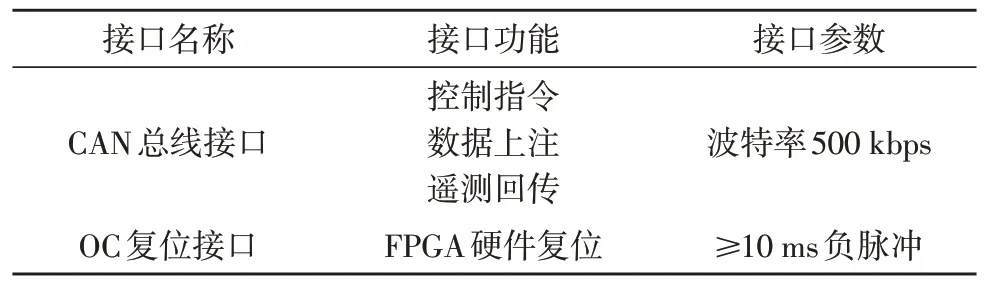

载荷功能单元对外有两类控制接口,分别为CAN总线接口以及OC复位脉冲接口,具体参数见表1。

表1 载荷功能单元对外接口表

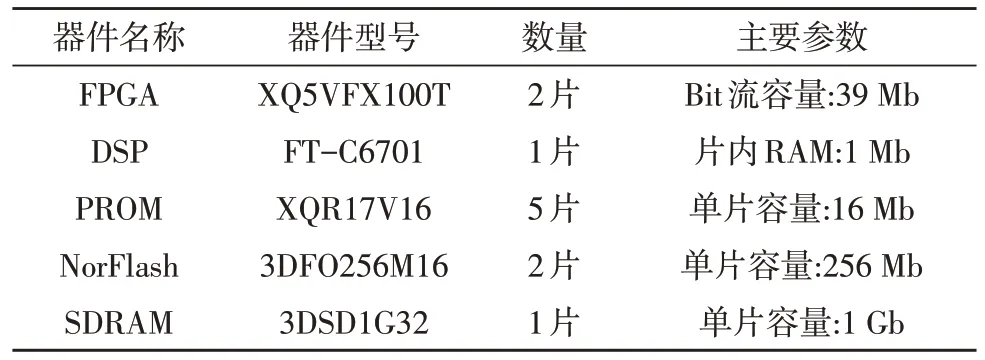

载荷功能单元的主要元器件选型见表2。

表2 载荷功能单元主要元器件列表

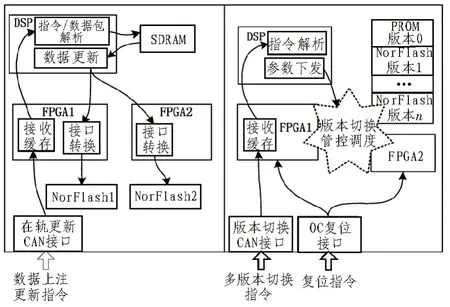

在载荷功能单元中,软件动态重构包括FPGA和DSP 软件多版本切换以及在轨更新升级两种方式,其实现原理如图2 所示。

图2 功能软件重构原理框图

1)软件多版本切换的工作原理

在电路设计中,利用PROM 和NorFlash 双存储电路,实现FPGA 和DSP 全功能软件多版本的本地存储[11]。设备上电后,FPGA和DSP默认加载PROM版本的功能软件。当载荷管理设备接收到地面站的版本切换指令,需要进行软件版本切换时,具体过程如下:

①载荷管理设备通过CAN 接口发送FPGA2 的版本切换指令及信息,DSP 解析指令后,由FPGA1 控制FPGA2 的加载模式和外挂NorFlash2 中相应版本的地址空间,并通知载荷管理设备软件版本切换准备就绪;载荷管理设备确认状态后,发送FPGA2 的OC 复位信号,FPGA2 硬件复位后主动从NorFlash2中完成指定版本软件的加载。

②载荷管理设备等待FPGA2切换版本成功后,发送FPGA1 的版本切换指令及信息;FPGA1 在FPGA2和载荷管理设备的协同控制下,完成版本在轨切换,其过程与FPGA2 的版本切换过程完全一样。

③载荷管理设备发送DSP 的版本切换指令及信息,DSP 解析指令后,由FPGA1 控制其外挂NorFlash1中相应DSP 版本的地址空间,然后在FPGA1 控制下DSP 完成版本切换。

④DSP 完成版本切换后,载荷管理设备通过CAN 总线的轮询指令,判断切换后功能是否运行正常;正常则结束切换流程,不正常则通过发送OC复位信号,进行版本回退,重新加载并运行PROM 版本。

在版本切换过程中,FPGA1、FPGA2 和DSP 三者之间采用相互控制、相互引导的管控调度策略,实现了没有本地通用CPU 或主控制器(如反熔丝型FPGA)的条件下,专用信号处理器(FPGA、DSP)全功能软件版本的自主重构特性,在简化电路设计的同时,极大地提高了载荷功能单元的灵活性。

2)软件在轨更新升级的工作原理

当在轨预设软件版本的工作模式都不能满足要求,或者有新增任务需求时,则需要地面站发送在轨更新指令,载荷管理设备接收地面站的指令后,具体执行过程如下:

①载荷管理设备通过CAN 接口发送软件更新指令,DSP 接收指令并解析,获取软件类型、软件版本号等信息,并判断指令信息的正确性;指令正确,则开始逐包接收软件更新数据,并执行数据校验操作。

②数据校验正确后,根据数据包的编号,将数据包写入SDRAM 的缓存空间中,并继续接收新的数据包,同时回复正确接收信息;否则,发送请求数据包重传信息。

③当所有数据包接收完毕,载荷管理设备发送数据存储指令,DSP 根据指令中软件类型、软件版本号等信息,将SDRAM 中缓存的全部数据包,写入NorFlash1 或者NorFlash2 的3 个不同物理空间。

软件在轨更新过程中,同时支持所有数据包一次性上传、数据包分包后多次断电续传、数据包仅部分上注等功能,不但解决了软件在轨更新面临的星地链路通信速率小、过境时间短、程序数据包数据量大等困难,而且极大地提高了载荷功能单元的扩展性。

2 软件动态可重构具体设计

结合该方案的硬件电路,从加载模式、控制方式、版本切换流程、数据包存储等几个方面构建了灵活的管控策略,实现了软件可动态重构的功能。

2.1 加载模式设计

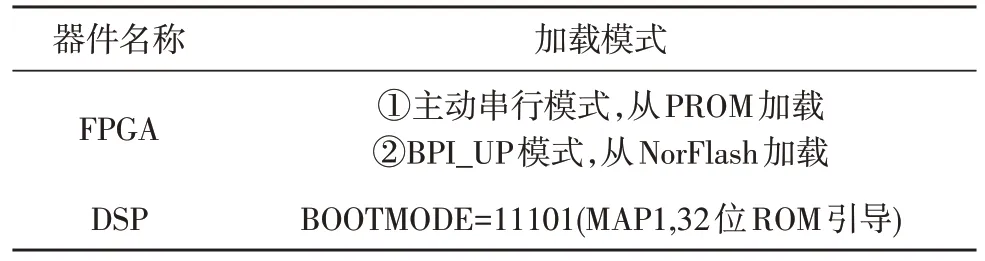

加载模式决定了系统的硬件设计和软件设计,特别是对重构软件的管理有着重大影响,该方案中FPGA 和DSP 加载模式的设计见表3。

表3 FPGA和DSP加载模式

由表3 可知,基于PROM 和NorFlash 双存储电路,FPGA 设计了两种加载模式[12]:主动串行模式和BPI_UP 并行模式;而DSP 采用片内0x0 地址空间映射的32 位ROM 引导方式,具体设计电路见图3。

图3 加载模式电路图

1)FPGA 主动串行加载模式

设计中,FPGA 的加载模式引脚M[2:0],通过下拉1 kΩ的电阻接地;设备上电后,初始状态为“000”,此时FPGA 工作在主动串行加载方式,将自动从片外两片级联的PROM 中进行加载。

FPGA 的型号为XQ5VFX100T,其配置bit 流为39 Mb。根据实际工程的测试,当FPGA 资源使用率达到90%时,对bit 流文件的压缩率可达70%,即39 Mb 压缩后为27.3 Mb,因此方案中选用2 片16 Mb的PROM 进行级联,满足使用要求。

PROM 型号为XQR17V16,具有SEU(单粒子翻转)免疫的特性,所以主动串行加载方式确保了FPGA 上电状态程序运行的可靠性。

2)FPGA BPI_UP 并行加载模式

FPGA 的加载模式引脚M1,通过控制电路可以改变电平状态。当M[2:0]状态为“010”时,FPGA 工作在BPI_UP 并行加载方式,此时控制电路触发硬件#PROG 引脚复位后,FPGA 将自动从片外NorFlash 中进行加载。

在空间环境下,NorFlash 具有SEU(单粒子翻转)的潜在风险,而且断电后重启也不能恢复。为了确保存储在NorFlash 中程序数据的可靠性,设计中将同一个版本的程序数据同时存储在NorFlash 的3 个不同的物理空间,当某一空间的数据发生SEU 时,采用3 取2 的原则,逐一比较3 个物理空间中的数据,就可以实现数据的纠错。因此FPGA 的一个NorFlash 软件版本至少需要96 Mb 的存储空间。

为了能够存储多个软件版本,NorFlash 的型号选用3DFO256M16,单芯片容量为256 Mb,芯片内部由4 片4M×16b 的基片组成。所以,通过控制4 个基片的片选信号和最高位地址线,可以将NorFlash 划分为8 个32 Mb 的存储空间,满足了至少2 个FPGA软件版本的同时存储。

3)DSP 32 位ROM 引导方式

在电路设计中,DSP 的加载模式引脚BM[4:0],通过上下拉电阻的配置,状态固定为“11101”,因此DSP 上电复位后,工作在32 位ROM 的自举模式:即DMA 控制器从CE1 空间(相当于FPGA1 空间)复制固定长度(C6701 是64 kb)程序到片内地址0x0 处,然后从片内地址0x0 处开始执行。

考虑到64 kb 的程序可能无法满足未来复杂功能的需求,为了兼容灵活性和扩展性,通过二次搬移程序将直接引导方式更改为二次引导模式,因此该方案中DSP 应用程序的大小可扩展到2 Mb(取决于外置PROM 存储器空间),具体过程如下:

①DSP 上电复位后,默认从FPGA1 片内1 kb 的ROM 中直接复制用户二次搬移程序到片内地址0x0处,并开始执行。

②用户二次搬移程序根据FPGA1 内部加载空间控制逻辑的状态信息,从FPGA1 片外的PROM3或NorFlash1 的指定空间再次将用户的应用程序复制到片内程序空间0x400 或片外SDRAM 空间0x400000 处,结束后开始运行程序。

设计中,PROM3 程序的加载是上电默认的状态,确保了DSP 上电运行的可靠性;而NorFlash1 程序的二次加载实现了DSP 软件多版本的可重构。

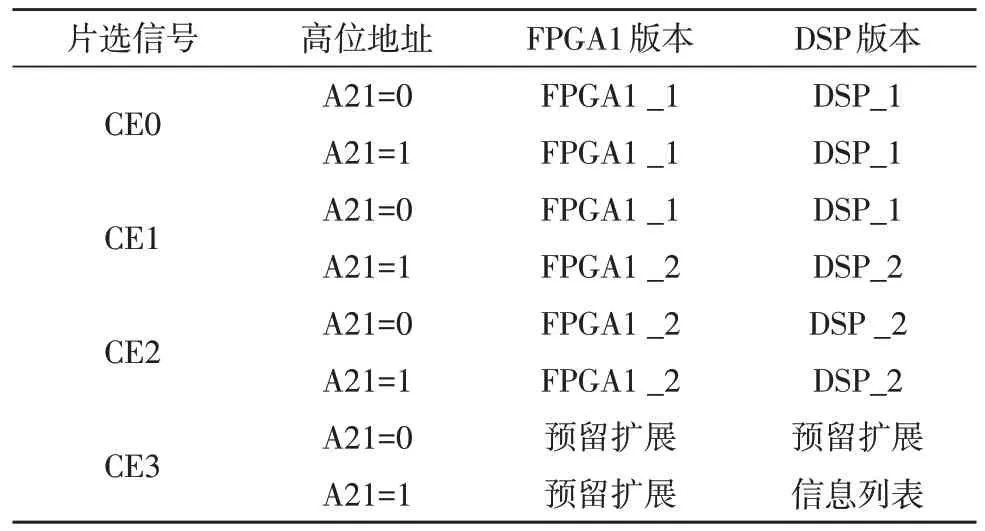

结合FPGA1 的加载电路可知,NorFlash1 中同时存储了FPGA1 和DSP 的多版本程序,对各版本程序存储空间的划分见表4。

表4 NorFlash1存储空间分配表

表4中,FPGA1分配了6个存储空间,存储2个软件版本,每个版本大小为28 Mb;DSP也分配了6个存储空间,存储2个软件版本,每个版本大小为4 Mb;另外预留了3个存储空间,共60 Mb,用于扩展功能;最后一个4 Mb 存储空间用于记录NorFlash1 的信息列表。(注:NorFlash2 只用于存储FPGA2 的程序,其存储空间的划分方法与NorFlash1完全相同,因此不再展开说明。)

2.2 控制方式设计

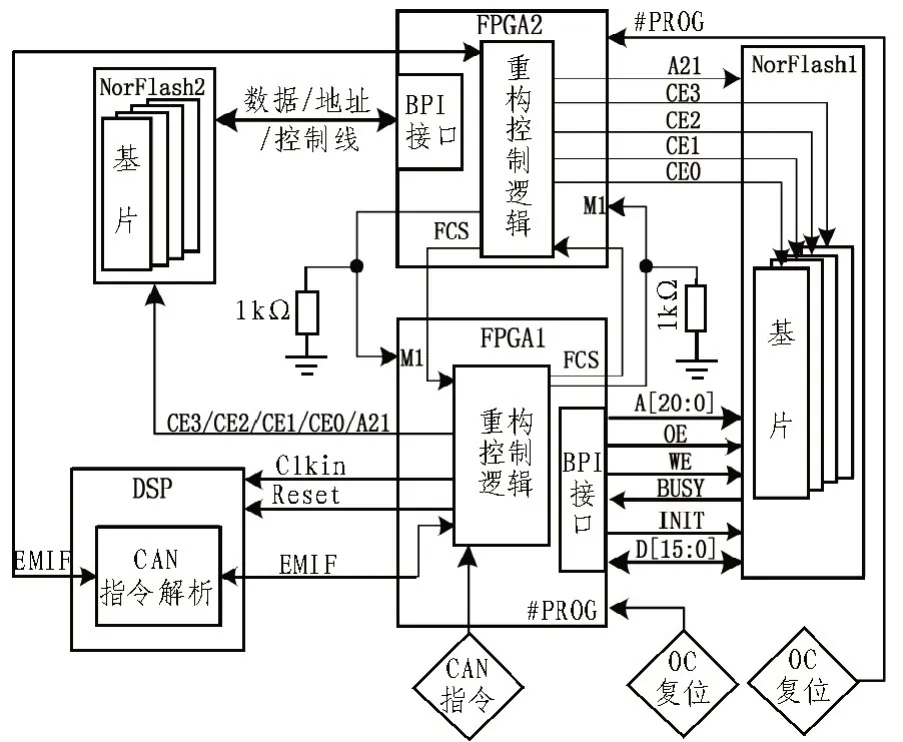

控制方式是实现功能软件动态重构的核心。相比传统采用本地通用CPU 或主控制器(如反熔丝型FPGA)进行统一控制的方法,该方案采用DSP 解析指令、双FPGA执行指令、FPGA和DSP之间相互控制、相互引导的管控调度策略,具体电路设计如图4所示。

图4 控制方式电路图

基于相互控制、相互引导的管控调度策略,图4中的控制电路可分为3 部分,分别为DSP 控制电路、FPGA1 控制电路以及FPGA2 控制电路。

1)DSP 控制电路设计

与DSP 控制电路有交互的对象有FPGA1 和FPGA2,其相互逻辑关系具体如下:

①FPGA1 输出硬件复位Reset 和工作时钟Clkin信号给DSP,实现DSP 工作状态的控制功能;

②FPGA1 通过EMIF 总线转发CAN 指令给DSP,DSP 将解析后的指令信息又通过EMIF 总线发送给FPGA1 和FPGA2,实现重构指令逻辑控制的功能。

2)FPGA1 控制电路设计

与FPGA1 控制电路有交互的对象有DSP、FPGA2、NorFlash2 以及载荷管理设备,其相互逻辑关系具体如下:

①载荷管理设备输出OC 负脉冲,实现FPGA1的硬件复位功能;

②FPGA2 控制FPGA1 的加载模式引脚M1,实现串行加载和并行加载的控制功能;

③FPGA1 输出硬件复位Reset 和工作时钟Clkin信号给DSP,实现DSP 工作状态的控制功能;

④FPGA1 转发CAN 指令给DSP,并接收DSP 指令解析后的信息,实现重构指令逻辑控制的功能;

⑤FPGA1 接收FPGA2 并行加载接口的片选信号FCS,结合DSP 输出的重构指令信息,通过片选信号CE0~CE3 和高位地址线A21,实现NorFlash2 存储空间的选择控制功能。

3)FPGA2 控制电路设计

与FPGA2 控制电路有交互的对象有DSP、FPGA1、NorFlash1 以及载荷管理设备,其相互逻辑关系具体如下:

①载荷管理设备输出OC 负脉冲,实现FPGA2的硬件复位功能;

②FPGA1 控制FPGA2 的加载模式引脚M1,实现串行加载和并行加载的控制功能;

③FPGA2 接收DSP 指令解析后的信息,实现重构指令逻辑控制的功能;

④FPGA2 接收FPGA1 并行加载接口的片选信号FCS,结合DSP 输出的重构指令信息,通过片选信号CE0~CE3 和高位地址线A21,实现NorFlash1 存储空间的选择控制功能。

2.3 版本切换流程设计

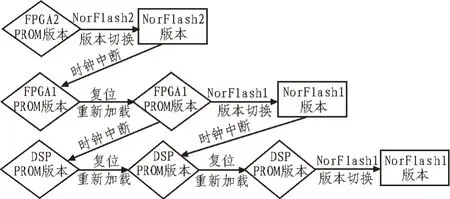

版本切换流程是实现功能软件多版本切换的关键。时钟电路是版本切换过程的心脏,至关重要[13],为简化电路设计,该方案采用单晶振的时钟设计方法,具体为:40M 晶振→FPGA2→FPGA1→DSP。

结合时钟电路设计以及FPGA 和DSP 之间相互控制、相互引导的策略,软件版本切换的流程设计如图5 所示。

图5 软件版本切换流程设计

图5 中,软件切换流程设计具有以下特点:

①上电或硬件复位状态:所有功能器件FPGA和DSP 均为PROM 版本;

②功能器件切换NorFlash 版本时,优先级从高到低为:FPGA2→FPGA1→DSP;

③高优先级器件版本切换过程,输出时钟信号会中断,为避免功能异常,低优先级器件会再次加载PROM 版本;

④功能器件FPGA 或DSP 可以任意单独切换软件版本,当高优先级器件切换软件版本后,需要对低优先级器件进行版本状态恢复;而低优先级器件切换软件版本不影响高优先级器件的状态。

2.4 数据包存储设计

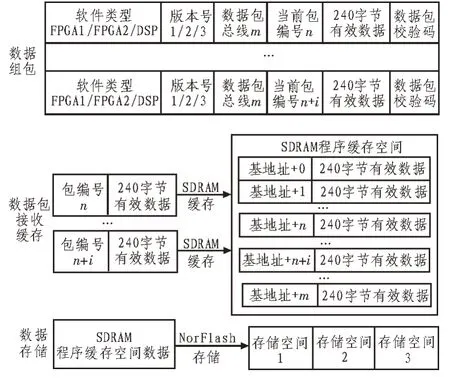

软件在轨更新过程中,程序数据包的存储设计是实现数据包断电续传、部分上注等功能的关键[14-15]。为此,从数据包的组包方式、接收缓存以及存储方式开展设计,设计原理如图6 所示。

图6 数据包存储设计原理

1)数据组包方式

首先在地面完成新版本软件程序的应用验证,然后将程序数据按照约定的数据格式进行组包,数据组包格式包含:软件类型、版本号、数据包总数、当前包编号、240 字节有效数据以及校验码。

2)数据包接收缓存

为了减少NorFlash的操作次数,提高效率,载荷功能单元通过CAN总线接收数据包,并根据数据包编号n直接映射为SDRAM的缓存地址,即“基地址+包编号n”(基地址为SDRAM程序缓存空间的首地址),然后直接缓存240字节的有效数据;由于SDRAM的数据位宽为32 bit,有效数据240 字节是位宽的整数倍,因此确保了SDRAM程序缓存空间地址的连续性。

另外,程序数据的缓存是以数据包为单位,仅与数据包的编号有关,因此一个完整程序数据包的更新,可以一次性完成更新,也可以分为多次更新任务完成,而且每次更新的数据包可以乱序组合。

3)数据存储方式

在此次数据包更新任务完成后,载荷功能单元根据数据存储指令,将SDRAM 中程序缓存空间的所有数据(包括已更新数据和未更新数据)一次性写入NorFlash 的3 个不同的物理空间[16]。

综合上述的组包方式、接收缓存以及存储原理分析,每次程序数据的在轨更新,可以实现对任意数据包的随机更新和存储。

3 结论

该文针对卫星载荷在轨期间任务需求变更以及软件潜在设计缺陷的问题,提出了基于SRAM 型“双FPGA+DSP”硬件架构的软件在轨动态重构设计,在简化硬件电路与功能软件重构方面取得了灵活性与有效性的统一,其加载模式、控制方式、版本切换流程、数据更新存储的设计思路和设计方式,已经在工程中得到应用验证,对航天电子载荷设备的研制具有很好的参考价值。