交错并联H桥结构的独立式电压扰动发生器

汪玉凤,韩金库

(辽宁工程技术大学电气与控制工程学院,葫芦岛 125105)

目前,随着电力电子技术的发展和风电、光伏发电等新能源的广泛应用,电能质量问题已经受到了国内外的广泛关注[1-3],动态电压恢复器DVR(dy⁃namic voltage restorer)、有源滤波器APF(active pow⁃er filter)、静止无功补偿器SVG(static var generator)等电能质量治理设备应运而生[4-5],为了测试和校验这些电能质量治理设备的性能,提供一个电压扰动研究的平台,国内外对电压扰动发生装置也进行了相关的研究工作[6]。

文献[7]提出的传统电压扰动发生器,均是通过切换变压器的变压比来实现电压的扰动,特点是功能简单,但功耗比较大,精度也比较低。近年来,随着电力电子和相关控制技术的发展,相继提出了一些叠加式的电压扰动发生器,其工作原理是将电压扰动发生器输出电压与电网电压进行叠加;文献[8]提出了一种新型多功能的10 kV电压扰动发生器;文献[9]提出了一种级联多电平式的电流扰动发生装置;文献[10]提出了一种基于载波移相的电压扰动发生器;文献[11]提出了一种电能质量扰动发生器,这几种叠加式电压扰动发生器主电路都采用背靠背式H桥结构,虽然这样的结构可以减小电压扰动发生器容量,提高精度,但控制复杂,开关损耗比较大,且叠加式电压扰动发生器的耦合系统可靠性比较低,在实际应用中,启动时不可避免地会对电网产生瞬时冲击。独立式的电压扰动发生器可以避免这些影响,文献[12]提出了一种独立式交错并联的电压扰动发生器,但其整体开关损耗比较大。本文针对文献[12]中独立式电压扰动发生器的开关损耗和控制精度问题,提出了一种差异化结构的设计方法,交错并联H桥提供基波分量输出,在输出电路上串联一组高频H桥;整流部分采用三相半桥式不可控整流电路,既保证了较高的控制精度和功率因数,又可以有效地减小开关损耗[13]。本文中的电压扰动发生器可根据需求实现谐波电压、电压暂升暂降、电压不平衡、波动和闪变等功能,既可以单独产生一种扰动电压,又可以将几种扰动电压进行叠加。

1 工作原理及拓扑结构

1.1 工作原理

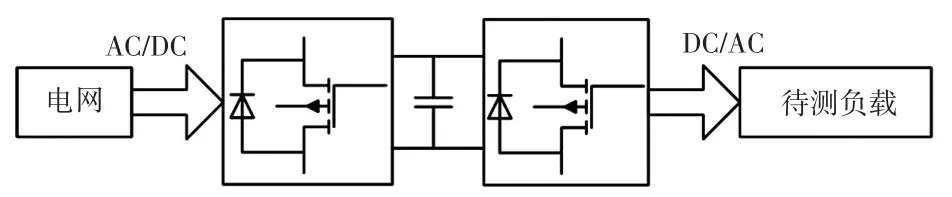

电压扰动发生器的工作原理如图1所示,电压扰动发生器可以等效为一个受控电压源,将电网电压进行整流后,再经过交错并联H桥逆变所需要输出的各类扰动电压。将含有扰动电压的输出电压作用于需要测试的不间断电源UPS(uninterruptible power supply)、APF、SVG、DVR等待测装置或其他负载,通过测试了解这些设备的性能,同时也可对电压扰动进行分析和研究。

图1 电压扰动发生器的工作原理Fig.1 Working principle of voltage disturbance generator

1.2 拓扑结构

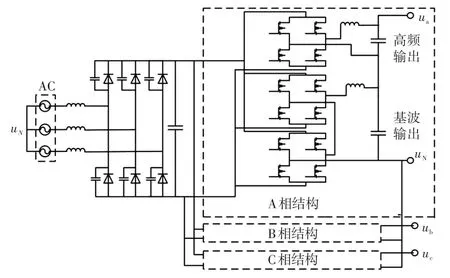

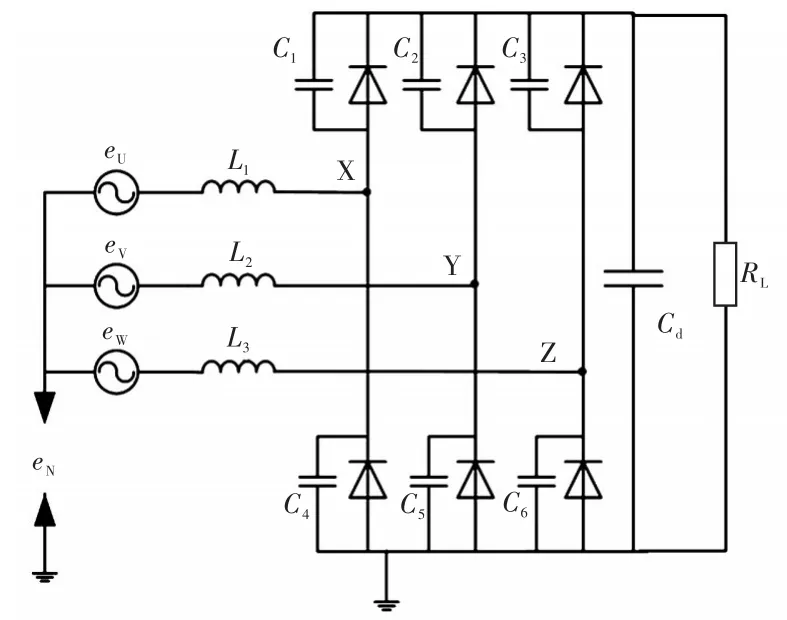

本文研究的独立式电压扰动发生器拓扑结构如图2所示,其中整流部分采用三相半桥式不可控整流电路。三相半桥式不可控整流电路相对于单相整流电路具有容量大、直流电压脉动小、滤波容易等特点,且不需要采用多绕组变压器,减小了装置体积。与一般三相半桥式整流电路不同的是,每个整流二极管并联了一个电容,工作时由于电容的滤波作用,使得输入整流器的高频噪声减少;另外,由于电容的充放电过程,降低了二极管的反向恢复时间和反向电压,因而减小了二极管上的开关损耗,并且这种优势在重载运行下更加明显,配合输入电感和直流侧电容,整流单元的功率因数高达0.995[13]。

图2 独立式电压扰动发生器拓扑结构Fig.2 Topology of independent voltage disturbance generator

逆变部分采用差异化控制结构,即高频部分和基波部分采用不同的模块和控制方法。高频电压利用一组H桥产生,基波电压利用两组H桥并联产生,然后将两者输出电压进行叠加,从而保证更高的输出电压质量[14],该结构提高了等效开关频率,同时降低了每个开关器件承担的电压,在保证系统容量及可靠性的前提下,可以有效地减少了开关损耗。

2 逆变控制策略

2.1 高频模块

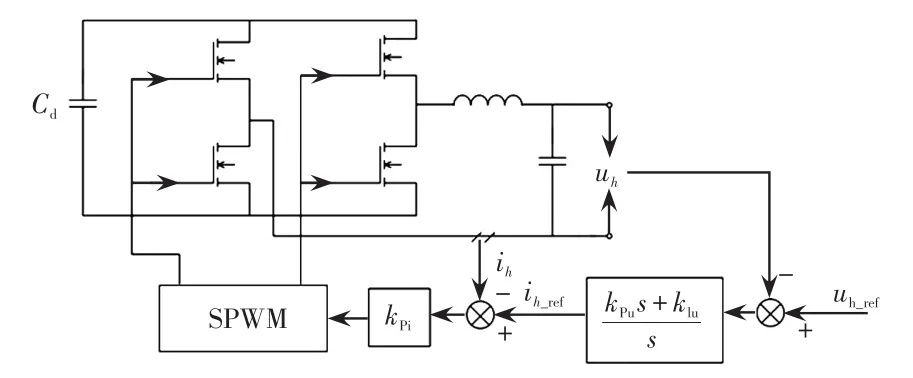

高频部分主要是用于输出高频扰动电压,采用单相H桥结构。高频模块控制结构如图3所示,取输出电压uh和输出电流ih作为反馈量,采用双闭环反馈控制方法,该方法简单易行,鲁棒性强,能够提高系统的动态响应能力和控制精度,适合用于控制本电路。图中,kPu和kIu是输出电压uh的比例和积分系数,kPi是输出电流ih的比例系数。

图3 高频模块控制结构Fig.3 Control structure of high-frequency module

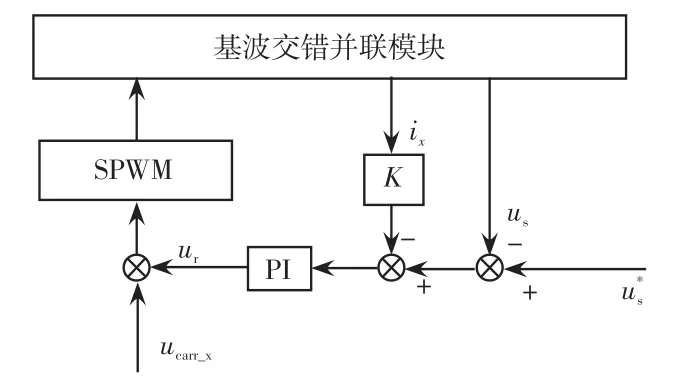

2.2 基波模块

图4 基波模块控制结构Fig.4 Control structure of fundamental wave module

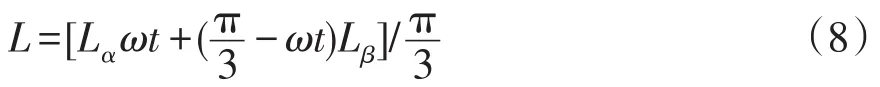

3 参数设计

3.1 直流侧电容

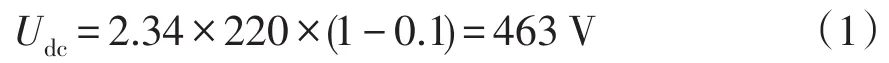

直流侧电容是连接整流电路和逆变电路的纽带,选取适当的电容可保证直流侧电压比较平稳,波动量小。整流电路采用三相不可控整流时,由于器件的导通压降、电容滤波器上的损耗以及死区效应等因素的存在,整流电压实际值会低于理论值,且损耗比率约为10%,则直流侧输出直流电压为

Udc取460 V,根据瞬态能量守恒可得

式中:Pr为整流器容量;ΔUdc为直流侧电压最小纹波,ΔUdc取2%;Ttrans为电容瞬态充放电时间。

最终Cd确定为4 700 μF。

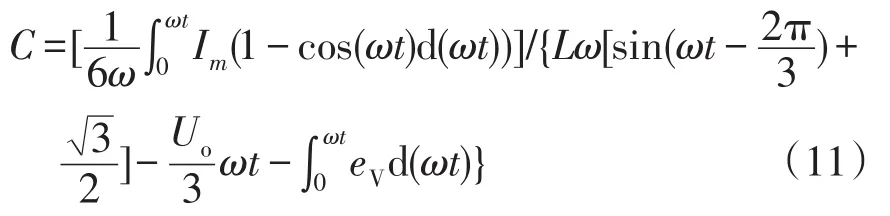

3.2 整流电路

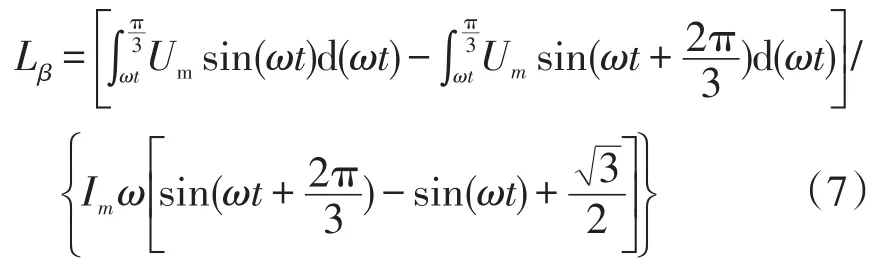

本文中,采用三相不可控整流电路,如图5所示,图中:L1、L2、L3为输入电感,L1=L2=L3=L;C1~C6为二极管并联电容,且它们的参数相同;Cd为直流侧滤波电容;RL为等效阻抗。负载不同,电容工作充放电时间也不相同,根据直流侧负载不同,可分为轻载、中载和重载3种工作模式。根据实际需要,本文对重载工作模式进行研究分析。

图5 整流电路Fig.5 Rectifier circuit

设电容C1充放电所需时间为t,输出电流平均值表达式为

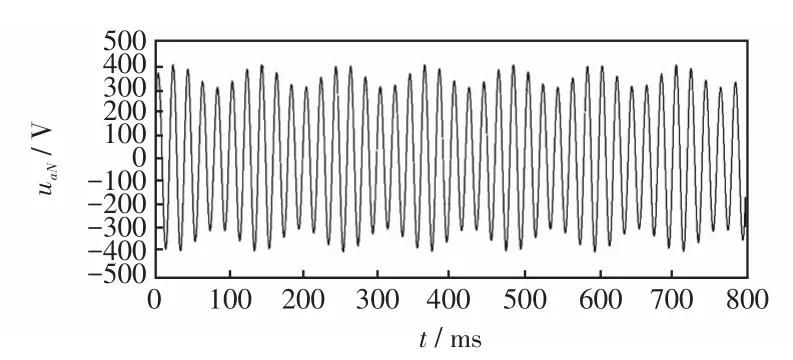

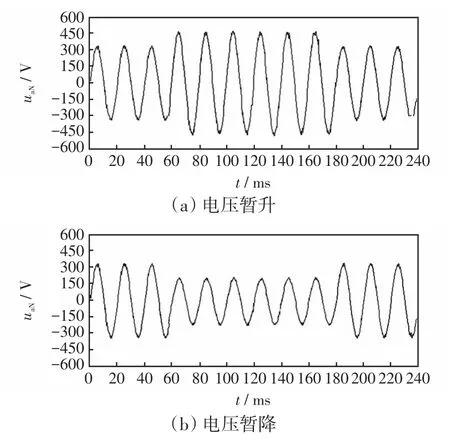

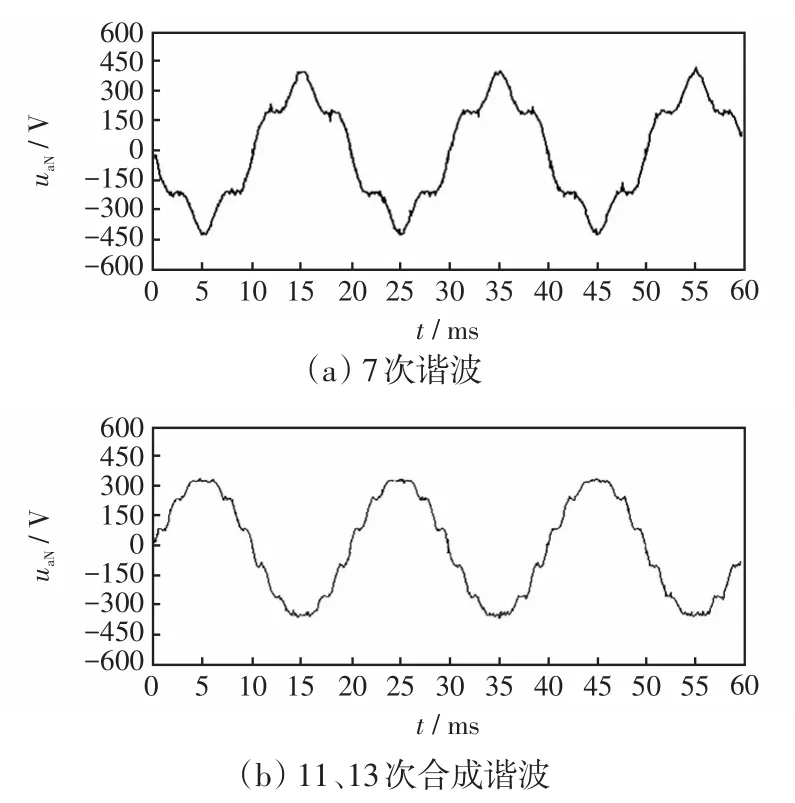

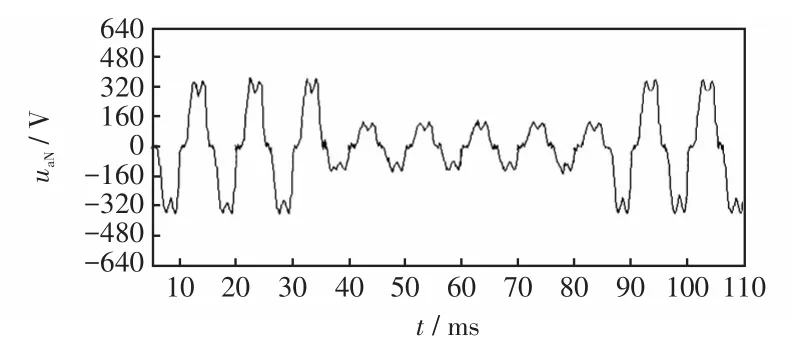

在重载条件下,0 式中:a=U,V,W;A=X,Y,Z。分别将V相和W相的电压和电流代入式(5),得 综合式(6)和式(7),取它们的平均值为最优值,确定整流输入电感为 由式(3)和式(8),最终求得L=245 mH。 并联电容确定,U相所对应的半桥多对应的并联电容在充放电时有 由式(9)和式(10)可得 求得C=1.294 μF ,实际取1.33 μF 。 为了验证本文中理论分析和控制策略的正确性和可行性,利用Matlab/Simulink仿真平台进行了电压波动与闪变的仿真研究,仿真结果以A相电路为例。电网中,8.8 Hz的扰动电压影响最恶劣,所以对8.8 Hz扰动电压进行了仿真。 图6为电压波动和闪变的仿真结果,扰动电压频率为8.8 Hz,幅值为50 V。 图6 电压波动与闪变仿真Fig.6 Simulation of voltage fluctuation and flicker 根据以上分析、参数设计和仿真模型搭建实验样机电路,控制装置由DSP(TMS320F2812)、FPGA(EP2C50F484I8)作为控制芯片,搭建了实验样机。图7为A相电压暂升暂降实验结果,系统正常工作时,输出电压为360 V。 如图7(a)所示,在t=0.06~0.18 s时,A相输出电压发生明显升高,电压幅值上升至504 V,暂升幅度为40%。 如图7(b)所示,在t=0.06~0.18 s时,输出电压发生明显跌落,电压幅值跌落至216 V,暂降幅度为40%; 图7 电压暂降和暂升实验结果Fig.7 Experimental results under voltage sag and swell 谐波电压扰动如图8所示。图8(a)为A相电压含有7次谐波电压扰动的实验波形,7次谐波含量为14.3%;图8(b)为同时含有11次和13次谐波电压的实验波形,11次谐波含量为9.0%,13次谐波含量为7.7%。 图8 谐波电压扰动实验结果Fig.8 Experimental results under harmonic voltage disturbances 三相不平衡电压扰动如图9所示,实验中,三相电压不平衡,系统电压为360 V。可以看出,由于电压不平衡扰动,A相电压上升至384 V,B相电压下降至328 V,C相电压下降至284 V;A相电压与B相电压相位差为126°,A相电压与B相电压相位差为235°。 图9 三相不平衡电压扰动实验结果Fig.9 Experimental results under unbalanced voltage disturbances in three phases 图10所示为谐波电压和电压暂降扰动的复合电压扰动实验波形。由图可知,该装置可实现复合电压扰动。 图10 谐波和暂降复合扰动实验结果Fig.10 Experimental results under compound voltage disturbances of harmonics and sag 针对叠加式电压扰动发生器的缺点,本文提出了一种新型的独立式电压扰动发生器。整流电路采用功率因数较高的三相半桥不可控整流电路,逆变电路采用差异结构,大大减少了开关损耗,基波部分采用交错并联结构,增大了系统容量,提高了系统的可靠性和控制精度。本文提出的交错并联H桥结构的独立式电压扰动发生器实现了输出谐波电压、电压暂升暂降、电压不平衡、波动和闪变等多种电压扰动功能,效果理想,为测试各种电能质量设备和各种电压扰动分析的研究提供了理想可靠的平台,具有较好的研究和应用价值。

4 仿真和实验

4.1 仿真分析

4.2 实验验证

5 结语