基于体区自适应偏置技术的5G基站射频开关研制

宁静, 王彦博, 陈丹妮, 许晟睿, 段小玲

(西安电子科技大学 微电子学院, 陕西 西安 710071)

0 引言

目前投入使用的5G通信基站均以半双工的方式收发移动信号,利用射频开关完成收发动作的切换[1-2]。5G信号的通信质量取决于射频开关芯片的承受功率和插入损耗,平均承受功率越大、插入损耗越低,信号质量越高。早期基站所采用的射频开关大多使用基于GaN工艺的pin结构形式的芯片,最高可承受几十伏的电压,但这种芯片表面积较大,过于占用空间,采购成本高、性价比低。此外,其运行所需电平值高于20 V,增加了系统的整体集成难度[3-5]。为此,本文提出并设计了一种基于体区自适应偏置技术的5G基站射频开关,通过体区自适应偏置技术的开发取消了开关管体区的偏置电阻,引入并联电容补偿技术提高射频开关的输入功率并降低其插入损耗。目前该射频开关已投入使用并在基站的信号稳定和能耗止损方面发挥了较大的作用。

1 射频开关总体设计

1.1 NMOSFET结构

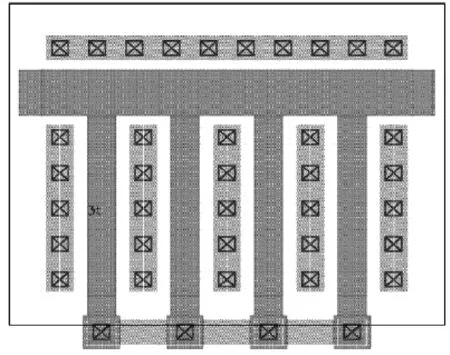

依据SOI CMOS射频工艺的模式,NMOSFET的架构由上到下分别为有源层、绝缘层与衬底层,其中,绝缘层用于阻止其它两层产生电连接,基于SOI CMOS工艺的NMOSFET结构,如图1所示。

图1 SOI NMOSFET结构

电连接的纵向隔离通过SIO2实现,横向隔离则可利用隔离槽、局部氧化、台阶刻蚀等方式实现,SIO2绝缘性能良好,各器件间发生耦合的概率很低,器件绝缘于衬底,杜绝了闩锁效应的发生。

在图1所示的NMOSFET结构下,由于SIO2绝缘层的存在,器件开始运行时残留的硅结构形成了一个电浮空的环境并因此产生浮体效应。在这种情况下漏击穿电压值变小,亚阙值区的电特性会偏离正常特性曲线,为此本文设计了一种T形栅形式的SOI NMOSFET结构,以体接触的方式清理堆积的空穴,从而消除了晶体管内所产生的附体效应,该结构具体形式如图2所示。

图2 T形栅晶体管NMOSFET结构

1.2 总体电路设计

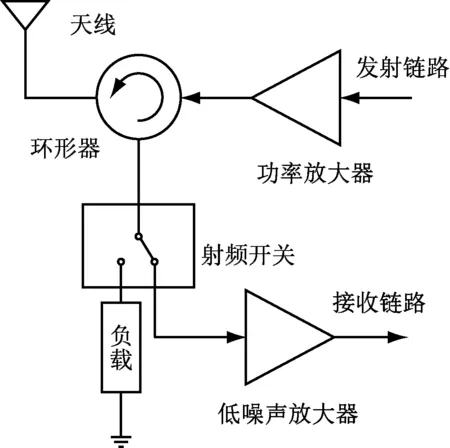

5G基站是在半双工模式下进行信号收发的,收发动作的切换依靠射频开关实现,信号收发过程如图3所示。

图3 基站信号收发原理图

射频开关天线负责接收射频信号,开关发射链路上的承受功率均值在15 W以上,因此芯片的功率承受能力是射频开关的关键性能指标之一。

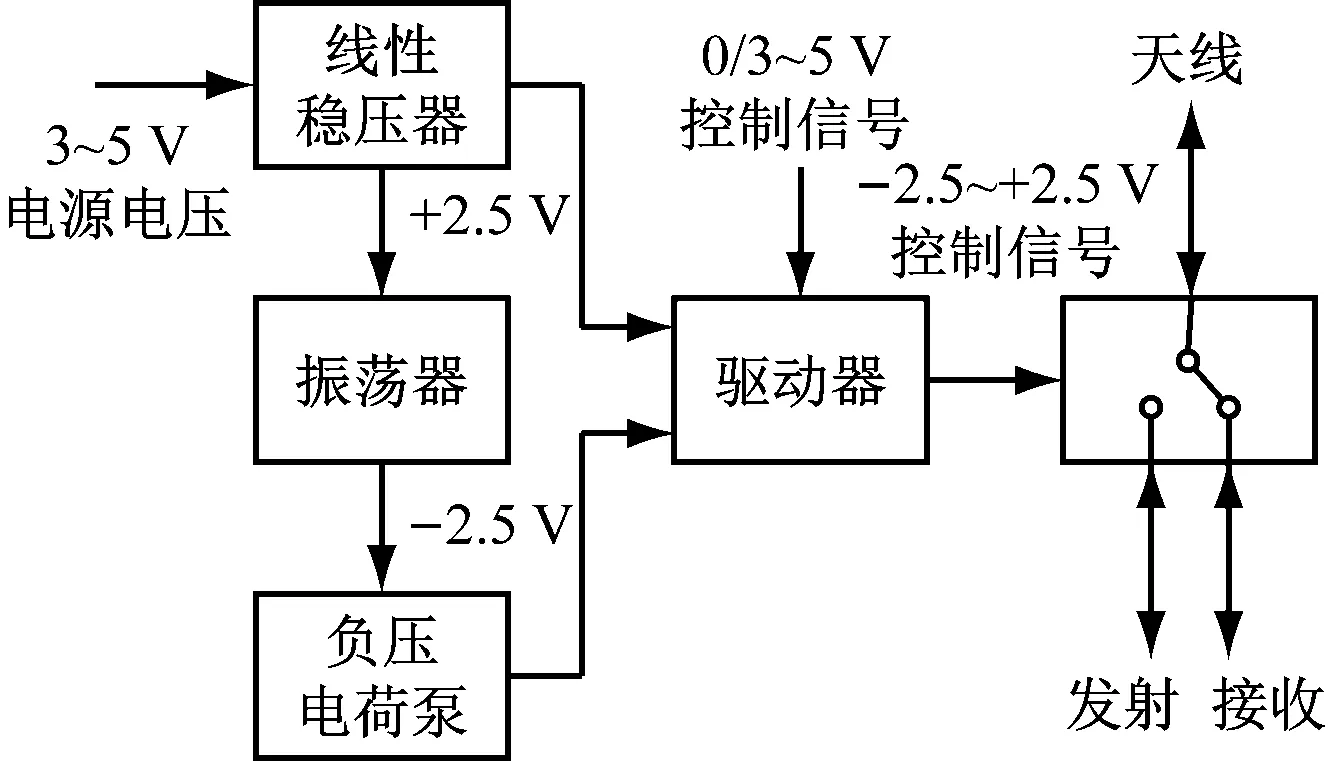

为了实现性能优化,本文射频开关设计的结构形式如图4所示。

图4 SOI射频开关设计结构图

晶体管栅极的运行电压为±2.5 V,在电压大幅摆动的条件下实现了较低的损耗和较好的隔离效果。为了给芯片提供一个简约的工作环境,芯片中集成了驱动器、负压生成电路和线性稳压器,通入3—5 V的运行电压进行信号收发控制。

1.3 射频电路设计

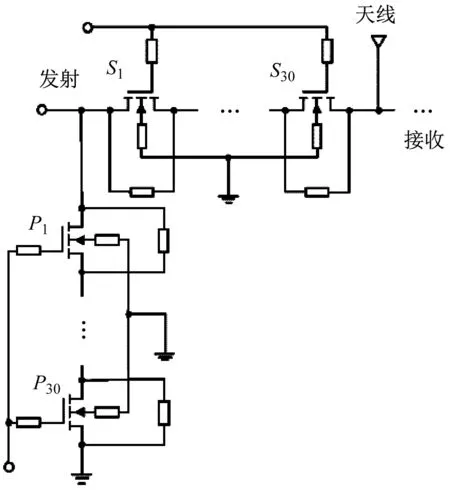

基于SOI工艺的MOS晶体管源所输出的漏击穿电压值在3 V左右,在大功率的输出环境中,为保证晶体管不会被击穿破坏,可以采取多个晶体管分摊电压的方式来增强射频开关功率承载的能力。多晶体管SOI射频开关的结构形式如图5所示。

图5 多晶体管SOI射频开关设计结构图

在射频开关中以并联的方式设置了30个并联开关管,即P1—P30,同时设置了30个串联开关管S1—S30。电路关断时,电路分支中的并联接地电路能够保证电路的彻底隔离,同时,由于寄生电容的存在,插入损耗会有所升高。

对于5G通信基站,每个链路的信号最大收、发功率分别为0.5 W和15 W。系统工作过程中的电压可通过下式进行计算为式(1)、式(2)。

(1)

(2)

式中,Vpeak与Vmax分别代表平均功率对应的最大电压和失配条件下的最高耐受电压。在实际运行中系统失配时VSWR(电压驻波比)值为5∶1,信号发射链路电压最高值为74.5 V,接收链路电压最高值为11.8 V。若单个晶体管分摊电压值为2.5 V,则可通过式(1)、式(2)推算出发射链路所需堆叠器件的数量为30个,接收电路为5个。

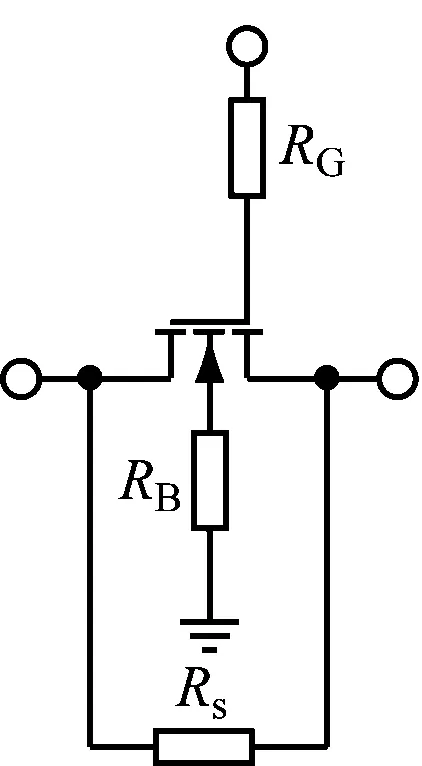

本文基于体区自偏置技术设计了射频开关的电路。具体结构如图6所示。

(a) 传统结构

图6中的RC代表栅串联电阻;RS与RB则分别代表源漏并联电阻和体区串联电阻。在自偏置结构下取消了偏置电阻进行体区的偏置,PMOS晶体管通过二极管连接,而该晶体管又是开关管栅极和体区的连接器件。开关管接通时,MP2沟道的阻抗值相较于传统结构下的偏置电阻阻抗值要高出许多。因而能够实现体区和其余电路的隔离。

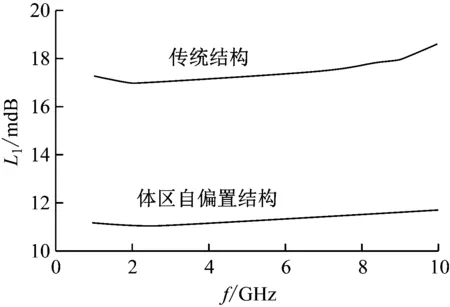

通过仿真实验获得的传统偏置结构和体区自偏置结构的插入损耗曲线,如图7所示。

图7 传统结构与自偏置结构插入损耗对比图

通过两组曲线的对比结果可见,采用自偏置结构能够大幅减小开关管的导通电阻值,降低晶体管插入损耗。

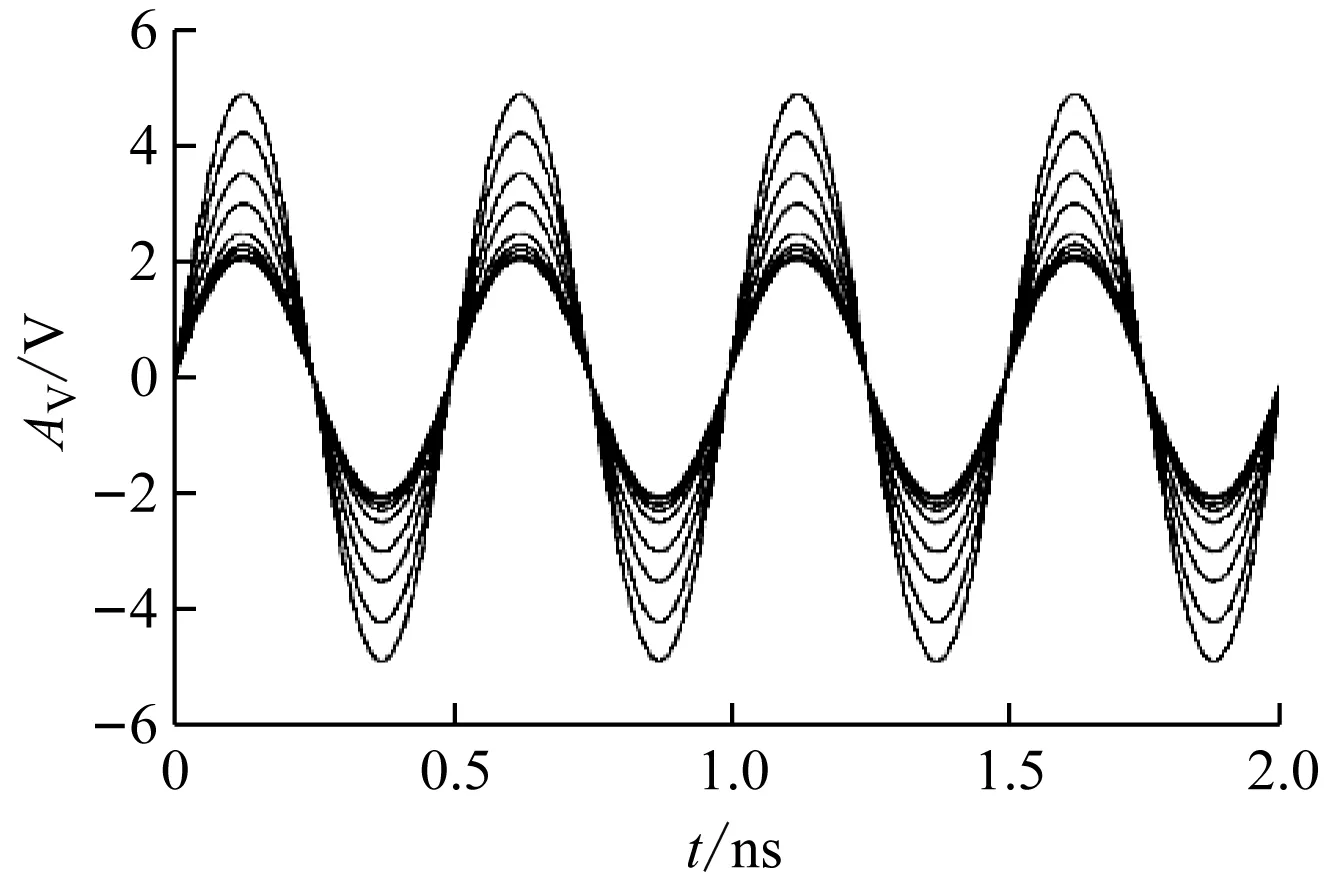

增加发射链路串联分电路中器件的栅宽度能够进一步降低插入损耗,同时,并联分电路寄生电容对链路插入损耗和隔离性能的影响需要缩短发射链路并联分电路的栅宽度。然而,寄生电容效应的发生使得射频开关关闭后的电压震荡幅度很难平均分配至所有的NMOS晶体管源漏。器件体积越小,数量越多,电压的分配越不平均,级数靠前的晶体管分担电压的摆幅越大,级数靠后则对应的分担电压摆幅越小,失配情况下的电压摆幅波形,如图8所示。

图8 电压失配波形仿真图

在失配的情况下,增加串联晶体管的个数或扩大器件的体积都会引起芯片面积的增大,如果持续增加串联晶体管数量会加剧失配的发生频率,无益于射频开关承受功率的提高。

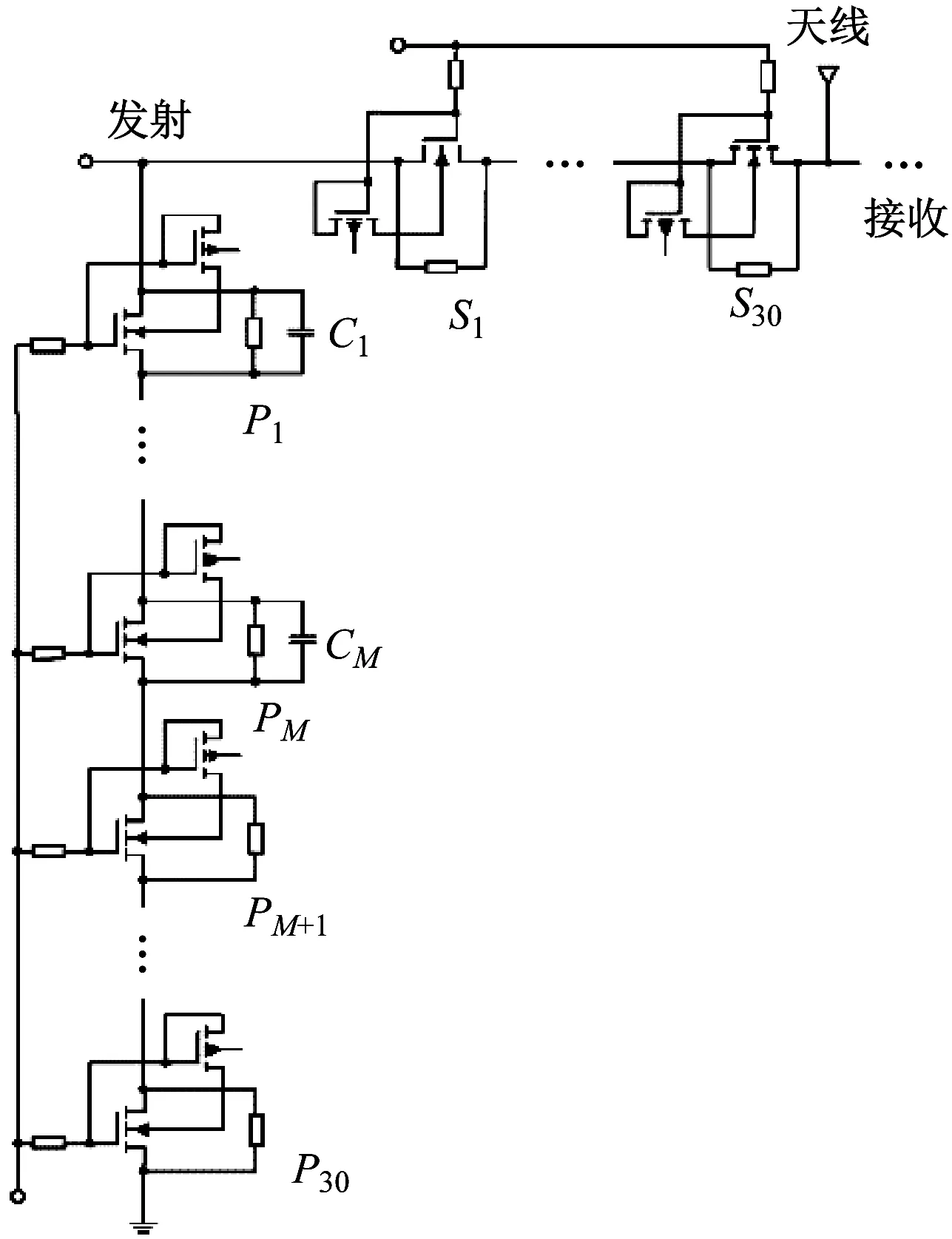

射频开关的芯片在通过天线接收大功率信号时,接收链路的分电路以及发射链路的并联分电路在同时承担高峰值电压震荡。为此本文通过为分电路级数考靠前的NMOS晶体管增加并联寄生电容的方式对射频开关进行了改进设计,且其电容值是逐级减小的。优化后的结构如图9所示。

图9 优化后的射频开关结构设计图

基于寄生参数获得仿真计算结果,进而重新选择电容值C1—CM(M为并联电容级数),以调整各级晶体管分担的电压震荡。获得并联补偿的电压震荡波形如图10所示。

图10 优化后电压震荡仿真波形

由上图可见,每级晶体管的电压震荡幅度差值均小于0.1 V,射频开关电路的功率承载能力大幅增强。

2 改进设计测试及结果分析

经过本文改进设计后的射频开关使用的是180 nm规格的SOI CMOS工艺芯片,该芯片外形尺寸为1.90 mm×0.98 mm。测试用PCB电路板,该板为4层罗杰斯4 350板材结构,底层接地且整体材料为铜,用过烧结工艺与金属盒体连接,以此保证大功率信号输入测试条件下电路板的散热性能良好。射频线的连接方式为共地波导连接,其优势在于能够大幅提高电路板收发信号过程中的隔离度,以获取真实的隔离度测试结果。在电路板的关断端口处安装了50 Ω的电阻,以减少射频信号在周围环境中的反射。

射频开关芯片的运行电压为3.3 V,运行逻辑控制电压为0—1.8 V,模拟电路的工作范围均包含在亚阙值区内,静态条件下运行电流值为90 μA。通电运行后对各项指标值进行采集,其中收发端口的插入损耗数值曲线如图11所示。

图11 收发端口插入损耗

在3.5 GHz的信号收发频率下,收发链路的插入损耗分别为0.43 dB和0.49 dB。

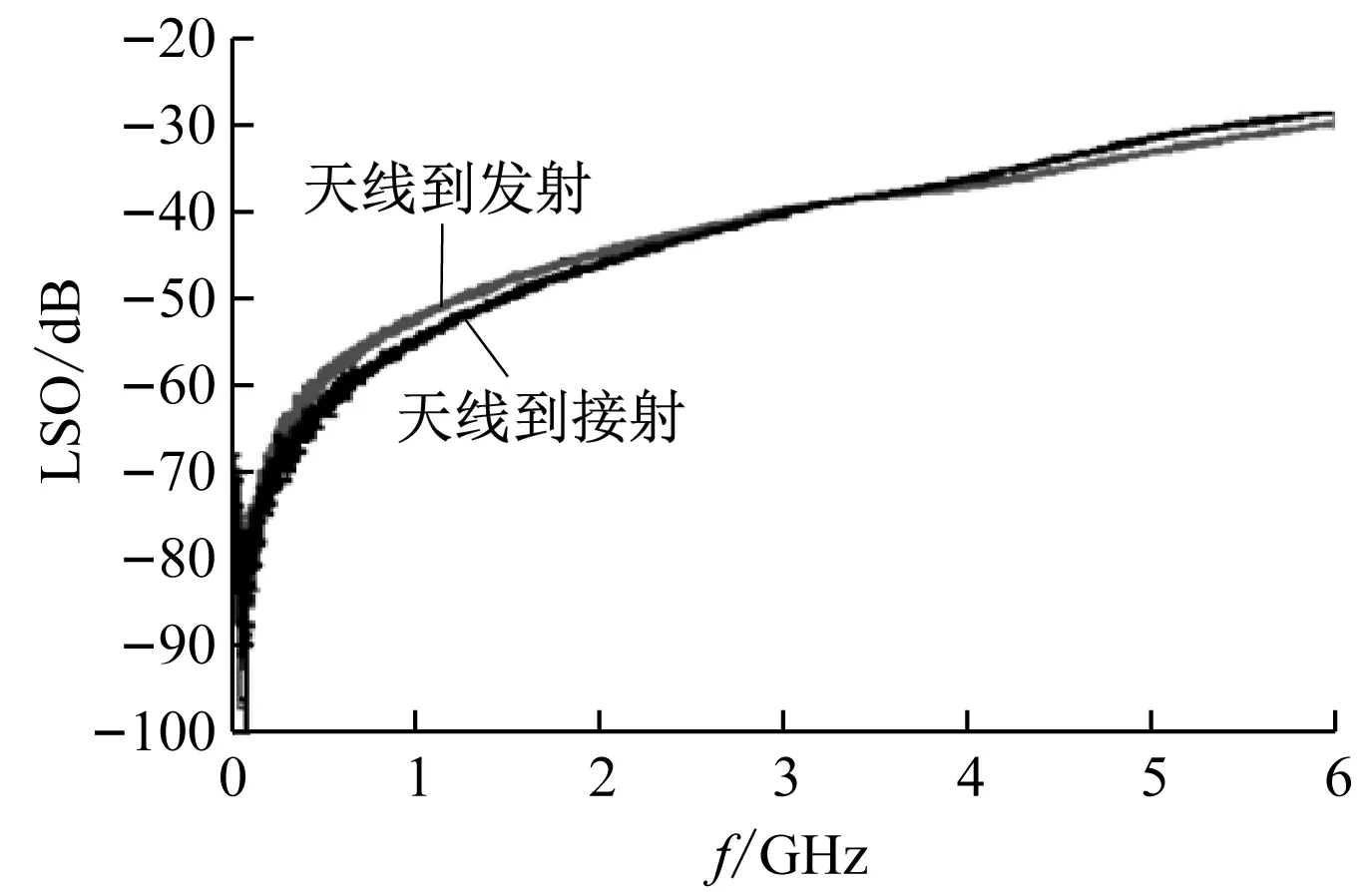

天线收发端口隔离度曲线如图12所示。

图12 天线收发端口隔离度

在3.5 GHz的信号收发频率下,天线收发端口隔离度数值为38 dB。

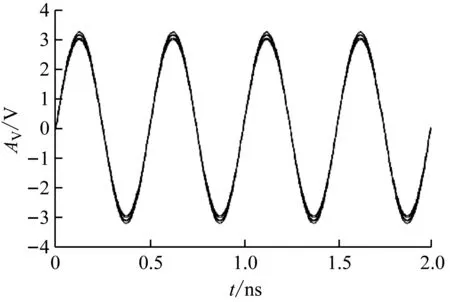

开关切换所需时间如图13所示。

图13 天线收发端口隔离度

由图13可见,本文所设计的射频开关的开关切换耗时为1 μs。

在常温环境下,射频开关发射链路长时间稳定运行时功率最大耐受值超过43 dBm,在0.1 dB压缩点发射功率的峰值为47 dBm;射频开关接收链路长时间稳定运行时功率最大耐受值超过30 dBm,在0.1 dB压缩点发射功率的峰值为31 dBm。

3 总结

本文针对传统5G通信基站射频开关所存在的芯片面积过大、性价比较低、不易集成于系统等问题,本文基于体区自适应偏置技术设计了一种采用SOI CMOS工艺芯片的射频开关。介绍了射频开关的总体电路架构,详细阐述了射频电路的设计过程,以体区自适应技术的应用取代了体区偏置电阻的设置,以并联电容补偿优化方案提高了信号收发链路的功率承受能力,降低了收发端口的插入损耗,最后通过测试数据验证了所设计射频开关的技术先进性和实用性。本文的射频开关优化设计方案能够为5G基站性能的提升与损耗的降低提供有价值的技术参考。