基于LTCC 工艺的低通滤波器设计与实现*

张 博肖宝玉

(西安邮电大学电子工程学院,陕西西安 710121)

随着无线通信行业迅猛发展,射频器件在系统中占据更重要的地位。而滤波器作为射频元件中不可或缺的组成部分,在实现小型化、高性能、集成度高等方面已然成为行业研究的热点与难点,而目前基于低温共烧陶瓷(Low Temperature Co-fired Ceramic,LTCC)工艺设计的滤波器为以上的研究提供了很好的方向。

基于LTCC 工艺设计的滤波器能够很好的实现小型化和高性能,并且采用不同的结构来实现。例如在2018 年[1]中电感采用立体螺旋型(Helical)电感,电容采用垂直叉指电容(VIC)来获得小型化滤波器[1];2019 年[2]中电感采用5 层3D 螺旋结构,电容则采用传统的(Metal-Insulator-Metal,MIM)式结构来获得较大的等效值和Q值[2];在2019 年[3]中电感的设计采用垂直螺旋电感和平面螺旋电感2 种形式,电容采用MIM 结构以实现小型化、高性能滤波器[3]。

应滤波器小型化、高性能的发展趋势,结合微波滤波器理论并使用ADS、HFSS 进行联合仿真,设计出具有高Q值的电容电感,并结合原理图进行合理布局,设计了一款DC-500 MHz 的低通滤波器.

1 低通滤波器电路设计

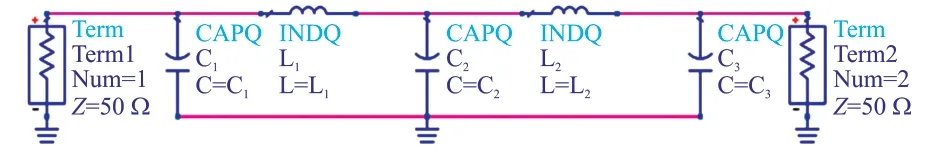

根据低通滤波器的设计指标,选择5 阶等波纹0.1 dB 的切比雪夫滤波器,其滤波器低通原理图如图1 所示,其中的电容电感元件值的相关公式如下所示[4]:

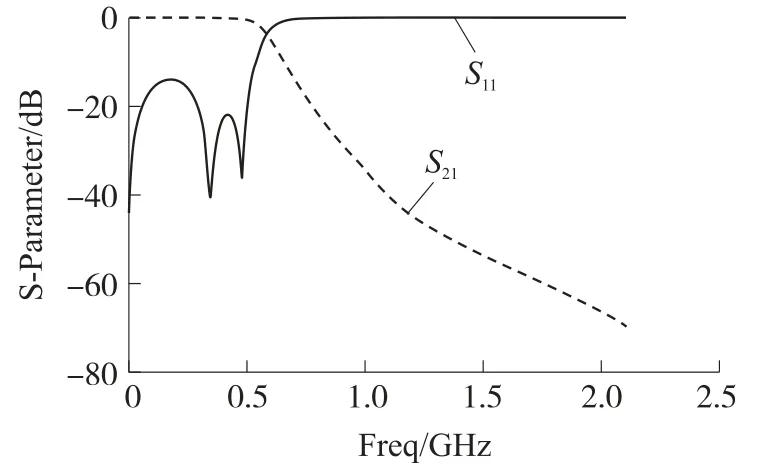

在ADS 中使用Q值模型,其中电容电感的Q值分别设置为150,50。优化得到C1=C3=6.63 pF,C2=12.25 pF,L1=L2=21.76 nH。仿真结果如图2 所示。

图1 DC-500 MHz 低通滤波器原理图

图2 低通滤波器ADS 仿真结果

由图2 可知,在500 MHz 内插入损耗在0.8 dB,通带内回波损耗优于-18 dB,在1 000 MHz 处,带外抑制达到-30 dB,1 500 MHz 处带外抑制有-50 dB。在达到设计指标后参考ADS 给出的原理图,然后在HFSS 电磁仿真软件中建立模型并进行仿真。

2 低通滤波器建模仿真

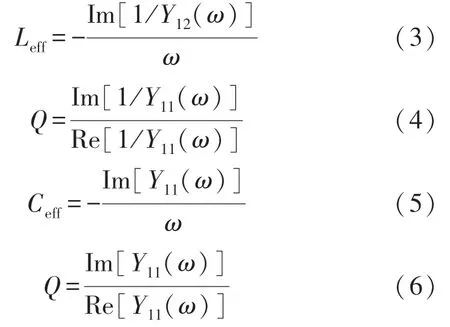

在应用LTCC 工艺制作集总LC 型滤波器时,最关键的是将原型电路图转化为三维立体仿真模型,这样更接近实际情况。在LTCC 滤波器的设计中,真正发挥作用的是元件的有效值,其中电容电感的有效值提取公式如下[2]:

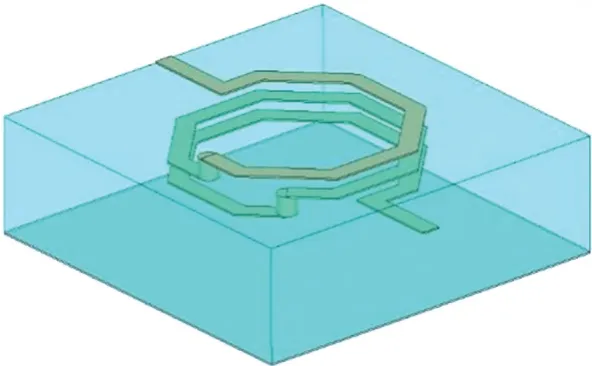

2.1 电感设计

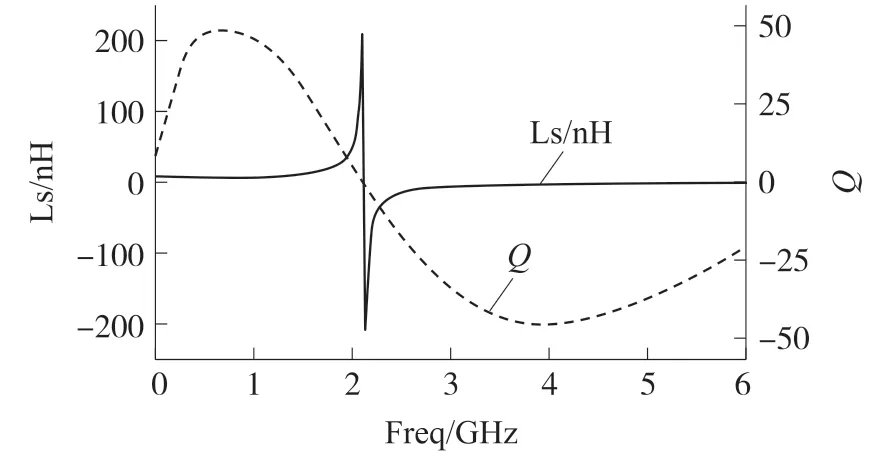

在建模前,首先设计出具有高Q值电容电感。为了不增加滤波器尺寸大小,且结合各方面因素的考虑,电感设计为垂直螺旋结构,电容设计为垂直直插式结构[5]。垂直螺旋电感的三维结构如图3 所示,而图4 为垂直螺旋电感结合式(3)和式(4)计算得到的电感有效值随频率变化曲线。

图3 垂直电感设计结构

图4 垂直电感特征曲线

由图中看出,此电感的自谐振频率点在1.9 GHz,电感有效值在低频处大约10 nH。Q值最高大约为50。分析可知,在物理结构不变的情况下,采用高介电常数材料会降低Q值,这是因为高介电常数材料会导致对地的寄生电容增大,增加了损耗,从而影响Q值。

根据以上分析可知,降低对地寄生电容成为了首要优化目标。在已经确定的介电常数下,使线圈远离地板可以减小对地寄生电容。如图5 所示电感,底部线圈与地板之间的距离是原来3 倍介质层厚度,这样可以很大程度上改善电感Q值,以及有效值[6]。

图5 优化后垂直螺旋电感

观察图6 可知,与之前相比无论是在电感有效值还是Q值方面都有明显的提高。其中有效值提高30%左右,Q值提高到75。

图6 优化后垂直螺旋电感特征曲线

2.2 电容设计

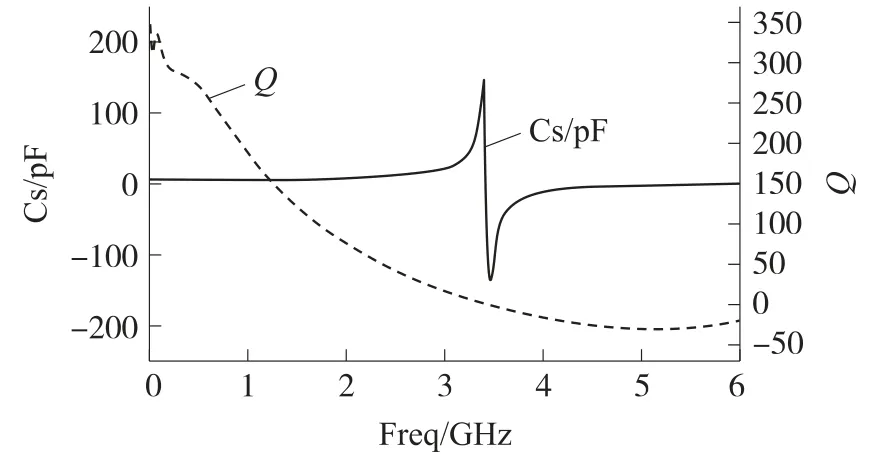

电容的设计可以采用如图7 所示的垂直直插式接地电容,此结构有着单一的通孔和相对较长的金属抽头。然后根据式(5)、式(6)得到电容有效值以及Q值随频率变化曲线。

图7 接地电容设计结构

图8 接地电容特征曲线

分析可知,影响电容有效值的主要因素是接口两端的寄生电感。而寄生电感主要来自于金属通孔和端口处较细的传输线,这就为优化电容性能提供了方向[6]。

基于以上分析,改进后的电容通孔加在平行板边,数量增加到优化前的3 倍,之前用来连接通孔的金属抽头也缩短。

从图10 可以得到,与之前的电容相比,有效值和Q值分别提高了8%和11%左右。分析原因可知电容的品质因数的提高是由于端口间寄生电感减小。

图9 优化后接地电容设计结构

图10 优化后接地电容特征曲线

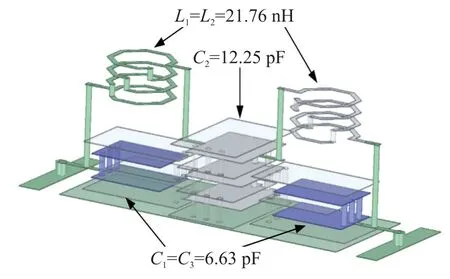

基于以上对于高Q值电容电感设计,此滤波器的电感设计为4 圈,大小为1.4 mm×1.4 mm。电容分别采用4 层介质和6 层介质,尺寸大小分别为:1.45 mm×2.34 mm 和2.56 mm×1.6 mm,整体大小为8.24 mm×2.85 mm×1.164 mm。根据以上分析对电容电感进行合理的布局,得到滤波器三维结构图11,将该模型在HFSS 中进行三维电磁仿真,得到如图12 所示的仿真结果。

图11 500 MHz 低通滤波器三维结构

图12 低通滤波器HFSS 仿真结果

由图12 可知,在500 MHz 处插入损耗为-0.6 dB,带外抑制在1 000 MHz 处有-35 dB,带外抑制在1 500 MHz 处有-55 dB,满足设计指标。从ADS 原理图仿真与HFSS 三维电磁仿真中发现,HFSS 中的仿真结果相对更好一些,这是因为在ADS 中设计电容电感的Q值不是太高,在HFSS 中电容电感的Q值要比ADS 中高。

3 加工与测试

根据图11 滤波器结构图在LTCC 生产线上经过流延、打孔、填孔、印刷线路、叠层、烧结、封端等一系列工艺,制成滤波器实物[7]。

完成加工后的滤波器如图13 所示,将加工后的滤波器焊接在PCB 板上,利用矢量网络分析仪对此滤波器的性能进行测试。

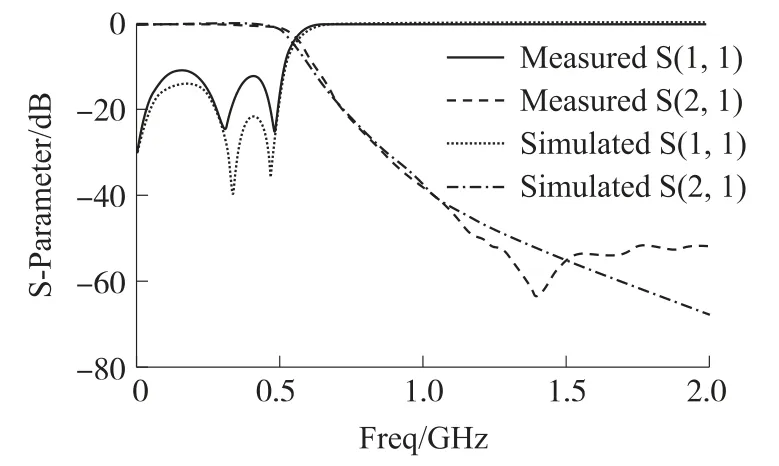

测试结果如图14 所示,可以看到实际测量的插入损耗在500 MHz 处大约为-1 dB,与仿真结果基本吻合。通带内回波损耗在-15.5 dB 以下,在1 000 MHz处带外抑制达到-30 dB。分析结果,可能是因为电容基板重叠面积降低,器件加工材料收缩造成层与层之间有一定的偏移导致电容有效值的降低;而插损的增大在所难免,主要由于Q值的降低以及SMA 接头损耗,焊接带来的不连续等问题都会引入插损。

图13 滤波器实物照片及测试

图14 500 MHz 低通滤波器仿真对比

表1 给出了所提出的低通滤波器与具有类似特性的低通滤波器的主要指标对比。

表1 所研究低通滤波器与其他滤波器对比

从表1 可以比较出,所设计的低通滤波器展现出很好的带内选择性以及较好的带外抑制能力。

4 总结

结合微波滤波器理论和ADS、HFSS 联合仿真技术,设计了一款高Q值电容电感模型DC-500 MHz 的低通滤波器,其中在感值和容值不变的情况下电感电容的Q值分别提高了6%和11%,且滤波器的性能为:通带内插损基本在-0.5 dB,回波损耗在-16 dB 以下,带外抑制为在1 GHz 处有-33 dB,在1.5 GHz 处有-50 dB,且加工生产出的器件实际测试结果也基本符合设计指标,性能良好。