一种具有相位转换模块的全数字延迟锁相环设计*

邱舒晴,张世琳,王少昊

(1.福州大学晋江微电子研究院,福建 晋江 362200;2.中科芯集成电路有限公司,江苏 无锡 214072)

0 引言

锁相技术能够有效地同步不同芯片或设备之间的时钟频率与相位延迟,从而保证数据传输的正确性,因此被广泛地应用到射频收发机、高速通信接口、存储器接口和频率合成器等领域中[1]。锁相技术主要包括锁相环(Phase Locked Loop,PLL)和延迟锁相环(Delay Locked Loop,DLL)等[2]。PLL具有抗干扰能力强、面积小的优势,但是面临着设计复杂、锁定时间较长、需要考虑高阶系统稳定性等设计挑战[3]。相较而言,DLL由于是一阶系统,因此反馈环路更加稳定且易于实现[3]。

全数字延迟锁相环(All Digital Delay Locked Loop,ADDLL)具有锁定时间短,工艺敏感度低、可移植性强等优势[2],能够满足新一代DRAM传输速率高达3.2~6.6 Gb/s的DDR5标准等应用的要求,达到减小芯片内外时钟偏移、实现快速锁定的目的[4]。常见的ADDLL工作模式有开环模式、闭环模式和开-闭环结合模式等。开环模式相位锁定速度快但不具备相位动态保持能力,闭环模式可实现相位动态跟踪保持但锁定速度慢。开-闭环结合模式则结合了前两者的优点。在相位量化方式上,ADDLL中的移位寄存器控制器常采用时间数字转换器(Time-to-Digital Converter,TDC)和逐次逼近(Successive Approximation Register,SAR)等结构[5]。TDC方案可通过产生数字控制字的方式直接调节延迟单元个数,不仅克服了SAR方案中存在的谐波锁定或锁死的问题,还可显著提升相位锁定速度[5]。但是,TDC方案需要较长的延迟链和较多的触发器来对相位差进行量化,因此延迟链电路面积和功耗均大于SAR方案。

本文提出将相位转换技术应用在一种具有可复用双精度延迟线结构的开-闭环结合ADDLL的延迟线电路中,可将粗调延迟链中的延迟单元数量减少一半,并减少TDC电路中所需的触发器个数,节约了电路整体面积和功耗。本文对提出的ADDLL电路进行了闭环模式下的稳态相位噪声分析,并采用SMIC 55 nm工艺库对提出的ADDLL电路结构进行了仿真与性能验证。

1 ADDLL结构及其传输函数模型

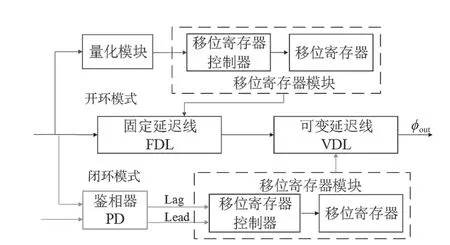

ADDLL电路结构主要由固定延迟线(Fixed Delay Line,FDL)、可变延迟线(Variable Delay Line,VDL)、移位寄存器模块(包括移位寄存器及其控制电路)和量化模块[或鉴相器(Phase Detector,PD)]4个部分组成。

开-闭环结合ADDLL的操作步骤如下:在开环模式下,先在量化模块中快速量化初始相位差进而得到数字控制字,再将数字控制字输入FDL实现快速开环锁定,如图1所示;再通过将量化模块切换为PD即可切换至闭环模式,即可对电路相位延迟变化进行动态跟踪,进而保持相位锁定状态。

图1 开-闭环结合模式的ADDLL结构

在闭环模式下,锁定环路受到器件参数波动、电压变化、温度变化(Process、Voltage、Temperature,PVT)等因素的影响,会导致输入信号相位ϕin与输出信号相位之间相位差产生微小的抖动。PD会将该超前(Lead)或滞后(Lag)的相位差转换为相应的数字控制字。如图1所示,在移位寄存器模块中,控制器先将数字控制字译码,再控制移位寄存器向VDL发送左移或右移动作指令,从而达到调整延迟的目的。该电路结构将VDL的输出信号相位ϕout反馈至PD的输入端,构成闭环负反馈系统。在若干个时钟周期后,该闭环系统可将ϕin与ϕout的上升沿再次对齐,从而实现对输出时钟相位锁定的动态调节与保持。

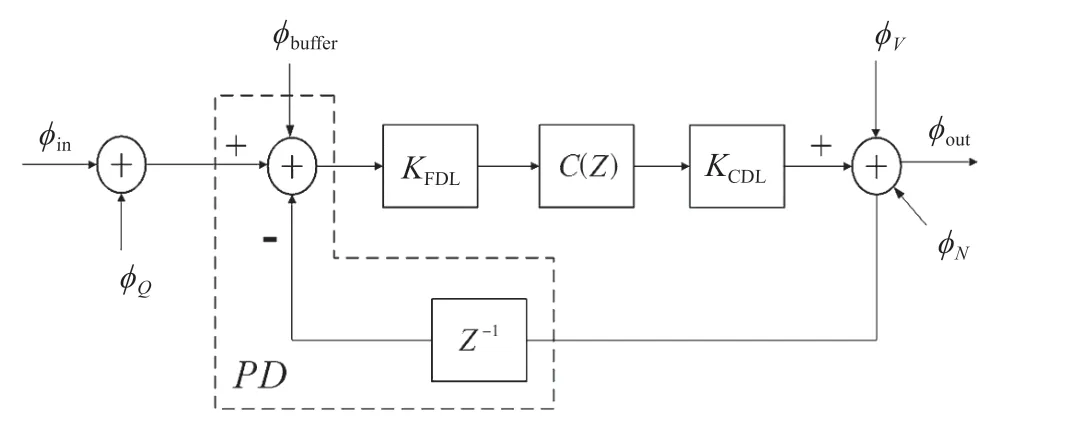

当非线性模型环路锁定并进入闭环跟踪模式时,其平衡状态可以近似成一个线性系统[6],对应的小信号线性模型如图2所示[7-9]。图中,ϕin与ϕout分别表示DLL输入与输出相位变化量,Z-1表示一个参考时钟周期的固定延迟,KFDL与KVDL分别表示FDL单元与VDL单元的增益。若将移位寄存器模块的传输函数C(Z)写作:

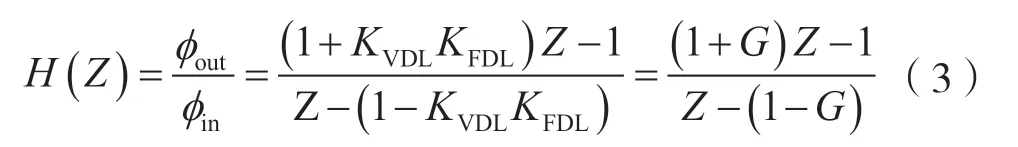

则该线性模型的系统传输函数为[7]:

图2 ADDLL小信号线性模型

对于闭环锁定的ADDLL系统,其噪声主要来源包括外部参考时钟带来的量化噪声ϕQ,延迟单元间的随机噪声ϕN,电压噪声ϕV以及缓冲器噪声ϕbuffer等。由于该ADDLL模型中的FDL、移位寄存器模块、VDL的传递函数都是常数,ϕN和ϕV在ϕout跟随C(Z)快速变化时并没有显著的累积效应[6],且与延迟链相比ϕbuffer等造成的相位偏移通常可以忽略不计[8],因此影响环路的噪声主要由量化噪声ϕQ构成。因此。可认为量化噪声ϕQ传输函数即为系统闭环传输函数[9],令环路增益G=KVDLKFDL,结合式(1)和式(2)可得:

设ωn为环路带宽,ωref为输入参考时钟的角频率,G的频率响应函数可写作[3]:

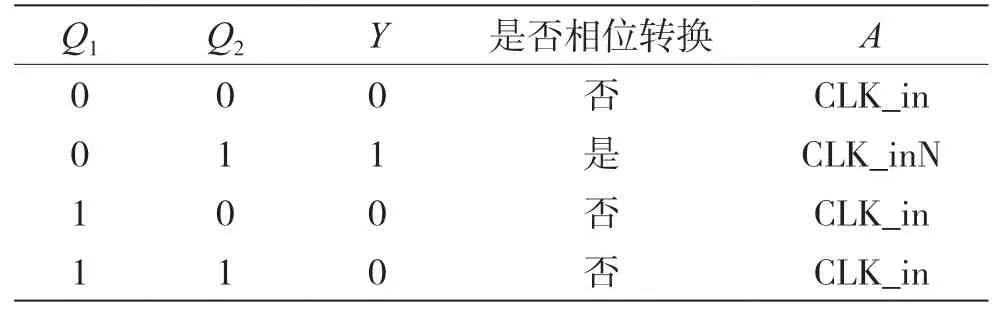

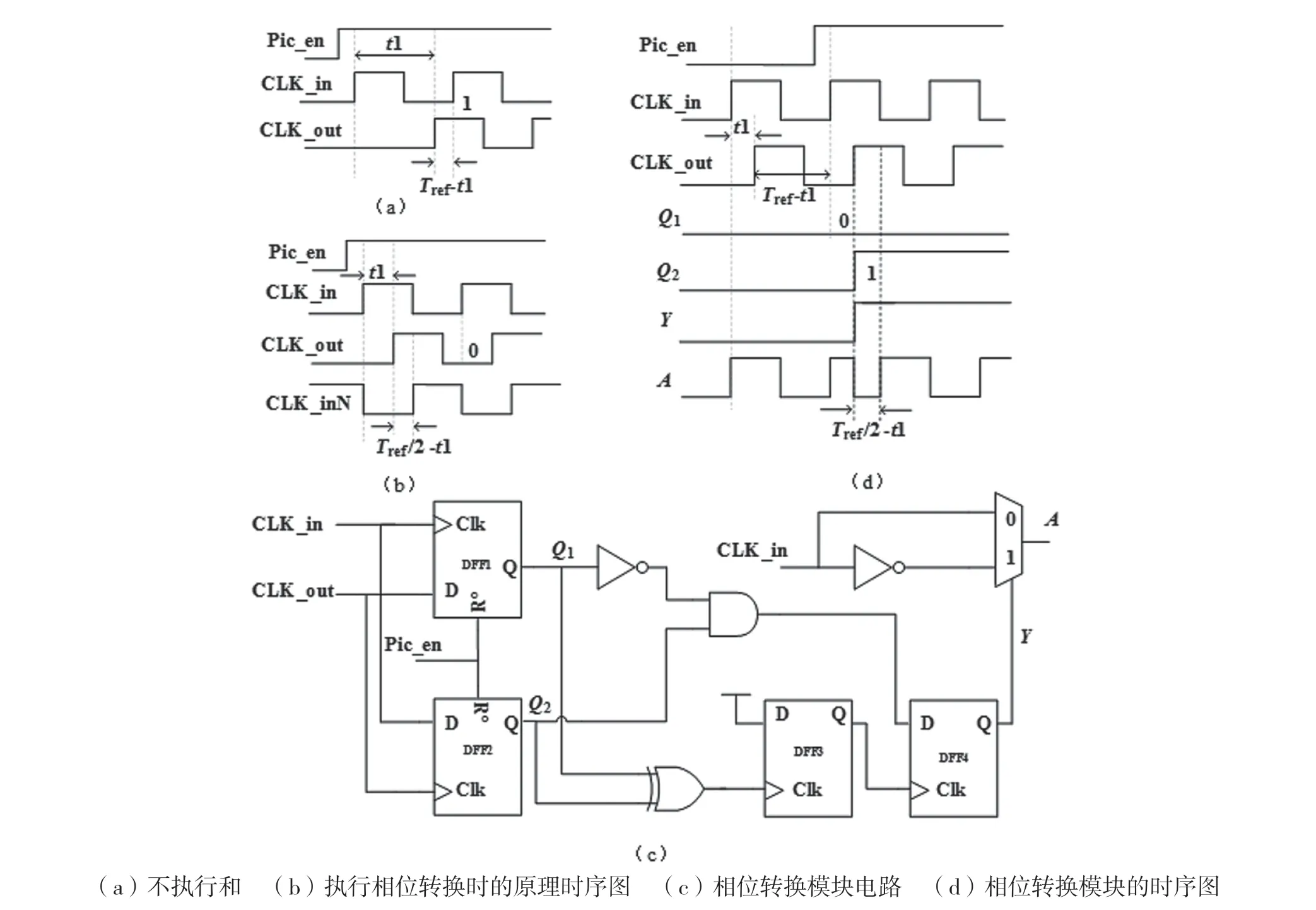

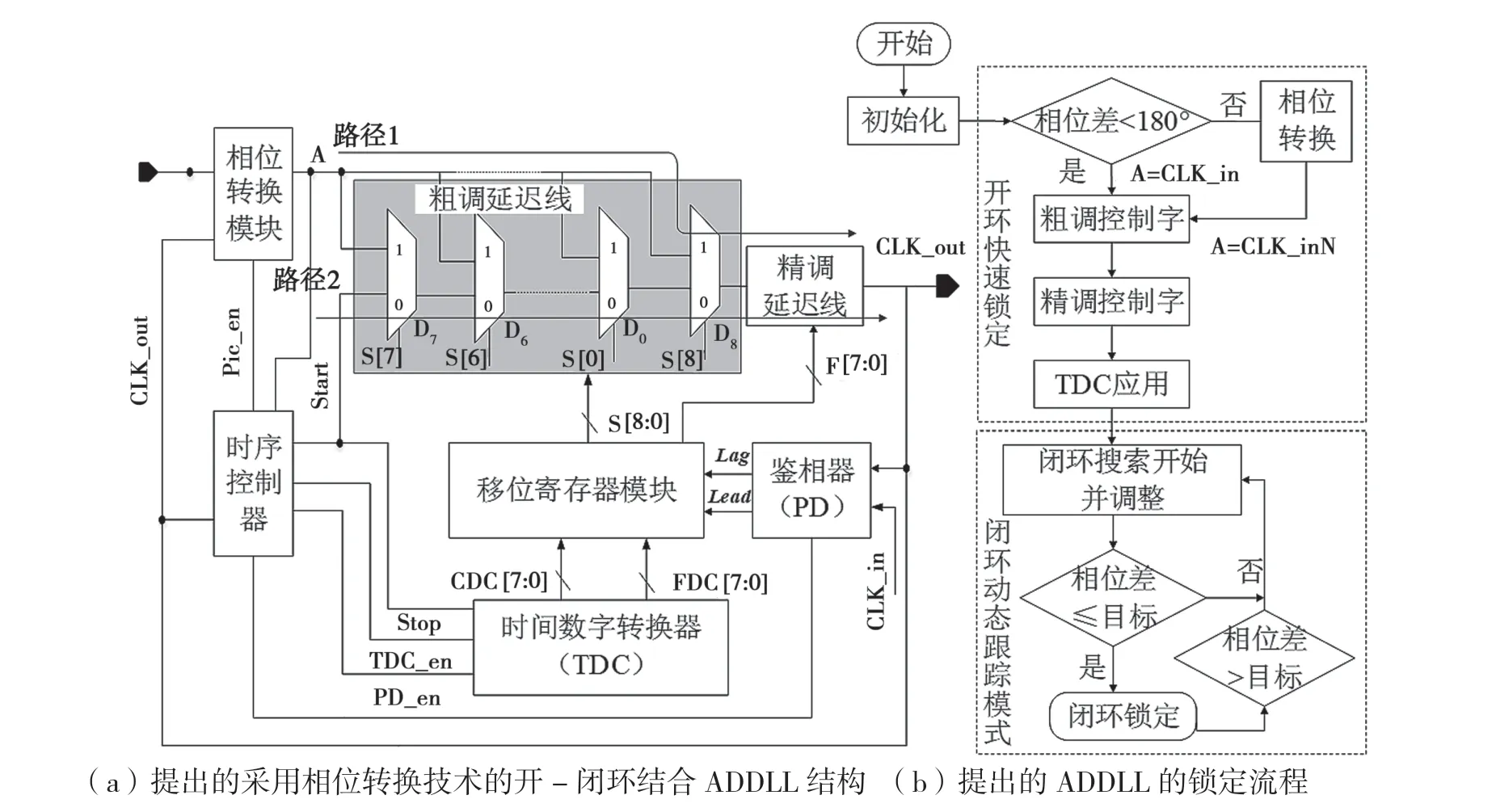

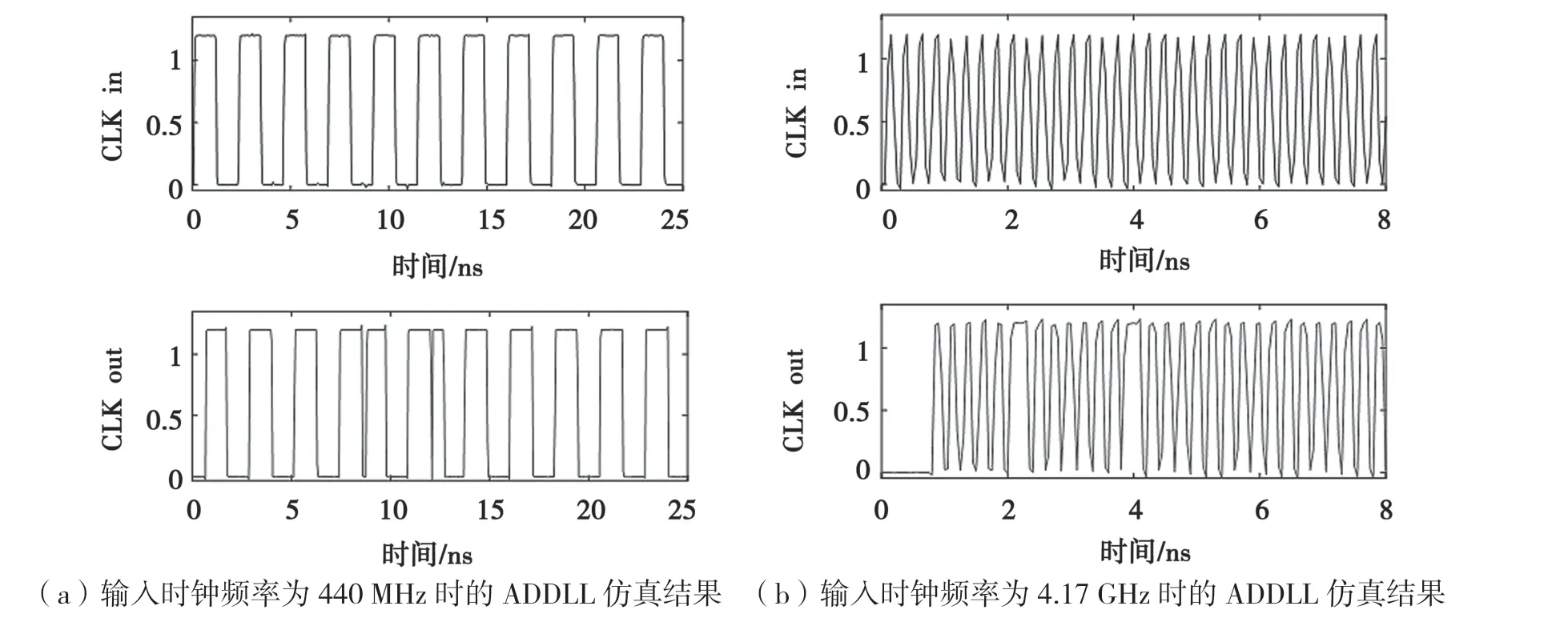

结合式(3)和式(4)可知,ADDLL的离散系统模型在Z域中有一个实数极点,其值为Z=1−G。当0 ADDLL结构中延迟链的最小延迟单元数量决定其环路带宽上限,最大延迟单元数量决定其环路带宽下限。较大的环路带宽不仅有利于实现ADDLL系统的快速相位锁定,还能够有效地增加ADDLL环路的稳定性并抑制低频噪声[3]。然而,受到PVT变化的影响,简单地增加延迟单元数量会增大电路面积和功耗[9]。 本文提出的开-闭环结合ADDLL方案将传统的“FDL+VDL”结构优化为“相位转换模块+基于MUX的粗调延迟线+精调延迟线”的结构,具体工作原理和锁定流程图如图4所示。 相位转换技术最初被应用在模拟DLL中[9],其基本原理如图3(a)和图3(b)所示。考虑输出时钟CLK_out与输入时钟CLK_in之间的初始上升沿延迟为t1,相位转换模块需要将t1与CLK_in的周期Tref进行比较,进而判断是否需要实施相位转换。 当t1≥Tref/2时,意味着CLK_in上升沿来临时CLK_out也为高电平,如图3(a)所示。此时仅需将输入信号CLK_in的相位延迟后即可锁定,相位转换模块无须进行相位转换。 当t1 如在ADDLL的开环锁定模式中添加相位转换模块,TDC的相位延迟范围仅需覆盖[0,π)区间,从而减少一半的延迟链晶体管数量,降低功耗,节约芯片面积。例如,文献[10]所示的16级(16×2+1=33个MUX结构)粗调延迟线的总延迟调节范围为65~2145 ps。增加相位转换模块后仅需8级粗调延迟线(共8×2+1=17个MUX结构)即可实现65~2 210 ps的调节范围。 如图3(c)所示,本文提出的相位转换模块由4个触发器、4个逻辑门和1个选通器组成。输入的CLK_in和CLK_out互为触发器DFF1和触发器DFF2的输入时钟Clk和输入信号D。Pic_en为使能信号,用于控制相位转换模块的开启。DFF1的输出Q1读出CLK_in上升沿到来时CLK_out的电平;同理,Q2读出CLK_out上升沿到来时CLK_in的电平;后续的电路产生的相位转换控制信号Y,即在Y=1时实施相位转换操作,如图3(d)所示令输出信号A=CLK_inN,而在Y=0时输出A=CLK_in。相位控制模块主要指令的真值表如表1所示。 表1 相位控制模块真值表 本文所述ADDLL方案通过初始化、开环快速锁定和闭环动态跟踪这三个阶段实现快速锁定。该方案的结构图如图4(a)所示,其中粗调延迟链由8个双级延迟单元(D0~D7,每个单元2个MUX)和一个单级延迟单元(D8,包含1个MUX)组成。移位寄存器模块负责将从TDC电路输入的粗调控制字CDC[7:0]和精调控制字FDC[7:0]转换为粗调延迟线控制字S[8:0]和精调延迟线控制字F[7:0],并输入延迟链中。 图3 相位转换工作原理 在初始化阶段,相位转换模块输出A=CLK_in。将控制字S[8]设置为高电平,此时信号A沿路径1,经过初始延迟单元(固定延迟单元D8及精调延迟线),产生CLK_out输出。 在开环快速锁定模式下,时序控制模块启动相位转换模块与TDC模块。相位转换模块根据CLK_in和CLK_out的初始相位差判断是否进行相位转换。同时,时序控制模块将相位转换模块输出A和CLK_out的之间的延迟转化为Stop信号和Start信号。Start信号沿路径2先后进入粗调延迟线与精调延迟线,最后成为新的CLK_out输出;Stop信号则通过复用延迟线进入TDC模块用于产生粗调控制字和精调控制字,最后将控制字反馈给移位寄存器模块,在延迟线中实现粗调和精调延迟,实现CLK_out对CLK_in的快速锁定。 在开环锁定后,时序控制模块产生鉴相器PD使能信号PD_en,切换至入闭环动态跟踪模式。当延迟t1发生相位抖动导致相位差大于容限范围时,鉴相器产生可向移位寄存器模块发出超前信号Lead增加延迟链延迟时间或发出滞后信号Lag减小延迟,使输入信号CLK_in与CLK_out重新锁定。 为了验证设计方案的有效性,本文基于中芯国际55 nm CMOS工艺对提出的新型ADDLL结构进行了仿真验证。如2.2节所述,本文设计的单个粗调双级延迟单元的延迟时间为130 ps(单个MUX延迟为65 ps[10])。由于固定延迟单元D8至少需要接入1个双级延迟单元,因此开环总延迟范围为195~ 1140 ps。由于相位转换模块可将环路总延迟范围增大1倍,因此该设计方案可以提供439 MHz~5.13 GHz的工作频率范围。图5(a)、图5(b)分别为输入时钟频率为440 MHz和4.17 GHz时的仿真结果。 图6展示了时钟频率为1.25 GHz、初始延迟为300 ps时的锁定过程及峰值抖动。由于300 ps 图4 提出的ADDLL电路结构及流程 图5 ADDLL工作频率仿真结果 图6 提出的ADDLL在1.25 GHz下的锁定过程仿真 在接下来的闭环跟踪模式中,在对锁定后的CLK_in施加量化噪声ϕQ后,输出CLK_out测得的最大峰-峰值抖动值为1.05 ps,如图7所示。 图7 1.25 GHz时钟频率下测得的输出时钟峰-峰值抖动 接下来,在1.25 GHz时钟频率下,对初始延迟为150 ps、450 ps和600 ps的情况进行性能仿真验证,所提出的ADDLL结构均能在10个时钟周期内实现对相位的快速锁定。 表2给出了本文提出ADDLL方案和相关快速锁定ADDLL方案的性能参数比较。文献[5]提出的基于TDC开环结构的ADDLL尽管锁定速度快,但无法对锁定后的相位实施动态跟踪。文献[11]中的方案实现了对PVT等因素导致的相位抖动的动态跟踪调节,但工作频率范围受延迟单元精度、面积等因素的限制仅为25~ 300 MHz,不符合新一代高速集成电路芯片的要求。文献[12]通过在ADDLL中采用可变SAR的混合搜索算法方案解决了SAR谐波锁定和锁死的问题,但环路锁定速度较慢,需要38个时钟周期。本文提出的ADDLL采用了相位转换技术将粗调延迟链中的延迟单元个数减半,1.25 GHz工作频率下,仅需10个周期就能实现快速开环锁定,还能在闭环模式下实现相位动态跟踪保持,峰-峰值抖动仅为1.05 ps。 表2 ADDLL性能比较 本文提出了一种采用相位转换技术的全数字延迟锁相环设计方案,在一种具有双精度延迟线的开-闭环结合ADDLL中增加了相位转换模块,有效地将ADDLL结构中的延迟单元的数量减少了一半,并减少时间数字转换器所需的触发器个数。在中芯国际55 nm工艺下的仿真结果表明,在440 MHz~4.17 GHz的频率范围内,该DLL能够在10个周期内实现输入信号和输出信号的同步。此外,本文提出的ADDLL结构还可以通过改变延迟单元的延时和数量进一步调整优化工作频率范围和分辨率,以适应不同领域对高速集成电路芯片交互中的时序同步的要求。2 基于相位转换的ADDLL电路设计

2.1 相位转换模块的设计

2.2 ADDLL电路功能实现

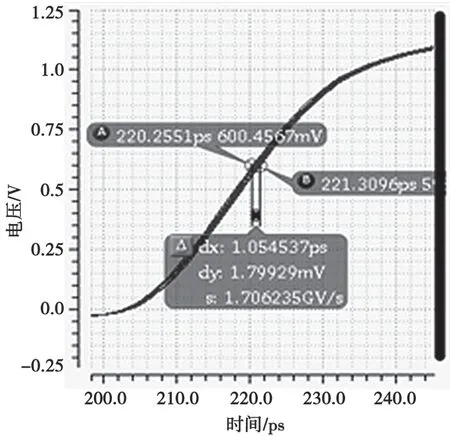

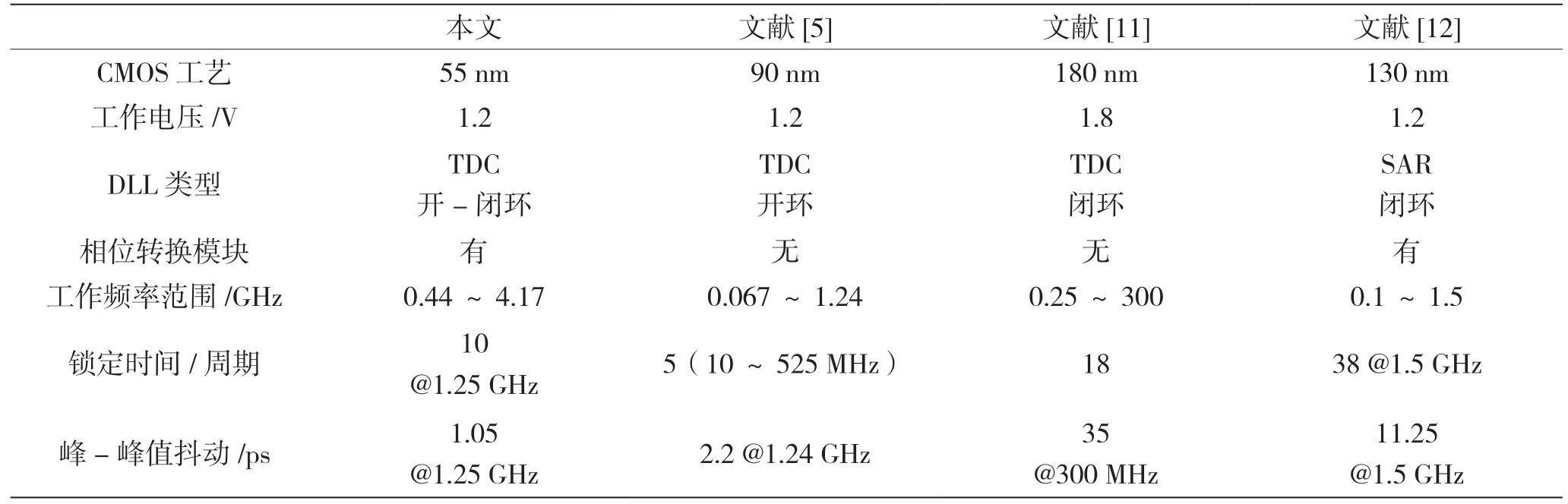

3 ADDLL电路仿真结果与分析

4 结语