一种高压模拟开关漏电失效解决方法

黄立朝,阎燕山,程绪林,张如州

(1.中科芯集成电路有限公司,江苏无锡 214072;2.中国航空无线电电子研究所,上海 201100)

1 引言

高压模拟开关具有传输速度快、导通电阻小、通道隔离度高等特点,因此,其广泛用于微处理器中的交互接口或其他开关应用电路中。模拟开关工作时不仅可以传递模拟信号,还可以传递数字信号,但值得注意的是,模拟信号的变化值(幅度)必须在正负电源电压之间,又由于电路是高压模拟开关,故其传递的信号幅度变化范围就可扩展得很大[1]。

模拟开关主要功能是实现信号的不失真传递,在开关上消耗的功耗很小,实现信号传输系统的低能耗和高精确性。随着模拟开关工作电压越来越高,在高压工作状态下容易出现端口漏电流过大而失效。然而芯片漏电失效的原因往往不易把握。本文提出了一种快速定位漏电失效的方法,通过分析漏电现象,提出解决漏电问题的一种通用方法,对漏电相关问题具有较强的参考价值。

2 电路结构原理及漏电测试方法

2.1 电路介绍

本文针对的这款16 选1 高压模拟开关采用0.8 μm FEOL with 0.35 μm 40 V power analog process工艺生产。芯片版图采用1P2M 布线,版图面积为3.825 mm×2.825 mm。电路内部主要采用的器件包括高压NMOS 管、高压PMOS 管、高压阱电阻及高压BTJ 管等[1]。以上类型的器件,其工艺耐压可达40 V 以上,是构成本模拟开关电路的核心器件。本文介绍的这款高压模拟开关电路基于BCD 工艺设计制作,性能可靠,实用性强[2-3]。

2.2 电路结构原理

本文介绍的高压模拟开关电路的结构框图如图1所示。高压模拟开关电路共有16 路输入S1~S16,1 路公共输出端口D;通过4 位地址寄存器A0~A3 来选择某一路输入通道输出到公共输出端。另外,电路共有3个使能控制信号,分别是读写信号WR、使能信号EN以及清零信号RS。清零信号RS 的优先级最高,当RS为低电平时,所有通道关闭无输出;读写信号WR 具有次优先级,当WR 为低电平时进行寄存器读写操作,否则输出状态保持;最后是使能信号EN 为低电平时输出零,高电平时正常工作(有效)。开关电路的整体工作原理是:在读写信号WR 的上升沿时,4 位地址寄存器A0~A3 存入一组被选择的地址;在读写信号WR 的下降沿且使信号EN 有效时,4 位地址寄存器中的地址被译码器翻译并通过电平转换电路来选中控制某一路通道链接到公共输出端D,从而实现16 选1的多路复用功能[4]。

2.3 电路漏电测试示意图

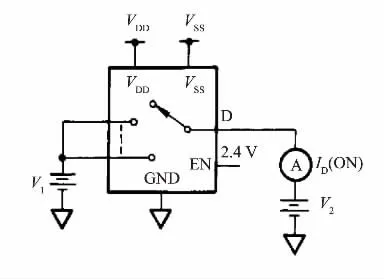

在模拟开关的应用中,最重要的指标之一是开关通道之间、输入端与输出端之间两个隔离度。理想的开关特性是各个通道之间是隔离独立的,开关导通时内阻很小,相当于导线;而开关断开时,相当于断路,漏电很小。通常试验中,针对高压模拟开关的漏电测试均是在输入与输出端口之间施加测试电压,并保持开关处于断开状态[5]。图2 是测试开关断开时的漏电测试图。

图1 总体电路框图

图2 漏电测试原理图

3 电路漏电试验及失效分析

3.1 电路漏电试验

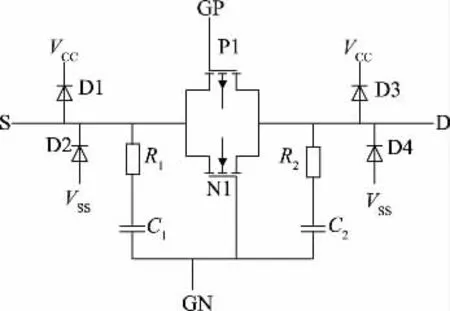

为了表述通俗易懂且不影响漏电试验测试覆盖性,采用单个CMOS 开关来说明漏电测试原理,如图3 所示。电路漏电测试结果及加电方法为:

(1)正电源电压VCC=15 V,负电源电压VSS=-15 V;

(2)负电源电压端口GN 为-15 V,正电源电压端口GP 为15 V,保证P1 与N1 为关断状态,S 端口不与D 端口接通;

(3)保持输出D 端口悬空,输入S 端口加一个直流测试电压,电压从-15~15 V 逐渐增大;

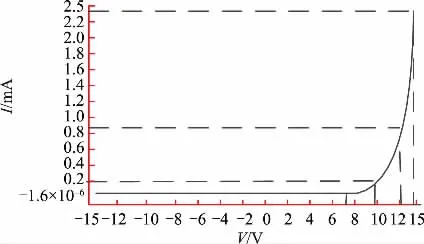

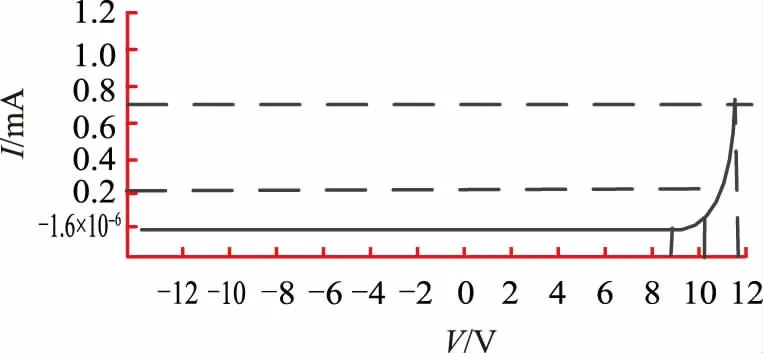

(4)测试结果是:当S 端口为负压(-15~0 V)时,S端口的漏电流为几个纳安级别,达到指标要求;当S端口的正压较小(小于9 V)时,漏电流也为几个纳安级别;但当S 端正压超过9 V(S 端对VSS的压差超过24 V 左右)时,S 端口的漏电流急剧增大,出现毫安级别的大漏电流,类似于二极管反向击穿的I/V 特性,且S 端口的漏电流流入了负电源电压VSS处,如图4 所示;

(5)由于S 与D 端口对称,按照上述方法,S 端口悬空,P1 与N1 关断,D 端口加测试电压,最后测试结果类似,均出现端口S/D 与负电源电压VSS之间的压差超过某个值(24 V)时,就出现漏电流急剧增大的现象,重复试验后问题复现。另外,每次出现端口漏电现象后,关闭电再重启,重复上述试验,能得到同样的试验现象,因此,可初步判断出引起该漏电电流急剧增大的击穿现象是可恢复的[6]。

图3 单个开关的电路结构

图4 开关S 端漏电测试扫描曲线

3.2 电路漏电失效分析

高压模拟开关电路内部均采用耐压高达40 V 的器件,理论上端口之间的压差低于40 V 时,不应该出现较大的漏电流。而从漏电试验结果看,S/D 端口与负电源电压VSS之间的压差超过24 V 时,就发生漏电流急剧增大的现象,且该现象可逆。从图4 可以看出,该漏电曲线类似二极管雪崩击穿的特性曲线。因此,推测电路中可能有某个器件的寄生PN 结耐压不够,达不到40 V(寄生二极管雪崩击穿)而产生大电流漏电[6]。为了验证这个对失效原因的推测,本文按如下步骤进行了具体测试分析。

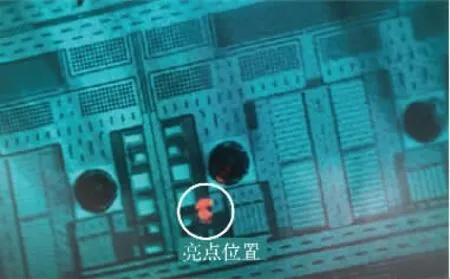

(1)进行EMMI 测试,找到漏电具体位置。根据图4 采用的漏电加电测试方法,采用红外热成像EMMI技术对芯片具体漏电位置做精确定位,试验获得的照片如图5 所示。照片显示的亮点在下半部居中位置,靠近PAD 处。

图5 EMMI 亮点位置

(2)通过EMMI 测试,获得了漏电器件的精确位置(图5 中亮点),接下来和实际版图布局进行比对,初步确定产生漏电失效的器件是PAD 附近的阱电阻Rn-well,见图6。

图6 漏电器件在版图上的位置

(3)漏电失效器件的确定通过聚焦离子束(FIB,它通过离子枪加速离子束后作用于芯片表面,可对芯片进行切割等操作)试验进行。经过EMMI 测试和版图比对已经初步定位发生漏电失效的器件,为了最终确定,需通过FIB 试验来验证。FIB 能把阱电阻单独切割出来,然后只针对该阱电阻进行耐压测试。本文通过在阱电阻一端口(另一端口悬空)与衬底P-sub 之间加测试电压,扫描获得端口电流与测试电压之间的I/V关系曲线,如图7 所示,从图中可以看出:当电阻端口与衬底之间的压差低于24 V 时,端口漏电流为纳安级别;但当压差超过24 V 后,端口漏电流急剧增大,表现出二极管反向击穿的I/V 特性。对比图7 与图4 的试验结果,漏电性能几乎一致,表明发生耐压不足的漏电失效的器件就是阱电阻Rn-well[7]。

图7 FIB 后开关S 端漏电测试扫描曲线

(4)初步分析器件漏电失效的原因。综上所述,已经明确了发生漏电失效的位置为阱电阻Rn-well,接下来分析器件漏电的原因。器件耐压不足导致漏电发生,同时漏电的I/V 曲线表现出二极管击穿的特性,并且可以恢复。因此,可以推测出阱电阻的器件纵向结构中有寄生的PN 结耐压不足,如图8 所示。在Rn-well的纵向结构中,如果N 阱层NW(N 型阱区)和衬底层BP(P 型衬底区)之间耐压不足,这两个层次类似于一个反偏二极管,当它因耐压不足而发生雪崩击穿时[6],是可能导致漏电失效的。

图8 Rn-well的纵向结构

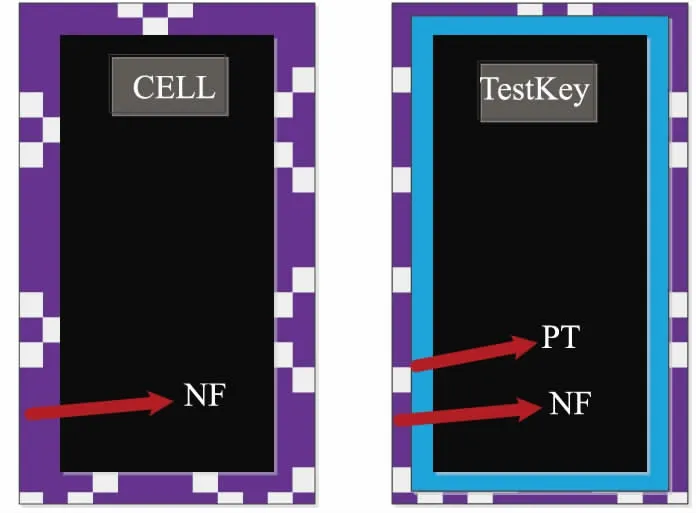

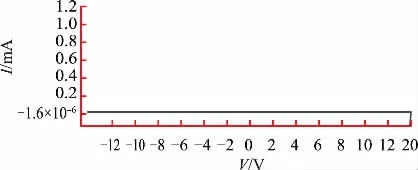

(5)解决漏电失效问题。通过前文一系列的试验和分析,已经找到了发生高压漏电失效的器件,并初步分析了漏电原因。通过修改器件工艺结构,总结出现的失效现象,通过相关的工艺测试试验,充分了解漏电失效问题的各个因素,逐一排查导致器件失效的工艺方面的原因,最后找到问题所在。器件工艺库中的阱电阻Rn-well的NV(有源场注入区)层次有误,其场注入NF 区和有源区(Testkey)靠得太近,几乎重合,两者的浓度均较高,引起耐压不足,如图9 所示。最终通过扩大NF 区和有源区之间的间隔以提高击穿电压后,便有效解决了高压漏电失效问题。如图10 所示,器件在-15~15 V 宽电源电压范围内,漏电均处于纳安级别,满足设计指标要求。

图9 Rn-well高压漏电失效原理

图10 Rn-well改进后的漏电测试曲线

4 结论

在一款采用40 V 高压BCD 工艺的16 选1 高压模拟开关中,实际测试时发现因器件耐压不足引起漏电失效问题。文章从试验现象入手,通过EMMI 亮点同实际版图进行对比,精确定位出现漏电失效的器件,再经过FIB 试验,最终确定漏电失效器件。然后,通过对漏电失效器件的工艺结构进行分析,推测出失效原因,确定了漏电失效的根本原因是器件工艺结构层次问题,PT 和NF 层叠间距太窄导致器件耐压不足,造成器件漏电现象,最终通过扩大NF 区和有源区间隔的方法成功解决了漏电失效问题。通过该分析方法和技术改进可以解决后续类似问题,提高解决问题的效率。