基于RISC⁃V 处理器的卷积加速SoC 系统设计

张坤宁,赵 烁,何 虎,邓 宁,杨 旭

(1.清华大学微电子学研究所,北京 100084;2.北京理工大学软件学院,北京 100081)

0 概述

自2012 年AlexNet 获得ILSVRC 比赛的冠军之后,卷积神经网络(CNN)开始引起关注,并逐渐应用于图像分类和检测、人脸识别以及语音识别等领域[1-3]。然而,随着深度学习技术的快速发展,CNN在提高识别准确率的同时,网络深度也在不断加深,结构更加复杂化,导致网络的计算量剧增[4-5]。通用处理器在处理大量且繁杂的卷积计算时效率十分低下,且能耗开销较高。因此,设计专门用于加速卷积计算的硬件架构尤为必要。

RISC-V是由加州大学伯克利分校(UCB)提出的一种开源精简指令集架构[6],全球的开发者能够共同参与研发。RISC-V 由3个基本指令集和6个扩展指令集组成,在实现基本指令集的前提下可以根据自身的实际设计需求灵活选择相应的扩展指令集[7]。与主要用于桌面计算机的x86架构以及用于嵌入式设备的ARM 架构相比,RISC-V架构具有通用且灵活的优势,并且开源设计的方式也避免了专利保护和高额授权费等给开发者造成的研发难度,因此,RISC-V近年来备受研究人员的关注并取得了一定发展[8-9]。

CNN 中的计算以卷积计算为主,同时还包含一些其他类型的计算。因此,通常采用软硬件协同设计的思路,即设计专门的加速器来提高卷积计算的效率,再使用通用处理器完成一些在网络中所占比例很小、无需在硬件架构中实现的计算。目前,基于卷积加速器的软硬件协同设计主要通过在FPGA 平台中构建SoC系统来实现,所用的通用处理器大多基于ARM架构[10-12],虽已出现一些将RISC-V 处理器与卷积加速计算相结合的设计[13-14],但总体而言数量仍然较少。

本文基于RISC-V 指令集架构提出一种顺序双发射的超标量处理器设计方法,并构建以动态量化的8 bit 定点数据作为输入的卷积加速器结构,对卷积循环计算顺序进行优化以进一步提高卷积计算的效率。在此基础上,构建包含RISC-V 处理器和卷积加速器的SoC 系统,将其部署在FPGA 平台上并运行VGG16 网络,以实现加速效果。

1 基于RISC-V 的处理器设计

1.1 RISC-V 处理器概述

RISC-V 包括一个基本的整数指令集,所有基于RISC-V 开发的处理器都必须实现这一基本指令集。此外,RISC-V 还有足够的操作码空间用来定义其他基于用户需求的自定义指令[15]。目前,UCB 已经设计出一款名为Rocket Chip 的64 bit、包含5 级流水线的顺序执行RISC-V 处理器,其使用台积电40 nm 工艺流片后与采用相同工艺的ARM Cortex-A5 相比,功耗和面积均约降低一半[16]。在与卷积加速器结合方面,YANG等人对Eyeriss结构进行改进,设计一种基于RISC-V 处理器的卷积加速结构,并在Rocket-Chip Simulator 中对该卷积加速结构进行仿真[17]。LI 等人在FPGA 平台上实现“RISC-V 处理器+卷积加速协处理器”的SoC 系统,其实现了32 bit 单精度浮点卷积运算的加速效果[18]。

1.2 顺序双发射超标量RISC-V 处理器

本文基于RISC-V 指令集标准,提出一种顺序双发射的超标量处理器设计方法。处理器支持RV32IMAFC指令集,具有32 bit 的整数指令和地址空间,采用9 级流水线架构,并支持动态分支预测技术,处理器对外还兼容AXI4 接口,能够原位替换ARM A 系列的处理器,从而为构建包含RISC-V 处理器和卷积加速器的SoC系统提供支撑。

处理器整体架构如图1 所示,包含指令缓存模块、指令获取模块、指令分发模块、指令解码模块、指令执行模块、数据缓存模块、数据传输模块以及寄存器堆等。处理器通过指令缓存模块从存储器中读取指令并组成指令包,指令包经拆分后发送到指令解码模块和指令分发模块。在6 个执行单元中,A0 和A1 两个算术逻辑单元支持加法、减法、乘法、移位和逻辑运算等操作,LD和ST 负责完成存储器与处理器之间的数据访存,DIV单元执行整型除法和取余计算,FPU 负责完成单精度浮点数的加法、减法、乘法、除法和开方等运算。处理器采用9 级指令流水线,主要分为指令获取、指令分发、指令执行和写回4 个步骤。具体地,首先将128 bit 的指令包进行拆分,然后对指令进行解析并根据指令的类型将其发送到相应的执行单元,最后将执行结果写入寄存器堆或存储器中。

图1 基于RISC-V 指令集的处理器架构Fig.1 Architecture of the processor based on RISC-V instruction set

2 卷积加速器设计

2015 年,ZHANG 等人基于roofline 模型提出卷积加速器的设计分析机制,对计算吞吐和数据带宽等进行定量分析[19]。2016 年,麻省理工大学提出的Eyeriss 深度学习处理芯片采用行固定的方式实现数据复用[20]。目前,卷积加速设计主要围绕以下方面展开:基于CNN 网络中输入特征映射和卷积核多通道的特性,利用FPGA 中的计算资源进行并行计算[21];基于有限的片上存储资源,对输入和权重数据进行分块,并通过设置片上缓存来暂时存储分块数据;通过设计特定的循环展开计算顺序,实现片上缓存数据的复用,从而减少片上缓存与片外存储之间的访存次数并实现高效的并行计算[22]。

本文设计的卷积加速器由计算单元、片上缓存和控制单元3 个部分组成,其整体架构如图2 所示。计算单元主要由乘加阵列、BN 计算模块、定点处理模块、激活模块以及池化模块组成,是完成加速计算的关键部分。片上缓存调用FPGA 的BRAM 资源,暂存来自DDR 的输入特征映射、权重数据以及卷积计算结果。控制单元主要产生一些控制卷积计算过程的信号,以保证计算过程准确有序。

图2 卷积加速器架构Fig.2 Convolution accelerator architecture

2.1 计算单元

卷积计算由乘加阵列完成,计算单元由若干个乘法器和加法器组成。卷积计算的效率提升主要通过阵列之间的并行计算以及阵列内部的循环展开乘加计算来实现。并行计算需要对输入图像映射和卷积核在各个维度上进行分块。鉴于主流的卷积神经网络的输入、输出通道数均为16 的倍数,因此,本文将乘加阵列在输入和输出通道维度上的分块尺寸确定为16,即其包含的乘法器和加法器的个数为256。此外,考虑到测试集中图片的尺寸为224×224,对于输入特征映射,本文将其在行、列2 个维度上的分块尺寸均设置为7。图3 所示为乘加阵列的结构。

图3 乘加阵列的结构Fig.3 Structure of the multiplier and accumulation array

在循环展开乘加计算顺序的过程中,采取将卷积核与输入特征映射的点乘运算进行分解的方式,即固定一个卷积核元素,令其完成全部分块数据中所有需要其参与的乘法运算,然后再移动到下一个元素。在本文设计中,输入特征映射的行、列分块尺寸均为7,在数据填充尺寸为1 的情况下,一个卷积核元素将全部输入数据扫描一遍共需49(7×7)个时钟周期,因此,尺寸为3×3 的卷积核与分块数据的一次中间结果计算共需9×49 个时钟周期。

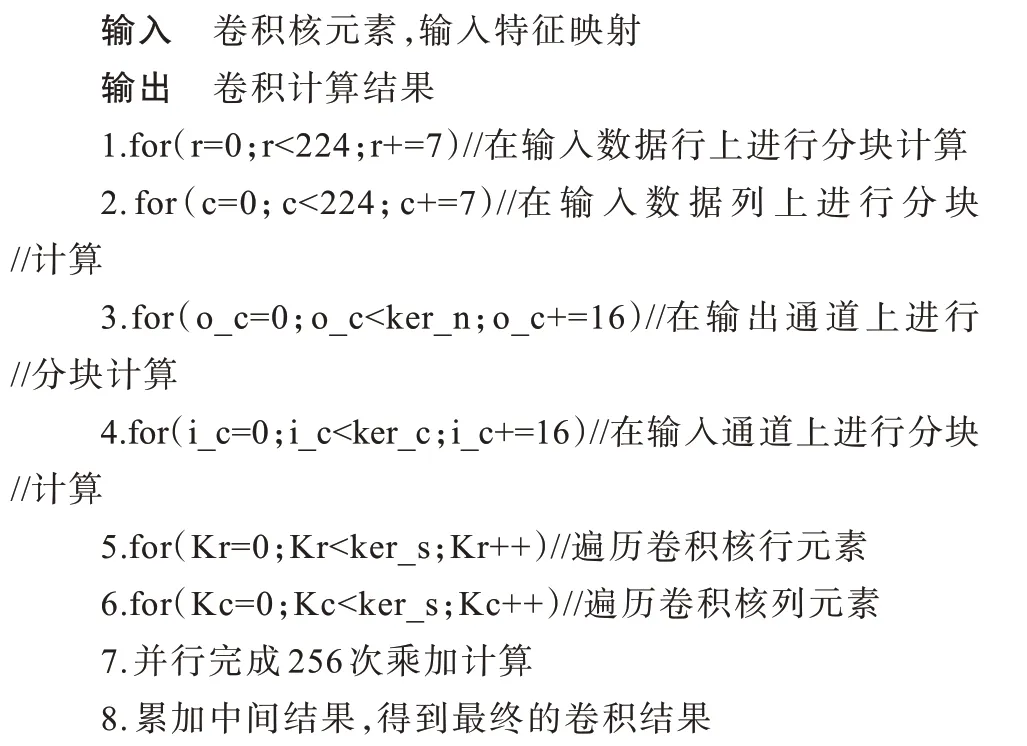

算法1 描述了上述并行计算和循环展开计算的过程。这种令单个卷积核元素与整个分块数据依次进行乘法运算的方式,优势在于既复用了卷积核数据,又令乘加阵列中的计算不受卷积核尺寸的限制,只需将卷积核的尺寸信息通过控制器传给计算单元,便可设计简单且通用的控制逻辑对片上缓存中的数据传输以及乘加阵列中的计算进行控制,从而大幅提升卷积加速器的通用性。

算法1卷积计算算法

2.2 片上缓存

如图2 所示,加速器中设置了输入缓存、权重缓存和输出缓存,同时在计算单元中还有用于存储卷积中间结果的缓存以及用于存储池化计算模块输入数据的池化缓存等。通过缓存数据,能够减少加速器与DDR 之间的数据访存次数,从而实现数据复用并降低由传输数据所产生的能耗[23]。

上述缓存均工作在ping-pong 模式下,设置两块尺寸相同的缓存,在一块缓存与DDR 进行数据交互时,另一块缓存则向计算模块传输数据,这种方式能够充分利用数据传输的时间,提高加速器的运行效率。

2.3 控制单元

控制器一方面接收总线传递的关于网络每一个计算层各个维度上的分块尺寸信息,另一方面又在计算过程中产生计算开始及完成的信号、片上缓存读写数据的使能信号以及地址等。

3 SoC 系统设计

在Vivado 2018 的IP Integrator 中,将RISC-V 处理器和卷积加速器分别封装为具有AXI 总线master接口的IP,与DDR、DMA、AXI 总线、时钟与复位模块、BRAM 控制器以及UART 等模块IP 共同组成能够运行完整CNN 的SoC 系统。CNN 中的卷积、激活、BN 计算、池化以及全连接计算等都能在加速器中完成,并且循环计算顺序经过优化使得加速器的乘加阵列更具通用性,可支持不同网络中各种尺寸的卷积核与输入特征映射的卷积运算。此外,网络中数据填充与分块、softmax 层计算等耗时较短的操作由RISC-V 处理器来完成。DMA 控制DDR 通过总线向片上缓存传送数据,同时API 函数中给出的一些控制信息也通过总线传递给加速器。图4 所示为本文SoC 系统架构。

图4 基于RISC-V 处理器和卷积加速器的SoC 系统架构Fig.4 SoC system architecture based on RISC-V processor and convolution accelerator

4 实验结果与分析

本次实验推理计算所用的数据集选用来自ImageNet ILSVRC2012 的100 张图片,每张图片的尺寸为224×224×3。运行的网络选用VGG16,共包含13 层卷积层和3 层全连接层,总参数量达132 MB,每完成一张图片的推理计算要进行15.84G 次乘加运算。

在前文所述的SoC 系统中添加约束并进行布局布线等操作,得到各项资源利用情况,如表1 所示。RISC-V 处理器和卷积加速器的工作频率分别为100 MHz 和300 MHz。将生成SoC 系统的bitstream文件写入Xilinx ZCU102 开发板中,在SDK 中编写并运行VGG16 网络的C 语言代码,以获得加速器的运行结果。

表1 FPGA 的资源利用情况Table 1 The utilization of FPGA resources

表2 所示为加速器运行VGG16 网络的结果。从表2 可以看出,在300 MHz 的工作频率下,加速器的峰值算力达到了153.6 GOP/s,完成单张图片的卷积计算仅需0.23 s。从算力、DSP 效率以及能耗比等方面来看,本文加速器实现了较高的计算性能。

表2 加速器性能指标结果Table 2 Accelerator performance index results

在运行VGG16 网络时,Xilinx ZCU102 自带的ARM Cortex-A53 处理器、Intel i7-8700 处理器以及本文加速器完成单张图片的卷积计算所花费时间以及加速比结果如表3 所示。从表3 可以看出,本文加速器的计算效率约为ARM 处理器的634 倍,约为Intel i7 处理器的40 倍。

表3 本文加速器与其他处理器的性能对比Table 3 Performance comparison between accelerator in this paper and other processors

5 结束语

本文将分块策略与循环计算顺序优化相结合,设计一种卷积加速结构,并与基于RISC-V 开源指令集的顺序双发射超标量处理器共同组成SoC 系统,将该系统部署在FPGA 平台上,能够取得较好的加速效果。本文处理器基于开源指令集,可根据具体的应用需求进行特定的优化,扩展指令功能,为“主处理器+卷积加速器”的软硬件协同设计模式提供新途径。下一步将对包含RISC-V 处理器和卷积加速器的协同设计进行流片,以在提高处理器主频的同时进一步提升加速器的整体性能。