基于低压器件的高效高功率密度串联谐振DC-DC 变换器

施鸿波,吴新科,郭 清

(浙江大学电气工程学院,杭州310027)

随着全球信息化的飞速发展,数据中心的规模 与耗电量与日俱增。 数据显示2016 年中国数据中心总耗电量为1 100 亿kW·h, 占全年总用电量的1.8%[1]。 全球数据中心耗电量占比为2%,到2020 年预计增长到5%[2]。而数据中心的供配电系统损耗占总能耗的10%左右[3-4]。 为提升数据中心的电能使用效率PUE(power usage effectiveness),业界提出了高压直流母线架构[5-7],相对于传统的交流供电架构,具有高效率、高可靠性、高扩展性、低成本、低谐波干扰等优势[8-9],是未来的发展趋势。

从高压直流母线电压(380 V)到负载点电压(12 V)需要一级隔离的降压DC/DC 变换器模块。未来的发展趋势是母线变换器及其负载都集成在主板上,从而实现集成化、模块化的产品[9-10]。 而目前380 V/12 V 的DC-DC 模块产品工作频率多在200 kHz,功率密度低于400 W/in3[11-12],不符合主板集成所要求的高功率密度需求。而串联谐振电路能实现全负载范围的原边开关管零电压开通ZVS on(zero-voltage switching on)与小电流关断,在MHz 下能实现较高的效率与功率密度,满足主板集成DCDC 模块的需求[10,13-14]。 在MHz 变换器中,新一代电力电子器件GaN HEMT 在高频变换器中相对于Si MOSFET 有较大的优势[10,13-14],但在商业化的电源模块中极少见GaN 器件的应用。

本文首先建立SRC 中原边开关管的损耗模型,在此基础上进行原边开关器件的选型;然后,针对低压器件进行拓扑的设计并提出原边高压输入侧串联的多相SRC 电路;最后,通过样机实验进行验证设计,所提变换器可以实现较高的效率与功率密度。

1 原边开关管导通损耗数学模型

典型的半桥串联谐振电路及关键工作波形如图1 所示。 图1(a)为典型的半桥串联谐振变换器的拓扑, 工作在谐振点时具有稳定的直流增益,故在高频下可以看作为直流变压器DCX(DC transformer)。 其原边由2 个开关管S1和S2构成半桥,Cotr为其寄生结电容,Lr、Cr分别为谐振电感与谐振电容;副边采用中心抽头结构与同步整流。

图1(b)为其工作的关键波形,在死区时间td内励磁电流iLm完成对原边开关管结电容的充放电,实现开关管的ZVS on。 当电路工作频率设定在谐振点时,关于谐振周期Tr、死区时间td和开关周期Ts的关系为

图1 半桥串联谐振电路及关键工作波形Fig. 1 Half-bridge series resonant circuit and its key working waveforms

原边开关管的导通损耗可以表示为

式中:Rdson为原边开关管的导通电阻;Iprms为原边电流有效值。

图中,原边电流ip=iLm+iLr,ip在电路谐振点工作时可以看做是一个正弦波,其表达式为

式中:Ip为正弦波幅值;ω=2π/Tr;θ 为iLp和ip的相位差。

忽略死区时间内的励磁电流,Iprms与Ip的关系为

由图1(b)可知,式(3)在t0时刻的初始值为ILm,即

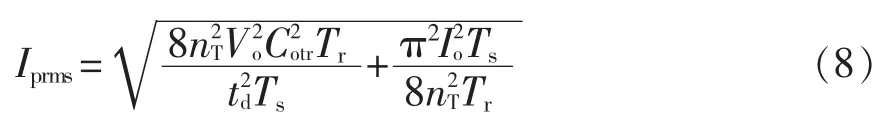

死区时间内电路模态与简化模型如图2 所示。图2(a)是在死区时间td内励磁电流iLm给原边结电容充放电的等效电路。 此时变压器原副边开关管(S1和S2、SR1和SR2)均关断,励磁电感Lm不再 被输出电压箝位,励磁电流可以看作一个恒流源给原边结电容充放电,其简化的电路模型如图2(b)所示。 为了在给定死区时间内实现软开通,励磁电流ILm的计算公式为

式中,V1为输入电压。

在变换器进入稳态后,变压器原边传递向副边的功率应当等于输出功率,即

式中:nT为变压器变比;Vo和Io分别为输出电压和输出电流。

由式(4)—式(7)可以得到Iprms的表达式为

将式(8)代入式(2),得到原边开关管导通损耗的表达式为

图2 死区时间内电路模态与简化模型Fig. 2 Circuit mode in dead time and the corresponding simplified model

2 电路器件选型与拓扑设计

在建立原边开关管的损耗模型后,根据模型可以进行原边器件的选型。 电路输入电压为380 V,考虑器件应力与一定裕量,考虑600 V 的Si MOSFET 作为原边器件。 在计算导通损耗时, 考虑MOSFET 结温为100 ℃下的导通电阻, 根据式(9)可以计算出,在380 V/12 V/150 A 规格下,600 V C7 MOSFET 系列[15]中导通损耗最小的器件为IPB60-R040C7,导通损耗为15.4 W,损耗占电路总功率比例约为0.9%,损耗较大。 若考虑以2 个250 V 器件串联代替高压器件作为原边器件时, 可选出250 V的Si MOSFET 系列中最小导通损耗的器件为IPB200N25N3G,导通损耗为10.0 W。 同理,计算不同数量的n 个低耐压器件串联代替高压器件的最小导通损耗,如图3 所示。

图3 导通损耗随器件串联数量与耐压的变化Fig. 3 Changes in PCon with the number of seriesconnected devices and withstand voltage

由图3 可得,随着器件耐压的降低,导通损耗逐渐减小,而所需器件串联的数量逐渐增大。 当器件耐压小于60 V 以后, 其导通损耗降低已经不明显。 考虑到导通损耗与器件数量的变化趋势,选择60 V 的器件作为原边开关器件, 此时器件串联数量为8,如图4 所示,所选器件型号为BSZ040N06 LS5。 然而器件的直接串联在实际工作中会遇到开关动作时器件间动态均压的问题,因此将器件的直接串联变成拓扑的串并联,如图5 所示,更具有可行性。

图4 低压器件直接串联Fig. 4 Series connection of low-voltage devices

图5 拓扑原边输入侧串联副边输出侧并联Fig. 5 Input-series output-parallel topology

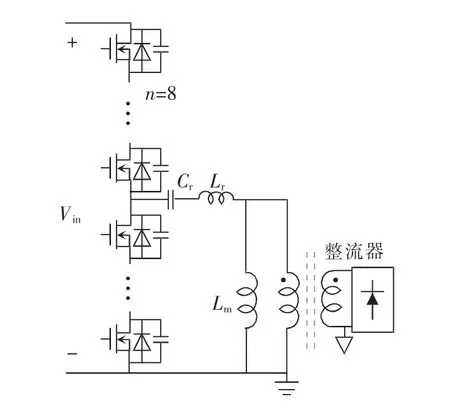

图5 所示的电路是由4 个具有相同电路结构的串联谐振电路单元在原边高压输入侧串联, 副边低压输出侧并联构成的ISOP 结构,实线框内为其中一个电路单元。由于电路原边为串联,则每个电路单元的输入电压为Vin/4。每个电路单元都有4 个60 V 器件构成的2 个半桥,通过矩阵变压器集成在一个UI型磁芯上。采用变压器漏感作为谐振电感,Cr为谐振电容,2 个半桥构成的SRC 子单元在原边串联,副边整流输出侧并联构成一个电路单元。

由于副边输出侧为低压大电流,因此采用中心抽头与同步整流技术减小副边大电流下的导通损耗。 在大电流输出下,须考虑同步整流器SR(synchronous rectification)由于温升导致的导通电阻增大。 此外开关管与PCB 之间的焊接点电阻通常为0.5~1.0 mΩ,与SR 的导通电阻在同一个数量级,因此焊点电阻不可忽略。首先建立副边整流电路的损耗模型,若选取的同步整流管在100 ℃下导通电阻为Rdson, 整流管的漏极与源极的焊点电阻等效为Rpad,则整体的等效导通电阻Rsr=Rdson+Rpad。 此时考虑多个SR 器件并联,则导通损耗为

式中:Is_rms为流过SR 的电流有效值;n 为并联的SR数量。

考虑SR 的驱动损耗,可得SR 的总损耗为

副边输出电压为12 V, 则整流管电压应力为24 V,考虑裕量选取30 V 与40 V 的器件,进行横向对比。 由于电路的4 个单元在拓扑上完全一致,处理的功率相等, 在计算时只考虑一个电路单元的整流电路。 计算时考虑整流管结温为100 ℃时的导通电阻,焊盘电阻取1 mΩ,驱动电压为5 V。 一些可选器件的总损耗随并联数目的变化如图6 所示。

图6 同步整流电路总损耗与SR 并联数目的关系Fig. 6 Relationship between the total loss of synchronous rectifier circuit and the parallel number of synchronous rectifiers

从图6 中可以发现,SR 总损耗先随着并联数目n 增大而快速下降,在SR 并联数较大时,总损耗反而增大。 n 较小时导通损耗占SR 损耗的主要部分,SR 的并联减小了总的导通损耗,因而总损耗随导通损耗下降而快速下降;当并联数增大后,驱动损耗占的比重增加,而导通损耗比重减小,因此随着并联数n 增大,总损耗反而上升。 从图6 中可以看到,在n>2 以后,总损耗几乎没有变化或快速增大,因此本文设计中取n=2。 此时可取副边整流SR型号为BSZ0501NSI。

3 实验验证

根据本文提出的损耗模型与设计思路,设计并实现了一台样机,其中一个电路单元的参数如表1所示,样机的正背两面如图7 所示。 变换器的工作频率为1 MHz,死区时间td为80 ns,原边器件为60 V的MOSFET。 电路一共由4 个串联谐振电路单元构成,每个单元具有相同的电路结构,由输入电容、原边开关管、谐振电容、变压器与副边整流电路构成。四相电路单元之间的高压输入侧为串联,其低压输出侧为并联。采用UI 磁芯构成的矩阵变压器,副边采用中心抽头结构与同步整流技术,减小大电流输出时的导通损耗。

表1 样机参数Tab. 1 Prototype parameters

图7 样机图的正背面Fig. 7 Top and bottom photos of the prototype

图8 是电路工作的关键波形, 图中,Vgs_S2为原边开关管S2的驱动信号,Vds_S2为对应开关管漏源极两端电压,ILr为谐振腔电流。由图8 可得,原边开关管在全负载范围内实现了零电压开通。在电路启动与负载跳变中各相电路之间的动态均压测试如图9 所示,各相输入电容上的电压在各种工况下都能维持均压。 由于变压器采用了平面变压器,使得各相之间的参数差异较小,在同频率工作时各相谐振参数基本一致,在电路启动、稳态与负载跳变等工况下均能维持各相间的均压与均流。

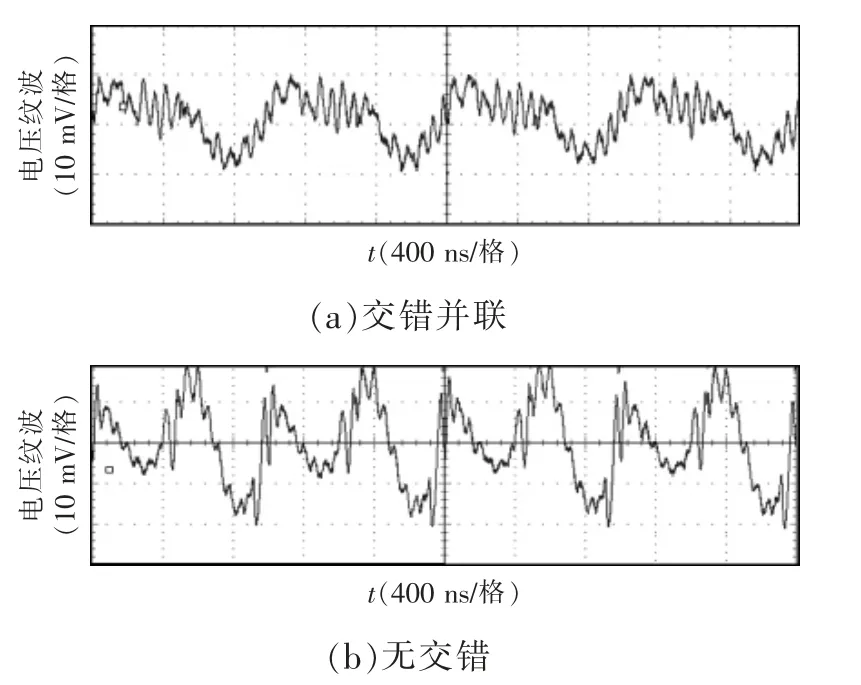

基于副边的并联输出结构,电路单元间采取交错并联控制策略时能有效减小输出电流的纹波与电压纹波,减少所需的输出滤波电容量。 为了实现各相输出电流之间相互的交错并联,则各相驱动时序应逐相差Ts/8。 比较四相交错并联时与不交错时的输出电容上的电压纹波,如图10 所示,同输出电流下交错并联时能有效减小输出纹波。

计算所得与实验测得的输出电压纹波随负载变化的趋势如图11 所示, 可见交错并联能有效减小输出电流的纹波与电压纹波。 图11 中的无交错并联实验中测得电压纹波大于计算得到的电压纹波,这是由于输出电容本身等效串联电阻与寄生电感影响了电容的滤波效果。 而在交错并联实验中,除了输出电容本身等效串联电阻与寄生电感外,各相输出之间的PCB 线路阻抗也会影响交错并联的效果,因此其实验测得的纹波也大于计算值。

图8 电路关键波形Fig. 8 Key waveforms of circuit

图9 各相启动与负载跳变时均压Fig. 9 Voltage sharing at startup and load transition

图10 60 A 输出时电压纹波对比Fig. 10 Comparison of voltage ripple at output of 60 A

图11 输出滤波电容上的电压纹波Fig. 11 Voltage ripple of output filter capacitor

样机所测的效率曲线如图12 所示(不包括驱动损耗),样机峰值效率在50 A 处,可达98.3%,满载效率为97%。 满载下功率密度可达810 W/in3。

图12 实验测得效率曲线Fig. 12 Efficiency curve measured in the experiment

4 结语

高效率与高功率密度的高频变换器越来越受业界关注, 而传统的高压Si 器件在高频DC-DC 变换器中效率表现较低频大幅下降,因此本文选择以低压Si MOSFET 作为高频变换器原边器件, 并结合拓扑设计了原边高压输入侧串联的ISOP 串联谐振变换器。设计了一台规格为380 V/12 V/150 A 的四相ISOP SRC DCX,并实现了98.3%的峰值效率、97.3%的轻载(10%载)与97%的满载效率,功率密度达810 W/in3, 均高于目前基于高压Si 器件的商业化模块。