基于CPCI总线的航天器通信信号设备故障检测系统设计

张贺鑫,雷文礼,王雨婷

(延安大学 物理与电子信息学院,陕西 延安 716000)

0 引言

航天器通常处于高温高压的恶劣环境中,当设备在飞行过程中发生故障时,会导致卫星的轮控姿态会发生偏差,甚至转速失控。因此,如何有效地探测航天器的失效状态,已成为当前研究的热点之一[1]。当前基于时域反射法设计的系统检测和分析导体绝缘故障,但本系统采用的测量信号为窄电压脉冲,易受原功率信号的影响,且仅适用于电缆故障离线检测;基于频域反射法设计的系统,通过被测电缆接收扫频信号,利用傅立叶变换,测量反射信号峰值频率,完成故障点的距离转换。该系统能够检测和定位航空器电缆故障,但因为算法复杂度较低,无法进行实时检测,只能离线运行;基于非线性时间序列定位算法设计的系统,可以实现故障特征提取,从而实现光纤网络故障的快速定位,已取得了一些研究成果,但是算法定位精度不高,实时性差。

针对上述问题,设计了基于CPCI总线的航天器通信信号设备故障检测系统。CPCI总线在操作系统、驱动程序和应用程序中,数据传输速度更快,具有高度开放性、高可靠性和热插拔能力。除了在通信和网络中有广泛地应用之外,它也可用于实时系统控制,工业自动化,实时数据采集,军事系统等方面,以 CPCI总线结构为基础的设备,已经广泛应用于航空航天领域的地面设备开发。

1 系统总体框架设计

基于CPCI总线的航天器通信信号设备故障检测系统总体框架主要采用标准CPCI箱体,中央处理机(CPU)采用普通板,其余功能模块采用已投入生产的CPCI板[2]。系统以CPU板为控制板,主要负责各种功能板的软件计算与硬件调度,系统总体框架如图1所示。

图1 系统总体框架图

连接被测板和子适配器,连接子适配器和主适配器。主适配器主要控制PXI中的卡资源,并连接通用的PC终端。系统总体框架主要控制PXI中各板产生的响应激励信号以及从测量板获得的响应信号[3]。通过主适配器以及子适配器,将激励信号添加到被测电路板上,并在电路板上添加标识信号,实现系统故障的定位和识别。

2 系统硬件结构设计

基于CPCI总线的航天器通信信号设备故障检测系统硬件主要采用CPCI故障模拟模块,通过RS232串行线控制注入机,利用故障注入器执行故障注入CPCI总线,使用时钟分配芯片传输时钟信号,通过CPCI检测板卡模块,配合FPGA实现接口控制。

2.1 CPCI故障模拟模块

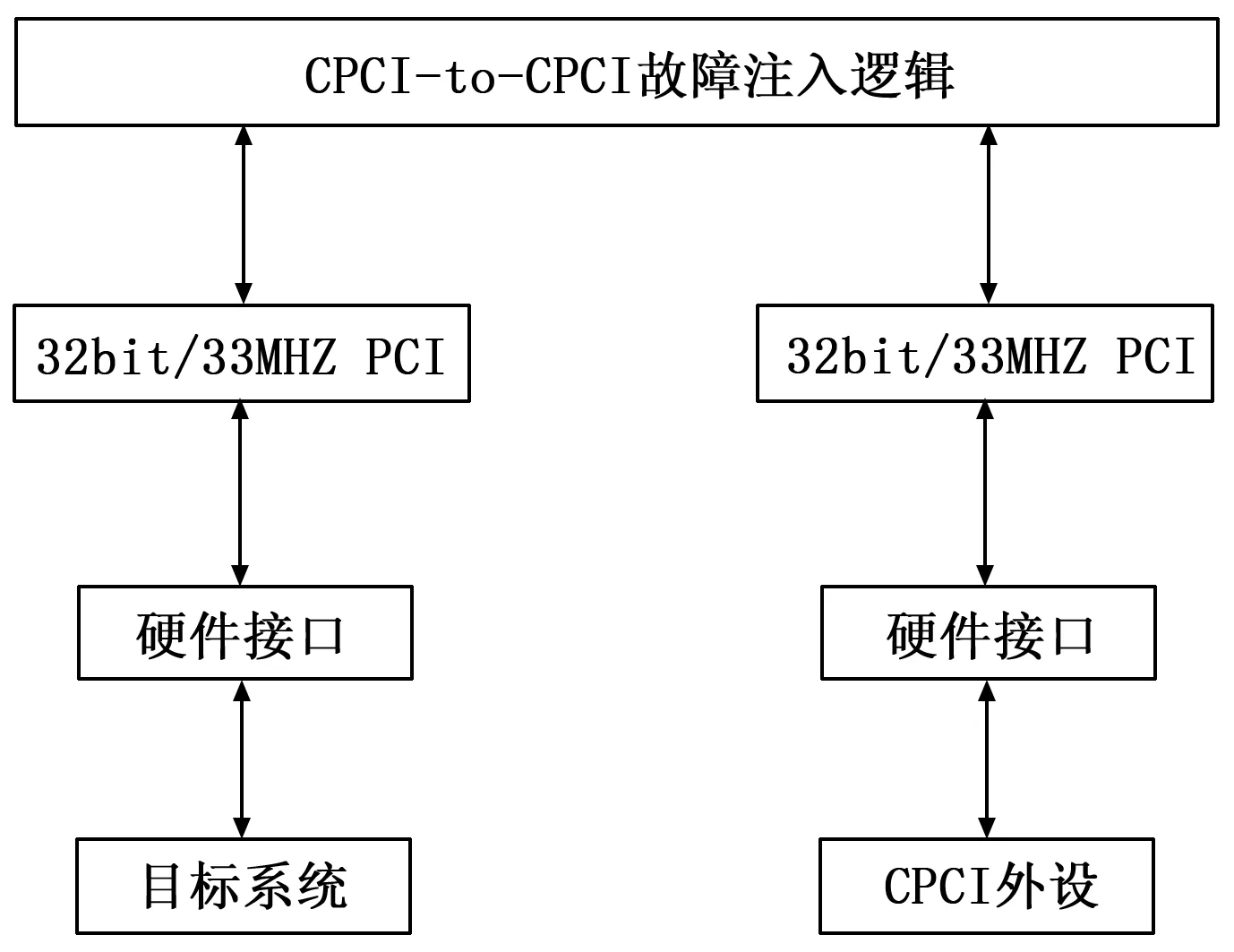

CPCI故障模拟模块通过RS232串行线对注入机的操作进行控制。注入器嵌入在目标设备与 CPCI底板之间,通过注入器可以对数据修改,从而实现故障注入[4]。CPCI故障模拟模块结构如图2所示。

图2 CPCI故障模拟模块结构图

故障注入器负责故障注入的执行,接收控制系统的参数和指令,根据用户设定的参数将故障注入 CPCI总线,并将注入结果和总线状态等相关信息反馈给控制软件,供进一步分析处理。FPGA逻辑是故障注入器硬件的重要组成部分,包括CPCI-to-CPCI桥IP核和故障注入逻辑[5]。桥接 IP核扩展了目标系统原有的 PCI总线;扩展总线通常被称为次总线,而扩展总线被称为主总线。CPCI-to-CPCI桥 IP核在主总线上只相当于一台 PCI设备,而在此总线上可以支持更多设备[6]。

2.2 故障注入器

因为CPCI故障注入程序包含一个CPCI-CPCI桥接逻辑,所以注入程序本身在总线主端作为CPCI设备运行。总线主侧注入器设计必须符合 CPCI设备设计规范;CPCI-CPCI桥接 IP核提供地址、数据、控制信号、独立时钟、中断机制和总线仲裁机制,用于总线上的其它设备。二次注入器的总线设计必须符合 CPCI底板,为保证注射头与靶板的正常工作,需根据有关规范进行硬件设计[7]。故障注入器结构主要包括 FPGA、CPCI插座、电源电路、通讯接口电路、时钟电路和配置电路[8]。在FPGA工作时,FPGA包含CPCI-to-CPCI桥接IP核和故障注入逻辑,但是FPGA基于 SRAM技术,断电后通常会丢失内部逻辑。当FPGA加电时,为了保存FPGA配置信息和自动配置FPGA,就需要一个独立的外部配置电路,这种组态电路通常使用 EEPROM作为组态芯片。

2.3 时钟电路模块

CPCI-to-CPCI桥接IP用于输入端P_CLK和S_CLK分别为主端和副端的两个同步时钟域,时钟信号需要同步,并且S_CLK的相位和频率不得超过P_CLK。连接后,主机侧时钟信号的长度应为63.5 mm(±2.54 mm),其他信号的长度应小于或等于63.5 mm。在第二端的每个扩展插槽都需要一个独立的时钟信号,该信号由CPCI到CPCI桥接器通过时钟分配芯片传输[9]。为减少时钟信号支路的反射效应,时钟分配芯片必须将时钟信号串入扩展槽中,再加上终端电阻。与此同时,为了保证时钟信号的同步,时钟分布芯片与 FPGA的S_CLK输入口必须具有相同长度的时钟跟踪每个扩展槽,每个扩展槽的长度为135~185 mm。二次侧喷嘴设计有三个扩张槽,但由于空间限制,只能实现其中一个扩张槽。时钟分配电路模块结构如图3所示。

图3 时钟分配电路模块结构图

2.4 CPCI检测板卡模块

使用CPCI接口芯片,配合 FPGA实现接口控制。FPGA+ CPCI接口芯片结构如图4所示。

图4 FPGA+ CPCI接口芯片结构图

因为CPCI总线是基于CPCI总线协议开发的,所以它承接了CPCI总线上的所有信号,并且在通信过程中维护CPCI总线的所有电气特性。CPCI接口芯片CPCI9054在 CPCI总线上完成 CPCI总线的部分功能,并可与各模块 I/O端口及存储器通信[10]。FPGA负责PCI9054与本机端口的通讯,实现CPCI本机定时控制。在CPCI总线上控制和管理触发信号、参考时钟和其它扩展信号,以及执行其它定时操作和控制。

3 系统软件部分设计

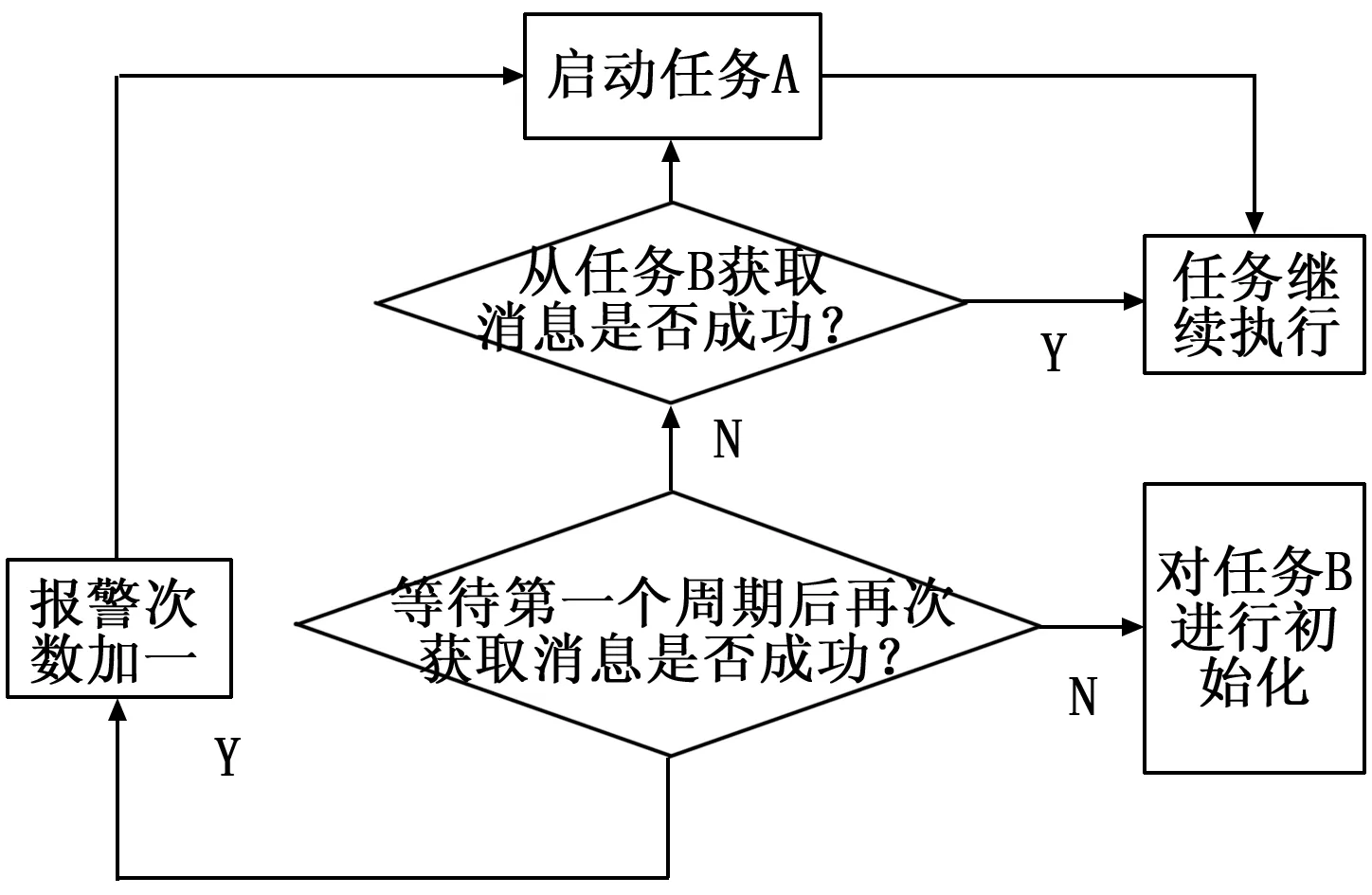

对于软件部分设计,当发现故障时,如果运行时间仍然不能满足系统运行要求,用户可根据可靠性来判断。若工作时间影响系统的工作要求,系统会自动复位并重新初始化设备。系统故障处理逻辑流程如图5所示。

图5 系统故障处理逻辑流程图

在任务开始运行时,两个任务之间的时间间隔被设定为固定位置。按照设计任务运行周期为32 ms,时钟准确度为微秒,因此,运行周期的时间误差在100 μs范围内。错误大于100 μs小于1 ms,报警次数增加;错误大于1 ms,软件重新进行初始化,完成对看门狗和任务的删除和重构。在任务级故障检测方面,利用任务间的相互依赖关系实现任务间的相互检测;在系统的整体运行中,许多任务相互依赖,需要使用消息来交换信息。所以当任务 A运行时,任务 B是否发送了任务 A需要的消息,任务级故障处理流程如图6所示。

图6 任务级故障处理流程图

任务 A启动后,首先从任务 B获取消息。如已成功获得任务 B的消息,则表明任务 B工作正常,程序运行正常。若某个获取失败,则程序继续运行,等待下一个获取,然后再次读取消息。若此时能成功取得讯息,警报会增加一次,继续正常运作。若仍未成功,则初始化任务 B,并确保它在运行前对所有相关变量进行初始化。终端网工作站定期向总线控制器和系统芯片发送多路通信网的相关信息,主要通过CPCI总线控制芯片和传输通信信号分析处理系统芯片,并向终端网节点返回无疵点检测结果。

在正常工作时间内,如果终端系统接收不到上位机的确认帧反馈,则可以确定故障区域。在多个通信网络中检测故障信号的关键是准确识别故障信号中包含的异常信息。该系统的软件算法部分在信息提取和噪声过滤链路中,使用二次相关算法,可在信噪比较低的情况下使用该算法。该方法可以准确估计多个网络的延迟,并提取故障信号中包含的异常信息。分别以和对信号采集模块采集的收发信号,设计了以下信号模型:

(1)

式(1)中,s(t)表示原始航天器通信信号;i表示信号采集次数;τi表示通信信号系数;n(t)表示故障检测系统受到的噪声影响函数。发射信号与接收信号两者之间关系如下所示:

Rxy(U)=E[x(t)y(t+U)]

(2)

充分考虑故障检测系统受到的噪声影响因素,将发射信号与接收信号两者之间关系改写为:

(3)

识别多通道通信网中所述发送信号和所述接收信号之间的关系,二次相关算法可以在低信噪比的情况下,提高网络时延估计的准确性,并且能够准确地提取多通道通信故障信号中包含的详细信息,以定位和识别故障节点或连接,及时处理多通道网络通讯故障,实现基于CPCI总线的航天器通信信号设备故障检测系统设计。

4 系统调试

针对基于CPCI总线架构的航天器通信信号设备故障检测系统设计合理性,进行系统调试分析。

4.1 CPCI串口卡故障注入实验环境

CPCI服务器通常用于工业控制领域的数据采集和生产设备状态监测。带有 CPCI接口的串口卡是一种比较常用的外设,在 CPCI试验中,选择研华micc-3392作为 CPCI试验机,用普通 PC作为控制机,进行 CPCI故障注入试验。执行故障注入控制软件,通过RS232串行线连接故障注入器。CPCI串口卡故障注入实验环境如表1所示。

表1 CPCI串口卡故障注入实验环境

通过 CPCI串行卡故障注入实验,MIC-3621串行卡插入喷射器,MIC-3392试验机外围插槽插入喷射器。RS232串口与MIC-3621串口卡通过串口直接相连,串口调试助手软件分别运行于测试机和控制机上。

4.2 实验结果与分析

采集航天器通信信号,分别分析正常情况下和故障情况下信号曲线变化幅度,如图7所示。

图7 正常情况下和故障情况下信号曲线变化幅度

由图7可知,正常情况下信号曲线变化幅度具有一定规律性,在3.5 s采集时间内,信号最大为28 dB,最小为3.8 dB;而在故障情况下信号曲线变化幅度不具有规律性,在3.5 s采集时间内,信号最大为28 dB,最小为1 dB。

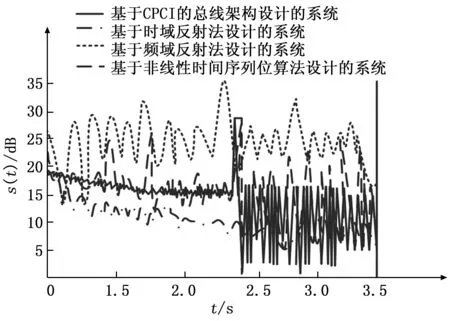

基于此,分别基于时域反射法设计的系统、基于频域反射法设计的系统、基于非线性时间序列定位算法设计的系统和基于CPCI的总线架构设计的系统对这两种情况下的信号曲线变化幅度展开分析,结果如图8、9所示。

图8 不同系统正常情况下信号曲线变化幅度

图9 不同系统故障情况下信号曲线变化幅度

由图8可知,基于时域反射法设计的系统与实际信号采集周期不一致,但变化幅度一致,信号最大为26 dB,最小为9 dB;基于频域反射法设计的系统与实际信号采集周期一致,信号最大为27 dB,最小为7 dB;基于非线性时间序列定位算法设计的系统与实际信号采集周期一致,信号最大为24 dB,最小为12 dB;使用基于CPCI总线架构设计的系统与实际变化幅度一致,信号最大为28 dB,最小为3.8 dB。

由图9可知,基于时域反射法设计的系统整体变化幅度呈下降趋势,整体变化幅度不大,但整体与实际情况相差较大,信号最大为23 dB,最小为8 dB;基于频域反射法设计的系统变化幅度上下波动形式较大,信号最大为35 dB,最小为13 dB;基于非线性时间序列定位算法设计的系统比上述这两种系统更贴近实际曲线变化幅度,但也与实际情况存在一定偏差,信号最大为28 dB,最小为9 dB;使用基于CPCI总线架构设计的系统与实际变化幅度一致,信号最大为28 dB,最小为1 dB。

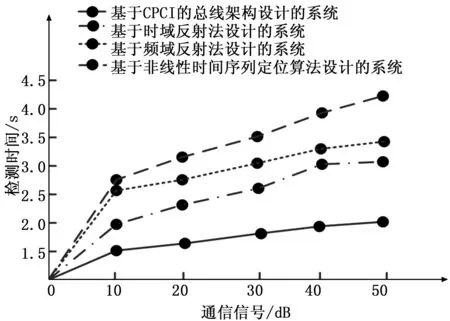

不同系统的通信设备故障信号检测时间如图10所示。

图10 不同系统通信设备故障信号检测时间

由图10可知,基于时域反射法设计的系统的通信设备故障信号平均检测时间为2.7 s,基于频域反射法设计的系统的通信设备故障信号平均检测时间为3.1 s,基于非线性时间序列定位算法设计的系统的通信设备故障信号平均检测时间为3.5 s,而基于CPCI的总线架构设计的系统的通信设备故障信号平均检测时间仅为1.8 s,由此可知,基于CPCI总线架构设计的系统的通信设备故障信号检测时间较短,

通过上述内容可知,使用基于CPCI总线架构设计的系统能够精准检测到通信设备故障信号,有效缩短通信设备故障信号检测时间。

5 结束语

为提高当前航天器通信信号设备故障检测系统通信设备故障信号检测精准度,降低故障检测时间,设计基于CPCI总线的航天器通信信号设备故障检测系统。通过CPCI故障模拟模块控制注入机,采用故障注入器执行故障注入CPCI总线,使用时钟分配芯片传输时钟信号,运用CPCI检测板卡模块,配合FPGA实现接口控制,完成系统硬件结构设计,通过终端网工作站发送多路通信网相关信息,返回无疵点检测结果,采用二次相关算法,提取多通道通信故障信号详细信息,实现系统软件部分设计。实验研究表明,基于CPCI总线的航天器通信信号设备故障检测系统通信设备故障信号检测精准度较高,能够有效缩短通信设备故障信号检测时间。