基于ZYNQ的高清图像显示及检测系统设计

林振钰,张志杰,刘佳琪

(中北大学 仪器科学与动态测试教育部重点实验室,太原 030051)

0 引言

图像包含大量的信息,对于人类而言视觉信息利用率最高,人类对数字图像显示的效果的判断会受到各种外部环境和主观意识等因素的影响。随着信息技术的飞速发展,在工农业生产中通过加入图像系统提取有用信息进行处理[1],从而输出检测结果或者控制信号,来提高系统的智能化和自动化。在某些特定场景下,如交通运输、精密测控、显微医学操作、工业探伤以及农田作业等领域[2],对图像有实时性和高精度检测要求,而在图像显示及处理的过程中要占用大量资源和时间,例如,尺寸为1 920×1 080的8/24 bit 的BMP图像大小为 5.93 MB[3],连续的图像数据频带较宽,数据量大,像素相关性大。传统的DSP或ARM处理器取样速率较低,且系统使用浮点,很难对其进行直接的处理,且成本较高。FPGA适用于高速采样频率且任务比较固定或重复的情况,系统使用定点,可灵活试制样机。本文基于Xilinx公司ARM + FPGA 体系结构的Zynq高性能芯片,在AXI协议框架下设计了自定义数据存储传输的IP核,实现了处理速度与带宽最大化。利用HLS工具将图像预处理算法快速打包生成IP核[4],为各种中端图像处理算法提供了可扩展的 FPGA 硬件加速通道,利用软硬协同设计的方法完成了HDMI接口的高清图像显示系统平台的原型机设计。有效解决了低延时低功耗与高数据带宽和处理速度之间的矛盾[5],为后端结果处理与应用提供了良好支持。

1 系统硬件电路框架

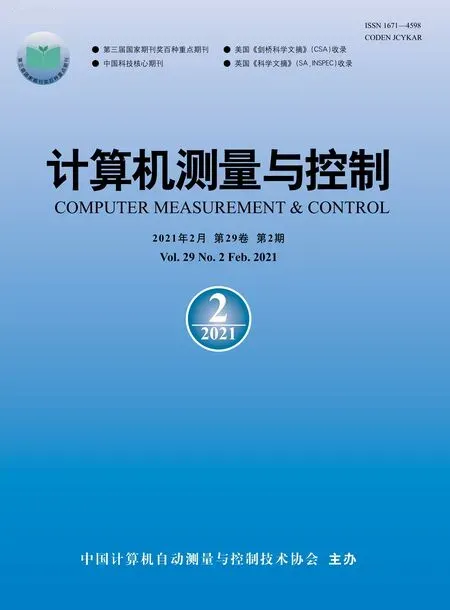

基于ZYNQ的实时视频高速采集处理系统原理如图1所示,系统平台主要由图像采集模块、数据存储模块、硬件加速模块、内部传输互联模块、HDMI高清显示模块组成。Zynq-7000SoC可扩展平台作为整个实时处理系统的核心,上方矩形为FPGA可编程逻辑(PL,programmable logic)部分,下方矩形为ARM处理系统(PS,processing system)。其中PS部分的高性能DDR3存储单元通过AXI内部互联与PL端进行大吞吐量的高速数据通信,其片内带宽足够大,消除了芯片间互联存在的带宽瓶颈问题[6]。

图1 系统结构原理框图

根据系统读取外界视频数据信息的数据流向,从软硬件功能层面具体划分为:

1)采集部分:视频通过位于PL侧的500万像素的cmos摄像头进行采集,PS侧引出EMIO引脚通过软件模拟SCCB协议对cmos摄像头进行配置。将采集到的图像数据送入PL中使用Verilog HDL编程封装的图像采集模块将数据位宽整合成24位。

2)硬件加速部分:将RGB数据格式传送到图像预处理模块,实现对RGB像素信息的各种预处理,如灰度化、滤波、边缘化等,此模块利用Xilinx的HLS工具,通过C语言编程实现各种图像预处理IP核的快速定制。在PL端实现硬件加速功能,提高图像处理的实时性。

3)存储传输模块:自定义AXI_DMA_WR写模块将数据通过HP口与PS端的DDR进行高数数据交互,将处理后的视频数据传输至DDR3内存芯片中存储,最后由PS端发出读信号控制AXI_DMA_RD读模块将DDR3中的图像数据读出并缓存到PL端的FIFO模块。

4)高清显示模块: 实现HDMI接口驱动逻辑,完成图像显示功能。根据差分信号高速数据传输技术TMDS(transition minimized differential signaling),编码驱动图像输出到 HDMI 接口,实现较传统VGA接口更为高清的图像实时显示功能。

2 系统关键部分实现

2.1 视频采集模块

视频采集模块选用OmniVision公司OV5640摄像头作为数据采集前端,它是一款1/4英寸单芯片图像传感器,其感光阵列2 592*1 944(即500 W像素),能实现最快15 fps QSXVGA(2 592*1 944)或者90 fps VGA(640*480)分辨率的图像采集。具有高灵敏度、低串扰和低噪声的优质性能。传感器内部集成了图像处理的功能,包括自动曝光控制(AEC)、自动白平衡(AWB)等。同时该传感器支持LED补光、MIPI(移动产业处理器接口)输出接口和DVP(数字视频并行)输出接口选择、ISP(图像信号处理)以及AFC(自动聚焦控制)等功能[7]。本系统中选择 DVP 接口模式[8],在PS端通过 SCCB协议将传感器视频分辨率配置为1 920×1 080,视频帧率配置为30 f/s。时钟频率为74.25 MHz(2 200×1 125×30)。

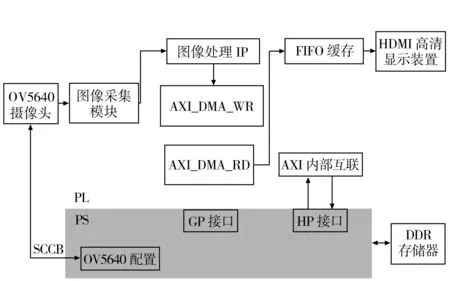

为了匹配适应显示模块HDMI接口输入端RGB888格式,在PL端使用Verilog HDL描述图像采集模块实现将8位原始图像数据转换为24位RGB数据的功能。摄像头采集模块在像素时钟的驱动下将传感器输出的场同步信号、行同步信号以及8位数据转换成读写控制模块的写使能信号和24位写数据信号,完成对CMOS传感器图像的采集。对图像采集模块进行测试仿真效果如图2所示,在帧同步信号激励下RGB颜色分量各占8位位宽输出。

图2 图像采集模块测试仿真图

2.2 数据读写模块

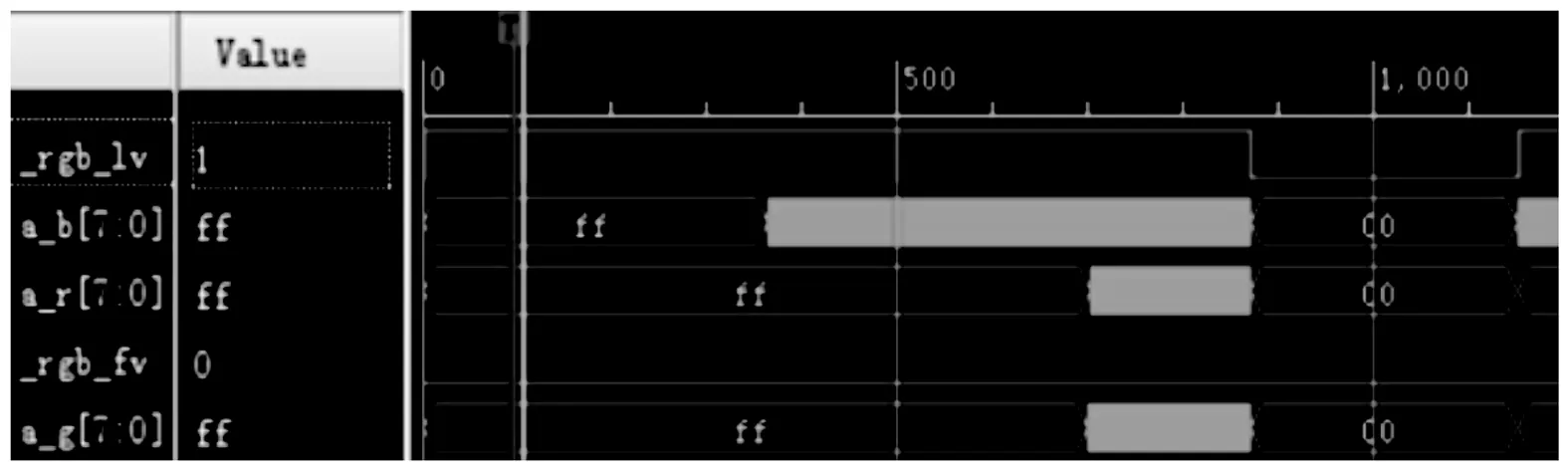

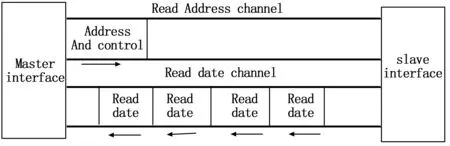

数据读写模块即FPGA与ARM的数据交换,不同工艺特征的处理器与FPGA融合在一个芯片上之后,片内处理器与FPGA之间的互联通路就成了ZYNQ芯片设计的重中之重。如果Cotex-A9与FPGA之间的数据交互成为瓶颈[9],那么处理器与FPGA结合的性能优势就不能发挥出来。在ZYNQ-7000AOSOC器件中, PS和PL之间的主要连接是通过一组AXI(Advanced extensible Interface)接口, AXI协议是基于猝发式传输机制的一种高性能、高带宽、低延迟的片内总线,总线由5个独立的通道构成:1)读地址;2)读数据;3)写地址;4)写数据;5)写响应。5个通道都有各自的源端产生的VALID信号和目的端产生的READY信号组成的握手机制,如图3所示。

图3 AXI协议的握手信号对

在地址通道上,每个交易有地址和控制信息,这些信息描述了需要传输的数据性质。在主从设备之间传输数据,分别使用从设备的写数据通道和到主设备的读数据通道。在主设备到从设备的写数据交易中,AXI有一个额外的写响应通道。从设备通过响应通道向主设备发出信号表示写交易完成。

2.2.1 AXI_DMA_RD读模块

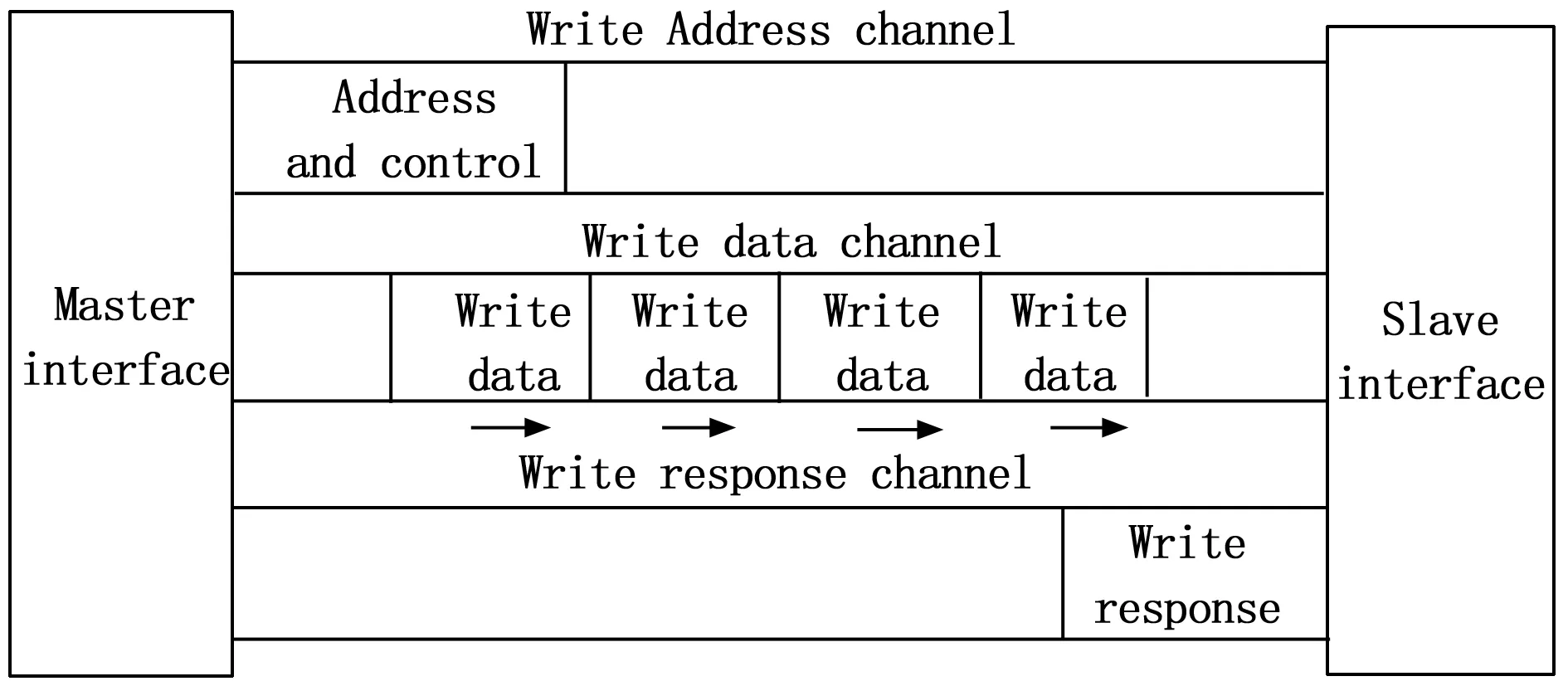

由于实时连续图像数据量大,本设计利用片内提供的的HP口即AXI的高性能端口(high performance ports)进行数据交互,对DDR3进行直接存储映射访问,其可设FIFO缓冲来提供“批量”读写操作,数据宽度是32或64位,适用于大块数据的高性能传输,带宽高。吞吐量最高,由于4个HP接口中PL都是做主机的,故创建一个master接口的AXI_DMA_RD读模块。主机首先在读地址通道给出读地址和控制信号,然后从机由读数据通道返回读出的数据,如图4所示。突发读操作主机只给出一个地址,从该地址连续突发读出数据。

图4 突发读操作过程

通过编辑IP保留模块接口信息,将AXI_DMA_RD读模块突发长度M_AXI_LAST改为256,数据位宽设为64,从而提高AXI访问DDR3的效率,将带宽做到最大,通过AXI总线把DDR3的数据读出来进入FIFO缓存。

图5 AXI_DMA_RD读模块时序图

具体设计时序如图5所示,在PS端控制读数据初始化脉冲TXN后,进入读数据阶段,使read_cycle_fl-ag拉高并一直保持。Read_cmd_flag开始发送读地址给从机,从机反馈数据read_data_flag,数据接收完毕后产生一个flase结束信号。256个数据读完之后读结束rea-d_data_flag拉低,地址清零,每个像素点占4个字节,则有结束地址READ_END_ADDR为8 294 400(1 920*1 080*4)。在read_cycle_flag一直保持高电平状态下循化再读。内部生成位宽为64,深度为4 096的异步FIFO。为了保证FIFO内部一直有数据,在FIFO缓存接口添加count计数器,当FIFO数据小于2 047就开始从DD-R读数据。由于突发长度为256,故将地址递增参数b-urst_size_bytes设为2 048(256*8)。最后通过添加例化RGB时序模块,将读模块封装成以RGB时序输出的模块,显示模块给内部FIFO读使能,当FIFO内数据量大于2 047时候读使能信号拉高,将读出数据缓存到F-IFO送给显示器。

2.2.2 AXI_DMA_WD写模块

同理,在编辑AXI_DMA_WD写模块时例化一个位宽32,深8 192的FIFO。图像采集模块帧同步信号作为内部FIFO写使能,读端口则设置为64位位宽,当FIFO读counter大于2 047时把W_axi_flag拉高开始写数据。

图6 写传输过程

写传输过程如图6所示,它用到了写地址、写数据和写响应3个通道。主机在写地址通道给出写地址和控制信号,然后在写数据通道连续突发写4个数据。从机在接收数据之后,在写响应通道给出响应信号。

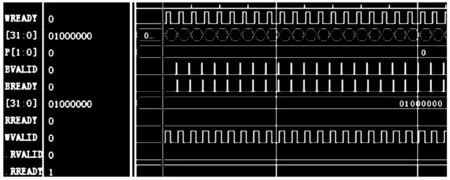

2.2.3 读写传输测试

在VIVADO工具中创建一个BD文件,添加ZYN-Q7处理系统IP,通过配置ZYNQ7处理系统IP进行读写传输功能测试,引出一个GPIO接口作为AXI_DMA_RD读模块的启动信号,在PS端设定一个TXN启动脉冲信号,内存基地址即访问DDR3的起始地址设为0X01000_000。PS端通过C代码模拟生成从1开始累加的测试数据写入DDR3并读出,PL端添加逻辑分析仪监测IP 检测,从而实现通过软件触发硬件运行,抓取片内实时信号的自回环测试功能,如图7所示。

图7 逻辑分析仪抓取的实时信号

在SDK工具中添加Memory监视器,可实时查看DDR内存测试数据动态,如图8所示。结果表明,该模块可实现预期功能。

图8 DDR3中的实时数据

2.3 高清显示模块

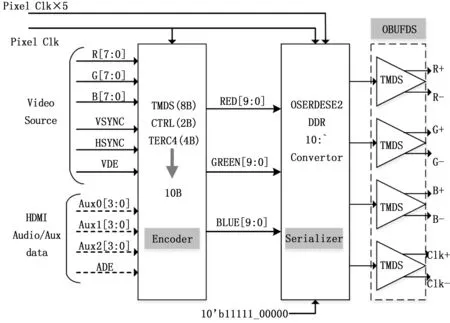

显示终端采用带有HDMI接口的设备,HDMI既高清晰度多媒体接口(high definition multimedia inter-face),是新一代的一种数字音视频接口,较传统的V-GA接口有数据传输带宽高、色彩度高及传输速度快等显著优点。本设计仅使用 HDMI 接口显示图像,不传输音频,因此只实现 DVI 接口驱动逻辑完成图像显示功能。DVI 和 HDMI 接口协议在物理层都使用 TM-DS 标准传输音视频数据。TMDS(transition minimized differential signaling)是一项使用差分信号高速数据传输技术[10]。

由于每个像素点的颜色深度为24位,即RGB每个颜色分量各占8位,通过添加一个 RGB2DVI 模块,将 RGB888 格式的视频图像转换成TMDS 数据输出。每个通道上的颜色数据通过一个8B/10B的Encoder编码器来转换成一个10位的像素字符。10位的字符通过Serializer并串转换器转换成串行数据,最后经过信号输出时的OBUFDS差分信号缓冲器由TMDS数据通道发送出去[11],OBUFDS模块在 FPGA 内通过添加例化原语实现,将内部逻辑信号转换成差分信号输出。上述过程的具体实现流程如图9所示。

图9 RGB2DVI 模块框图

需要注意的是,10∶1的并转串过程所生成的串行数据速率是实际像素时钟速率的10倍,实现的是10∶1的转换率。整个系统需要两个输入时钟,一个是视频的像素时钟 Pixel Clk(74.25 MHz),另外一个时钟 Pixel Clk x5(371.25 MHz)的频率是像素时钟的5倍。在此频率基础上实现双边沿采样,即在5倍时钟频率的基础上又实现了双倍数据速率。

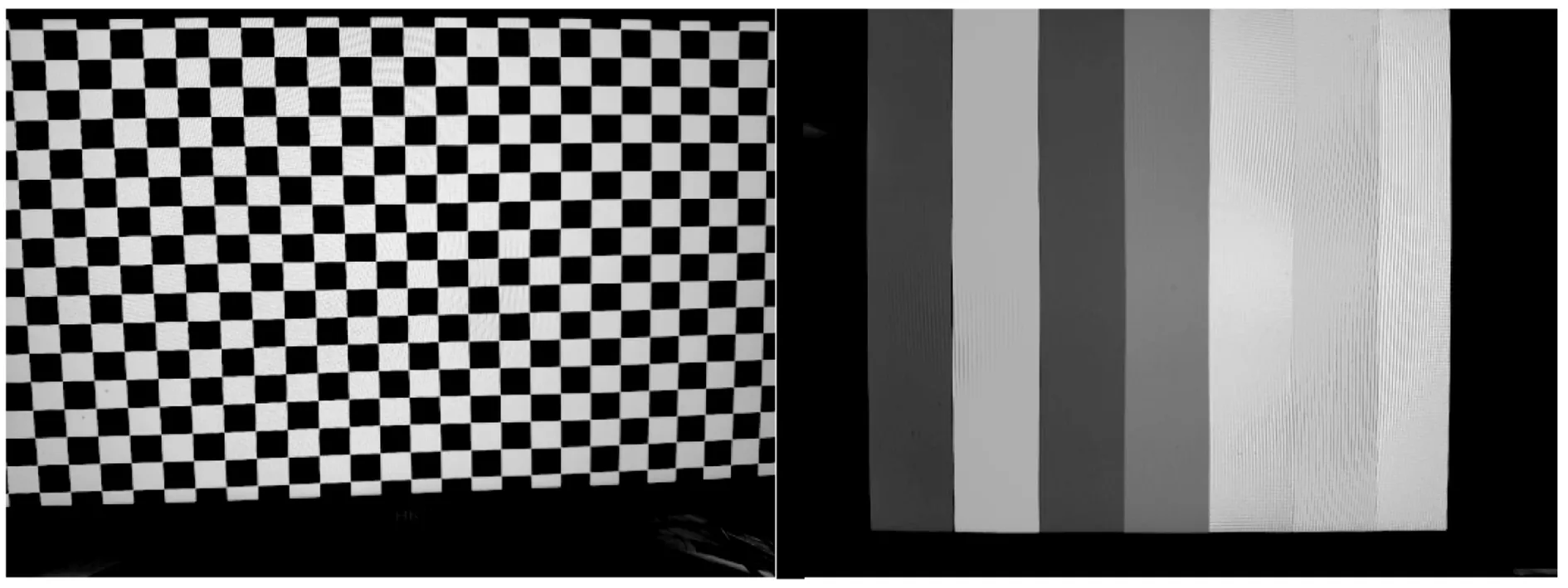

在支持HDMI接口的1 080 p分辨率的显示器上对高清显示模块进行测试,测试结果如图10所示。测试过程中,系统内部产生三基色、棋盘格图像数据源,结果表明,显示效果符合系统要求。

图10 高清显示模块测试效果图

2.4 图像特征提取IP核的实现

对图像预处理的算法常见的有中指滤波,均值滤波,高斯滤波,直方图均衡化等[12]。在工业生产中,图像的特征信息显得尤为重要。工业电子显微镜单一的图像显示对焦,不能实时迅速地对其进行处理与特征提取。通过某种方式对图像中的每一个像素点进行遍历,判断每个像素点是一个图像特征,从而减少冗余信息,可直观地评估图像为后续提供有效信息。

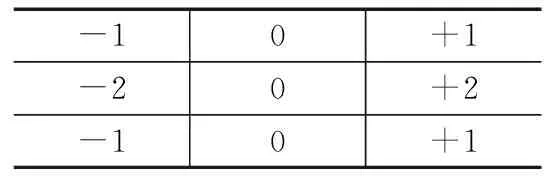

边缘检测即可标识数字图像中亮度变化明显的点,大幅度地减少数据量,剔除不相关的信息,保留图像重要的结构属性。在边缘检测算法中,Sobel边缘检测算子采用2个方向的3*3模板检测水平和垂直方向的边缘,如表1、2所示,其计算简单、速度快,满足实时性的要求。

表1 滤波模板

表2 滤波模板

将上述3*3滤波模板与图像作平面卷积,即可分别求得横向和纵向的亮度差分近似值。以A代表原始图像,GX和GY分别代表经横向和纵向边缘检测的图像灰度值[13],其卷积因子计算公式如下:

(1)

以f(x,y)表示图像(x,y)点的灰度值,则有:

(2)

(3)

图像的每一个像素点的横向和纵向灰度值均通过以下公式来计算:

(4)

通过将数值与提前设定好的合理阈值比较来判定该点是否为边缘信息点。

Xilinx推出的高层次综合工具HLS中包含大量的视频库函数,大部分图像处理模块函数和OpenCV库函数一致。本文利用视频处理库中的sobel函数,通过C++代码综合、仿真生成RTL电路,将其快速封装生成IP核,在PL端对图像处理算法进行硬件并行处理加速。

其具体开发流程中的关键语句如图11所示。首先,将视频流格式数据转换成mat类型,mat类型的RGB888格式的彩色图像再转换成单通道的灰度图像,用灰度数据与Sobel算子卷积;其次,将灰度数据转换成3个通道的灰度图像;最后,将mat类型的图像数据转换成视频流格式输出,完成处理功能。经仿真、综合完成后,将其打包生成IP核在PL中调用。在视频处理功能和数据结构方面,被综合后的代码与OpenCV基本对应,该方法极具灵活性、可扩展性,加快了图形处理模块设计的开发时间。显著提高了设计效率。

图11 基于HLS实现Sobel算子的设计流程

3 实验结果与分析

用Vivado工具的IP集成器将上述生成的IP核添加到系统Block Design中,对本设计进行最后的综合、实现、并生成比特流文件。导出最新的硬件平台即BSP板级支持包后启动SDK开发平台进行设计,利用C语言编程依次配置GPIO输入输出端口信息,设定系统初始化脉冲TXN。并通过SCCB协议配置摄像头参数信息。在SDK中对其进行单步调试,直到程序进入while主循环,周而复始地对DDR中起始地址0×1000000开始不断进行读写操作,处理连续的完整图像数据。

功能测试:采用两种不同场景对系统平台进行功能测试。

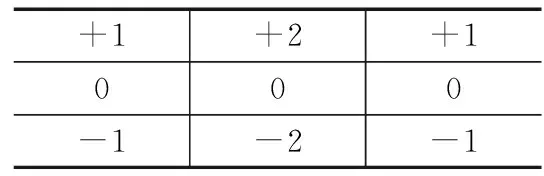

1)关闭图像处理通道,显示原始高清图像,采用一支偶丝直径为0.25 mm的高温热电偶对系统平台的高清显示功能进行测试,测试结果如图12所示。结果表明,该系统可直接对焦热电偶结点,清晰地显示肉眼不方便观察的偶结状态,对热电偶头部的损坏程度做出评估。

图12 原始图像高清显示的测试结果

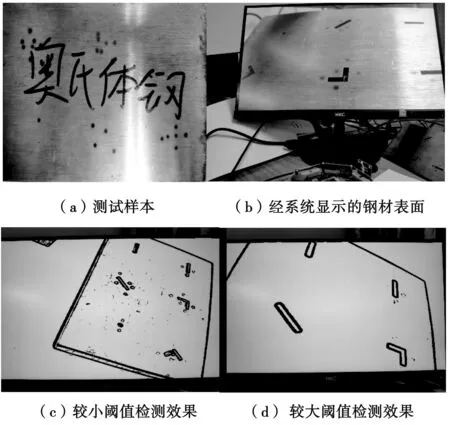

2)开启图像预处理硬件加速通道,采用带有激光烧蚀痕迹和受电火花侵蚀而形成槽形缺陷的特殊板材奥氏体钢对系统平台的图像实时处理功能进行测试。结果表明,通过调整检测阈值,可有效辨别出激光烧蚀痕迹与板材裂缝,如图13(c)中的小圆点为激光烧蚀痕迹,图13(d)为调整阈值后板材裂缝缺陷的检测效果,该结果可为板材的完好性评估提供有效参考价值。

图13 图像处理功能测试结果

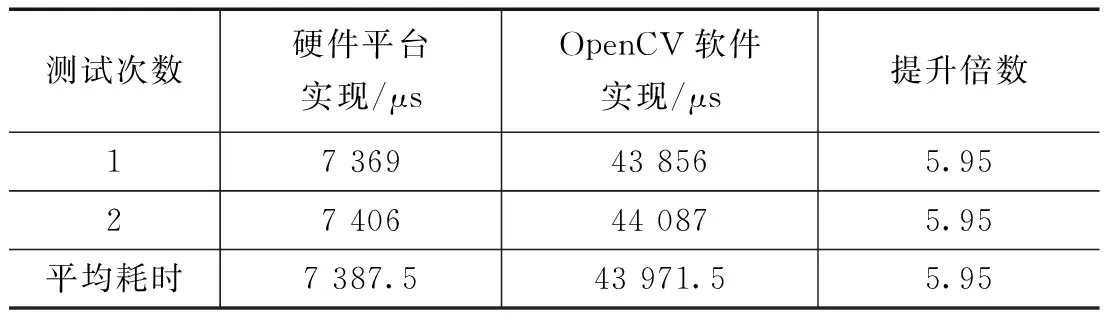

性能测试:在两种不同的平台上对系统平台的性能进行对比测试,即将在ARM处理器上通过软件的方式直接调用由 OpenCV自带函数处理的结果和在本系统硬件平台上进行处理的结果进行速度比对。其性能比对效果如表3所示。

表3 软硬件边缘检测耗时比较

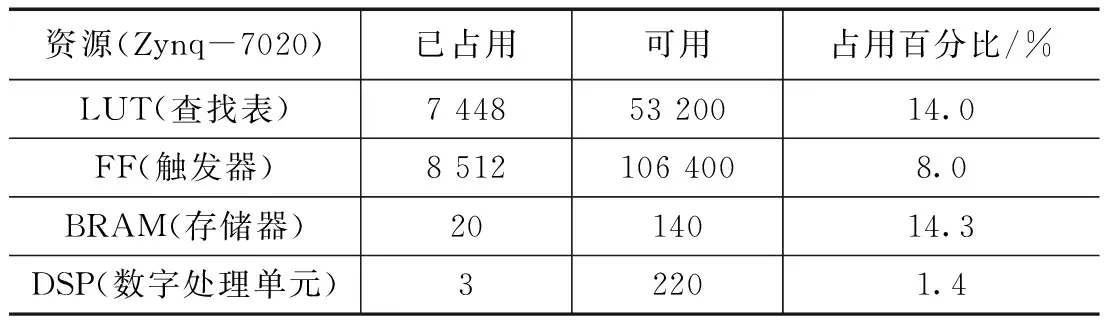

对系统占用资源进行汇总,片内资源使用情况如表4所示。

表4 片内资源使用情况

通过资源占用比和检测耗时比对结果可以看出, 软硬件协同处理与纯软件处理相比,速度提高了6倍左右,且片内资源使用合理,留有丰富剩余资源为后续开发提供支撑。可见本文提出的系统硬件平台实时视频图像处理的实时性和实用性较好。

4 结束语

针对传统处理器平台对图像数据采集与处理存在高时延与低吞吐量的问题,设计完成了集图像高速采集、特征提取硬件加速、图像实时高清显示为一体系统平台。系统充分结合FPGA与ARM的优势,减小了体积和功耗、降低了设计风险。通过自定义IP核有效提升数据带宽,并采用典型的图像处理算法验证了其高效可行性。硬件加速部分可以显著降低图像数据的处理耗时,使图像处理原型验证更具灵活性。系统平台资源利用合理,易于扩展,可为边缘终端数据处理加速和更复杂的图像处理应用系统提供可灵活配置的基础平台。系统可应用于工业监控探伤系统、民用多媒体系统以及医学等领域。