声音时延测量的数字电路实现与应用

刘永存,贺慧勇

(1.近地空间电磁环境监测与建模湖南省普通高校重点实验室,湖南长沙 410114;2.长沙理工大学物理与电子科学学院振动与噪声实验室,湖南长沙 410114;3.长沙理工大学物理与电子科学学院,湖南长沙 410114)

0 引言

声音时间延迟是指同一声源信号到达2个不同位置的时间差[1],其在机电设备故障声源定位[2]、流体流量测量[3]、流体泄漏检测[4]等工业领域有着广泛的应用。在基于麦克风阵列的声源定位系统中,传统的声源定位算法有3种:基于到达时间差(time difference of arrival,TDOA)算法、基于高分辨率的谱估计算法和基于最大输出功率的可控波束形成算法[5]。其中基于到达时间差的声源定位算法首先求出声音到达不同位置麦克风的时间延迟,再根据时间延迟求得声音到达不同位置麦克风的距离差,最后利用几何知识可以确定声源位置信息[6-7]。针对不同的测量条件与要求,常用的声音时延测量的方法有相关法、相位法、双谱法、自适应滤波器参数模型法等[8]。相关法是利用互相关函数在该时延值处取得最大值的特性,由互相关函数的峰值位置测量出该时延值的大小[9]。

在使用传统模拟麦克风作为声音传感器采集声音信号时,外围电路复杂,难于调试,稳定性和可靠性都较差。使用微控制器或数字信号处理器作为信号处理单元时,受其串行工作方式束缚,不能同时处理多个任务、速度慢。为了满足工业现场对时延测量系统稳定性与实时性的要求,本文提出一种应用于声源定位系统中的互相关法时延测量数字电路硬件级实现方案,该方案全部采用数字器件,便于系统调试,减少了模拟元器件参数离散性对电路指标的影响,提高了测量电路的稳定性与可靠性。在现场可编程门阵列(field programmable gate array,FPGA)中硬件实现互相关算法,减少了软件方案运行速度慢、难于采集和处理多路声音信号等问题。

1 互相关法声音时延测量原理

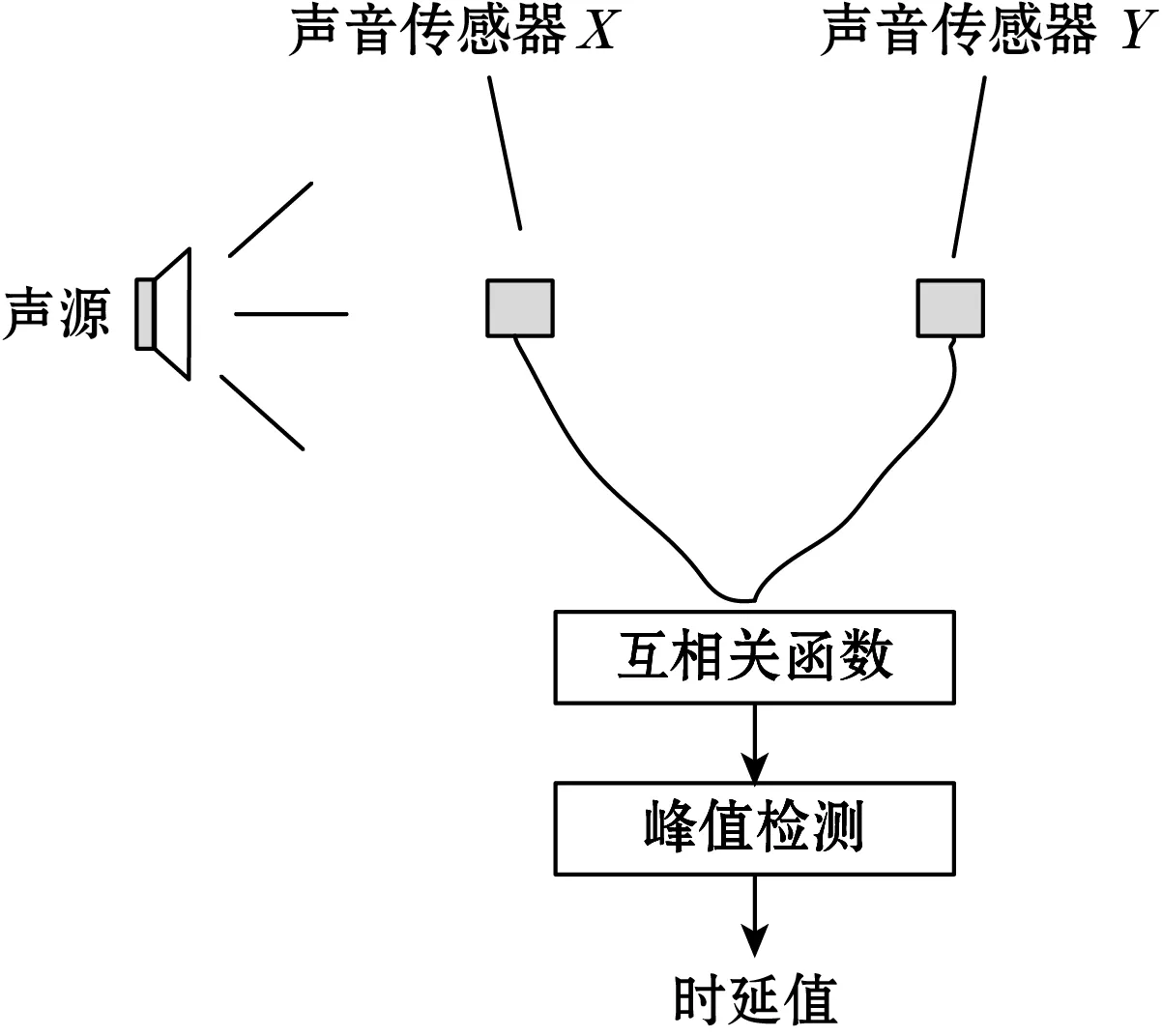

互相关法测量两路声音信号时间延迟的示意图如图1所示。

图1 互相关法测量声音时间延迟示意图

声源发出声音信号,到达两声音传感器的两路声音信号分别为x(t)和y(t),则表示两声音信号相似性的互相关函数可用式(1)来表示[10]。

(1)

式(1)中积分时间为无穷大,在实际应用中一般在有限时间内计算积分,如式(2)所示。

(2)

将式(2)离散化可表示为式(3):

(3)

式中:N为采样点数;k为延时序号。

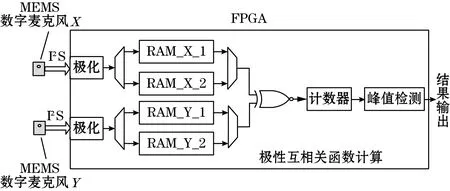

为了简化式(3)以便于在FPGA中用数字电路实现和减少数字电路资源开销,可将两路输入信号x(n)和y(n)量化为极性信号,即只取其正负号,从而得到极性互相关函数计算公式(4)。

(4)

式中:

J. H. Van Vleck等证明随机信号极性化后仍然保持原信号的平稳性与各态遍历性,极性互相关函数与直接互相关函数在相同的时延τ时到达峰值[11],所以求出极性互相关函数峰值点即可得出声音信号x(t)和y(t)的时延差值。

在计算极性互相关函数值时,如果不除以序列长度N,则极性互相关函数的幅度会变化,但是其波形形状和峰值所对应的时延值并不会改变[12],所以在FPGA实现时可不用除以N。

2 时延测量总体设计方案

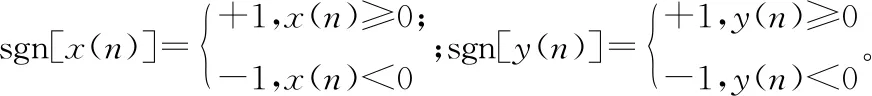

为了用数字电路实现两路声音时延测量,设计如图2所示的互相关法声音时延测量方案。该方案主要包括数据采集模块和数据处理模块。数据采集模块负责对两路声音信号进行同步数据采集,数据处理模块负责对进入数据处理模块的两路声音数据进行极性互相关运算和峰值检测,从而得到两路声音的时延值。

图2 互相关法声音时延测量系统框图

声音采集模块使用两个微机电系统(micro electro mechanical systems,MEMS)数字麦克风ICS-43432作为声音传感器同步采集两路声音信号,将声音信号转化为24位的数字信号,并通过I2S (inter-IC sound)接口传入数据处理模块;数据处理模块以FPGA EP4CE6作为数据处理核心,FPGA将两路声音信号做极化处理,完成极性互相关运算,并通过峰值检测实现声音时延的确定。

3 极性互相关时延测量设计

采用自顶向下的方法利用硬件描述语言Verilog在FPGA中完成极性互相关算法声音时延测量数字电路的设计与实现。首先明确极性互相关测量声音时延的实现步骤和功能模块,然后采用Verilog的可综合子集描述每个功能模块的硬件行为,最后由逻辑综合工具自动完成从硬件描述语言到门级电路的转换。利用极性互相关算法计算两路声音信号时延值的流程如图3所示。首先,2个MEMS数字麦克风分别采集2路声音信号,当2路声音数据分别采集满一帧时计算2路声音数据的极性互相关函数值;然后进行峰值检测;最后利用峰值位置得出时延值。

图3 一帧信号时延值计算流程图

3.1 信号采集

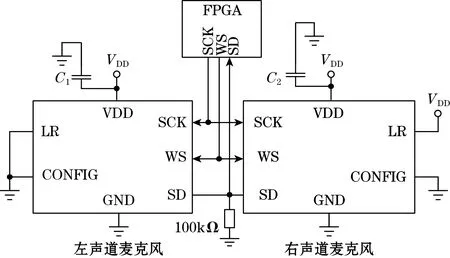

FPGA控制2个MEMS数字麦克风同步采集2路声音信号,两MEMS数字麦克风构成左右声道,按照I2S格式将X和Y两路声音数据传入FPGA,2个MEMS数字麦克风信号采集电路如图4所示。根据数字麦克风ICS-43432的频率响应和奈奎斯特采样定理设置数字麦克风采样率为50 kHz,即WS (word select)时钟频率为50 kHz。设置一帧信号采集的数据点N为1 024,即一帧声音信号的时长为20.48 ms。

图4 信号采集电路

3.2 数据极化处理

在实际基于FPGA对输入数据进行极化处理时可按以下方式进行。若24位声音数据的符号位为“1”,则表明此数据为负数,用“0”表示;若24位声音数据的符号位为“0”,则表明此数据为非负数,用“1”表示。极化处理后的数据节省了随机存取存储器(random access memory,RAM)资源,同时可用同或操作代替乘法操作,避免了乘法器的使用,提高了数据处理速度,也使极性互相关运算更易于在一般FPGA中用数字电路实现。

3.3 RAM配置与数据存储

如图2所示,配置4个双口RAM用作数据缓冲,每个RAM数据位宽为1 bit、数据深度为2 048 bits。4个RAM分为两组,X组2个双口RAM,Y组2个双口RAM,用以完成乒乓操作,保证数据可以连续地进行极性互相关运算。对于极化处理后的数据,每来1个声音数据进行1次存储,所以RAM写时钟为50 kHz。为了极性互相关运算读取数据的方便,X组RAM从地址1024开始写入,直到地址为2047,一帧数据1024点刚好写完;Y组RAM从地址0开始写入,直到地址为1023,一帧数据1024点刚好写完。

3.4 互相关运算状态机设计

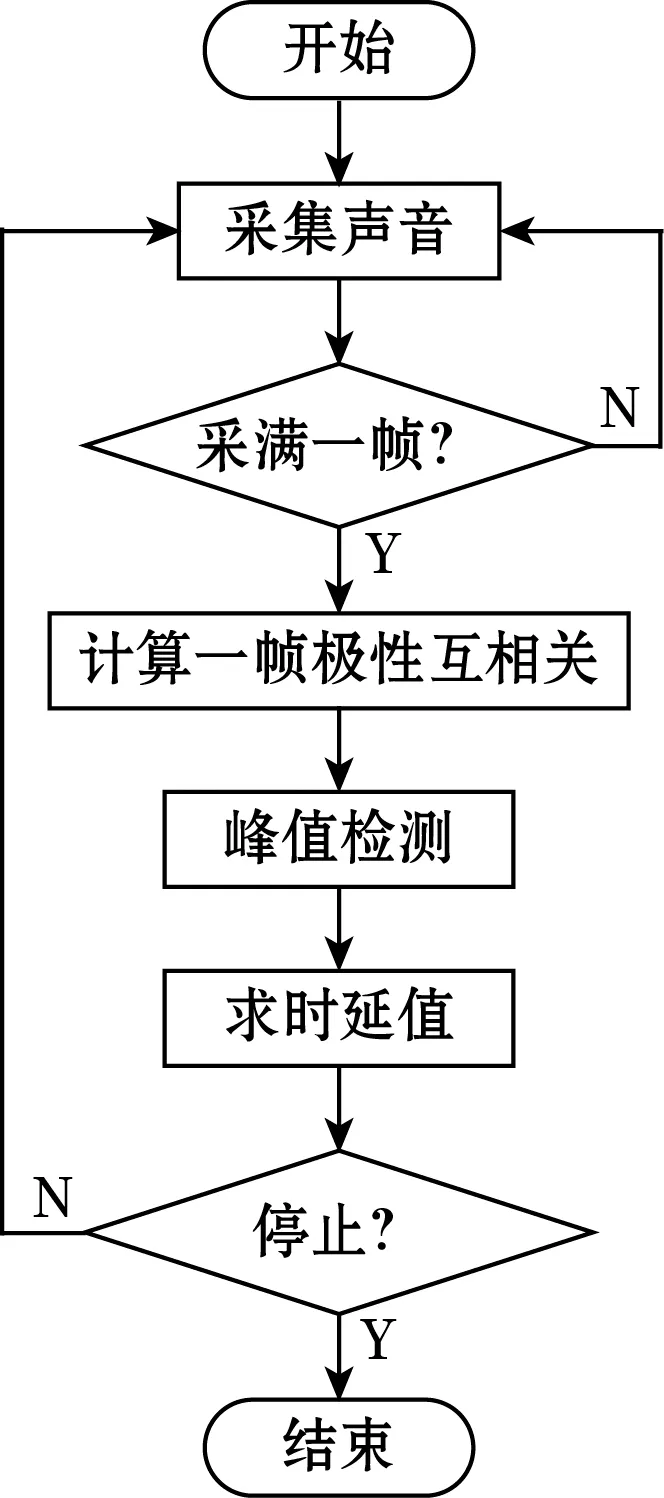

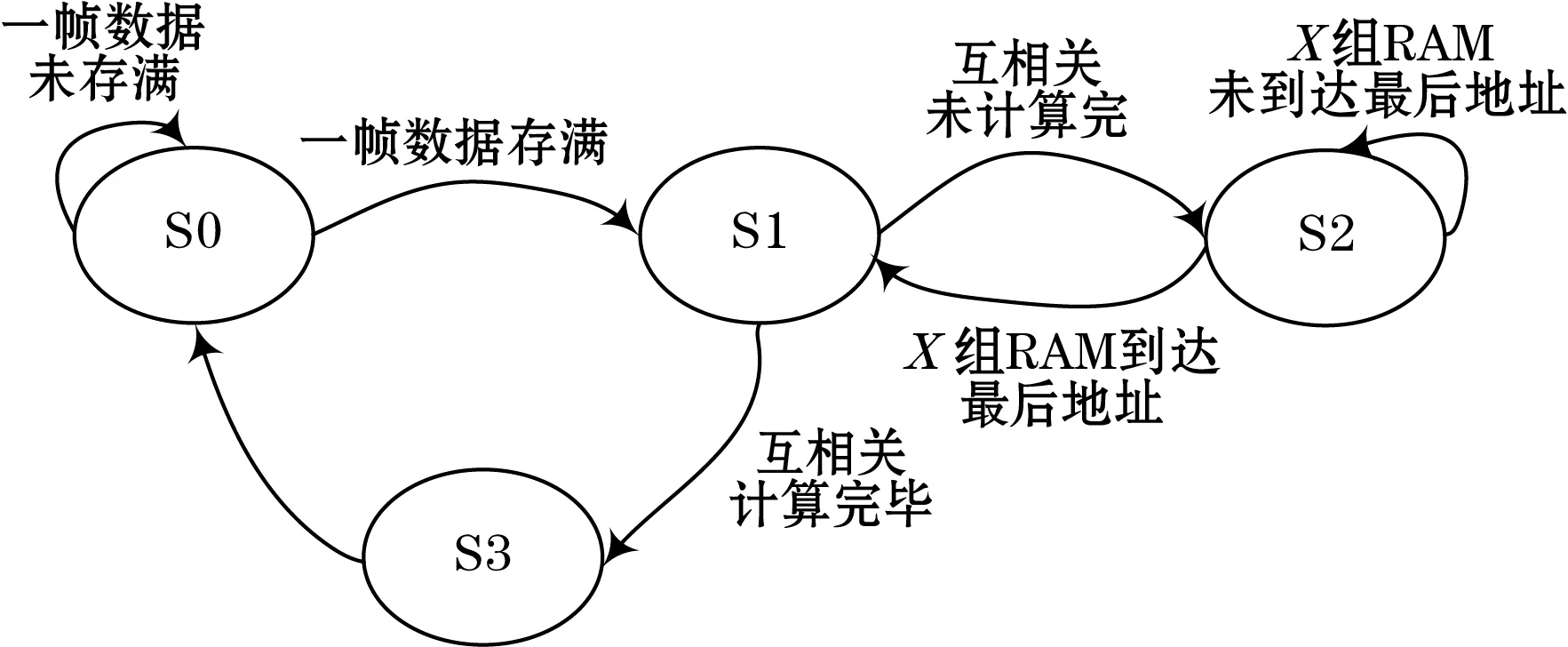

极性互相关运算是一个移位、同或、累加的过程,且X、Y两路声音各1 024个采样点进行极性互相关运算会有2 048个极性互相关函数值,因此运算过程中从RAM中读取数据有一个地址循环的过程,并且其运算过程是非常消耗时钟的。为加快极性互相关运算,设置RAM读时钟和极性互相关运算时钟为125 MHz。考虑到极性互相关运算的复杂性,设计如图5所示的状态机以保证极性互相关算法的数字电路实现。

图5 极性互相关运算状态机

状态机有4个状态变量,状态机的开始状态为S0状态,在S0状态判断两路数据是否都存满了1帧,当未存满1帧时继续进行数据采集与存储,当两路数据都存满了1帧时进入S1状态。在S1状态判断2 048个极性互相关函数值是否计算完毕,当计算完毕时进入S3状态;当未计算完毕时进入S2状态并给出2组RAM初始的读地址,X组RAM初始地址从1024开始且每次初始地址加1,Y组RAM每次初始地址都为0。在状态S2时,每来1个时钟2组RAM读地址各加1,并在下个时钟上升沿时分别读取2个RAM的输出数据进行同或操作,然后对同或结果进行累加;当X组读地址等于最后1个地址时进入S1状态,表明1个延时对应的极性互相关函数值计算完毕,否则继续在S2状态进行地址递增。S3状态时,所有时延对应的互相关值计算完毕。

3.5 峰值检测

对两路数据各1 024点做极性互相关运算时,首先将第1个时延值所对应的极性互相关值认为是极性互相关函数的最大值,然后在每1个时延所对应的极性互相关值计算完毕时,与极性互相关最大值作比较,若大于极性互相关最大值,则认为它是新的极性互相关最大值并记录其位置序号。如此每来1个新的极性互相关值就比较1次,当极性互相关计算完毕时可得到峰值及其位置序号,并由峰值位置得到时延值。

4 仿真与实验测试

4.1 极性互相关时延测量仿真

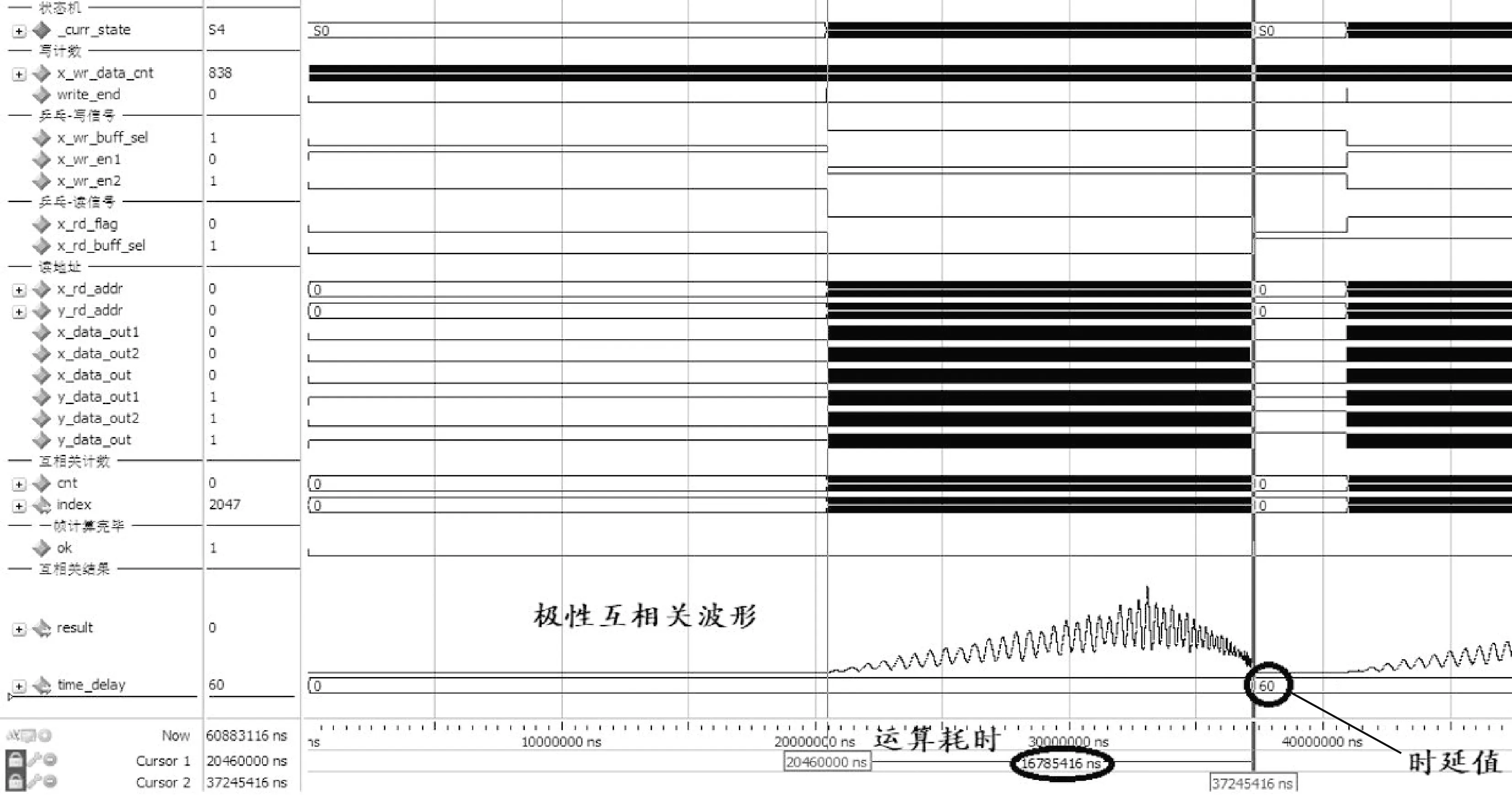

利用Verilog硬件描述语言设计极性互相关运算电路后,在ModelSim中进行仿真测试。仿真时设置互相关运行时钟为125 MHz,数字麦克风采样率为50 kHz。利用Testbench (测试平台)代码将数字麦克风预先采集到的两路声音原始数据读入以代替两路声音信号的采集,然后进行取符号、RAM写入/读取和极性互相关运算,仿真结果如图6所示。并且在Matlab中调用互相关函数计算两路声音极性数据的时延值作为对比参照。

图6 极性互相关运算仿真结果

由仿真结果可以看到,两路声音数据各1 024点进行极性互相关运算的运算时间为16.785 416 ms,第1帧两路声音数据的时延运算结果为60 μs,且Matlab中调用互相关函数分别计算各帧极性互相关时延结果和ModelSim仿真中各帧运算结果相同。根据极性互相关仿真结果和Matlab极性互相关计算结果可知,本方案设计的极性互相关运算电路运算结果与Matlab计算结果一致。

4.2 极性互相关时延测量实验

为了验证方案的实际声音时延测量效果,在室内进行了声音时延测量实验。将极性互相关时延运算电路固化在FPGA中,使用普通可听声作为测试声源,声源与两数字麦克风在同一条直线上,且声源不在两数字麦克风之间,如图1所示。两数字麦克风采集两路声音信号,极性互相关运算电路实际测算出两路声音信号的时延值,经过多次测量取平均值;并将采集到的声音信号原始数据导入到Matlab中,调用互相关函数计算出两路声音数据的时延值。调整两数字麦克风之间的距离进行相同实验,得到不同间距下的时延结果,测量结果如表1所示。根据实验结果显示,在室内条件下,设计的时延测量电路实际测算出的时延值与Matlab计算出的时延值基本一致。

4.3 声源定位实验

在基于TDOA的声源定位算法中求得若干组时延值就可根据声源与麦克风阵列的几何关系推导出声源的位置信息。将此声音时延测量方案应用于实际基于麦克风阵列的声源定位系统中去估计声源的方位角,设计如图7所示的麦克风阵列声源定位系统原型机。MEMS数字麦克风组成麦克风阵列采集多路声音信号后,将多路声音信号送入FPGA实现的声源定位数字运算电路中,从而运算得到声源的方位角信息。

(b)反面图7 麦克风阵列声源定位系统原型机

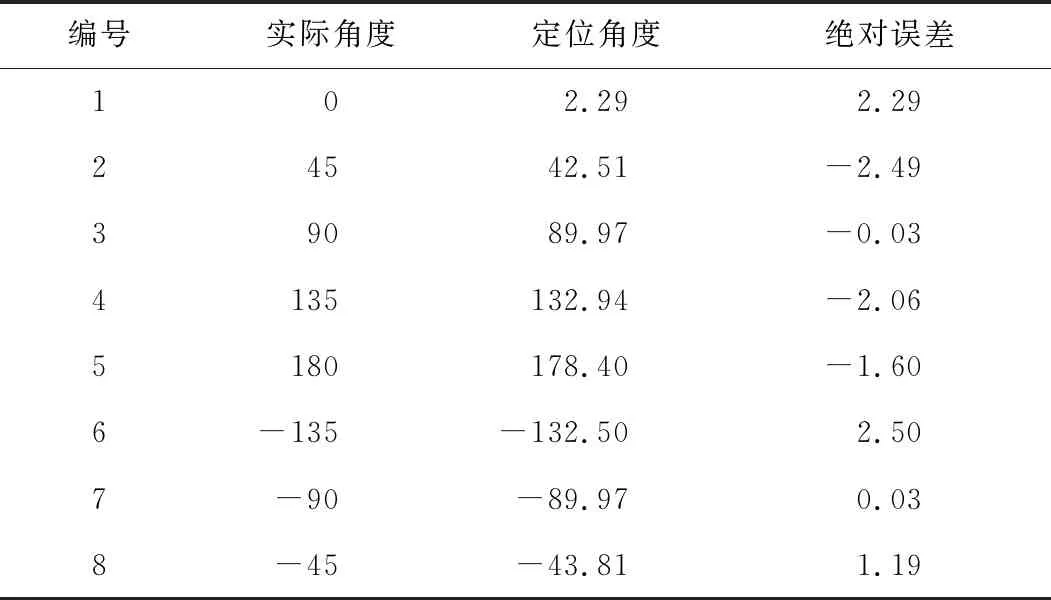

在室内用普通可听声对声源定位系统进行测试,经过10次测量取平均值得到1个方位角,然后每隔45°移动声源位置,得到多组声源定位结果,方位角定位结果如表2所示。从表2可以看出,在室内条件下,方位角测量结果的绝对误差在±3°以内,表明设计的声音时延测量电路在声源定位系统中运行良好。

表2 声源定位结果 (°)

5 结束语

在研究互相关算法理论的基础上,提出了一种应用于声源定位系统中的互相关法声音时延测量的数字电路实现方案,该方案采用MEMS数字麦克风作为声音传感器采集声音信号,在FPGA中利用硬件描述语言Verilog设计了互相关运算数字电路。基于FPGA与MEMS数字麦克风的纯数字电路方案来处理多路声音信号,提高了测量电路的稳定性与可靠性,减少了软件方案运行速度慢、难于采集和处理多路声音信号等问题。通过Matlab和FPGA验证了该方案进行声音时延测量的准确性,将此方案应用于实际的基于麦克风阵列的声源定位系统中,测得的声音时延满足声源定位系统对时延的要求,系统声源定位效果良好。同时该互相关法时延测量数字电路方案对其他工业领域的时间延迟测量也具有参考意义。