一种毫米波封装的设计与优化方法

程 琛, 刘丽虹, 夏 冬, 顾炯炯, 李全兵

(江苏长电科技股份有限公司, 江苏 无锡 214437)

1 引言

毫米波技术的研究起步很早,军事用途的研究最早可以追溯到二战结束前后。 近年来随着5G 通信标准的商业化,毫米波应用正变得越来越热门。 5G 的数据传输速率可超过10 Gbps, 是4G LTE 标准的100倍。 为了实现如此高速的传输,5G 网络需要支持毫米波频段以获得更宽的带宽。 与此相对应,在毫米波封装上,封装设计必须考虑更多的因素,尝试更多的方法,必须仔细设计和优化走线、Pad 和过孔,使之不会妨碍到芯片上的射频设计。 早先的军用毫米波产品大多采用陶瓷或者金属封装,这些封装拥有很好的可靠性,但是成本很高,并不适合民用市场[1]。 于是使用其他封装形式实现毫米波的研究如雨后春笋一般兴起。例如,文献[2]中,NXP 半导体研究了一种FOWLP(Fan Out Wafer Level Package)的毫米波封装;高通最新的QTM527 毫米波模组中则使用了SoC (System on Chip)封装形式,通过模组整合的方式有效控制尺寸,将射频收发器、前端器件和天线阵列都集成了进去。

可以看出, 在现有的民用毫米波封装产品中,先进 封 装 例 如 WLCSP (Wafer Level Chip Scale Package)、SoC 等占了主体。对于部分结构较简单的毫米波器件封装来说,先进封装成本仍然偏高。 因此,本文选择了传统的LGA(Land Grid Array) 封装进行设计,通过对走线、焊盘和过孔结构的仔细优化,达成了设计目标,并实现了产品性能与成本的良好平衡。

2 S 参数含义与分析

由于频率很高, 本文中使用S 参数(Scatter Parameter,散射参数)来表征互联的信号质量。 S 参数是一种高频下描述元器件的射频电气行为的工具,其通过元器件对入射信号作出“ 反应”即散射后,从元器件外部“ 散射”出可测量的物理量来对其进行描述。

常用的S 参数表达式为Sij,含义为从j 口注入,在i 口测得的能量。 以一个4 端口网络为例,S 参数可以分成以下几类。

S11、S22、S33、S44:在工程上称为回波损耗,表示互联结构对信号的反射, 它是由于阻抗不匹配而引起的。这种阻抗不匹配可以由驱动源、传输线和负载的阻抗不同引起,也可由传输线的不连续(过孔、短截线)以及腔体谐振等因素引起。 另外,返回路径不连续等因素也会导致阻抗不连续[3]。

S21、S12、S34、S43:从端口进入的信号并不能完整无损地到达互联结构的末端,S21即表示从端口2 出来的正弦波和从端口1 进入的正弦波的比值,工程上称为插入损耗。 互联通道产生插入损耗主要有以下几种[4]:

(1)金属电阻性损耗,较长的电流路径与趋肤效应使得电流横截面减小,都会使得电流感受到的阻抗增加,从而增加金属电阻性损耗;

(2)介质的极化损耗,交流电场使得介质中的电偶极子极化方向不断变化,也需要消耗能量;

(3)信号反射引起的损耗;

(4)和邻近传输线发生耦合而导致部分能量传递到邻近传输线;

(5)辐射损耗。

从插入损耗的来源可以看出, 通过优化回波损耗,可以改善(3);通过优化串扰,可以改善(4)和(5);(1)和(2)可以通过使用高速板材、减少封装走线长度实现。 这是由于高速板材介电常数和损耗角正切参数均较低, 低介电常数在同样阻抗的规格下走线会更宽,有利于增大电流的截面积,降低电流感受到的阻抗;低损耗角正切有利于减小介质极化损耗。

S13、S31、S24、S42为近端串扰,S14、S41、S23、S32表示远端串扰,统称为串扰。 串扰的大小与互联线间耦合长度、线间距、信号上升时间、介质厚度、介电常数等因素都有关系[5]。 但对于本案例而言,由于多个参数已经确定,并不能在后续优化中起到作用。

3 毫米波通道设计与优化

3.1 案例设计要求

该案例的设计要求是在0~30 GHz 频段上都满足表1 所列信号质量的要求。

表1 案例设计要求

按照以上的分析思路,在具体设计上,为适应毫米波苛刻的要求,先期就已经采取了如下的措施:

(1)选用较能适应高频的FC-LGA 4 层板设计,使用倒装凸点连接取代引线键合,形成最短电路,提升高频适应性;

(2) 采用介电常数/损耗角均较小的高速高频板材(介电常数/ 损耗角正切:3.4/0.003@10 GHz),为此使用了成本较高的无芯基板工艺;

(3)走线已经全部进行50 Ω 阻抗管控,最小化信号在走线上的反射。

本案例使用HFSS 软件进行优化工作, 扫频频段为0~50 GHz。待优化的毫米波通道有两种,Net1~Net4为短直走线,Net5 为长弯走线,如图1 所示。

图1 待优化毫米波通道结构图

初版设计使用HFSS 软件仿真后的信号质量如表2 所示。

表2 优化前回波损耗/ 插入损耗结果

由表2 可以看出, 上述措施并不足以满足毫米波产品电性能的要求,需要进行进一步优化。

3.2 毫米波通道优化

毫米波通道优化流程可以分成以下几个步骤:问题定位→制定针对性优化策略→设置优化变量并建模→执行相关项目优化(回损、串扰)→判断优化是否达标→优化完成。 如图2 所示。

图2 毫米波通道优化流程

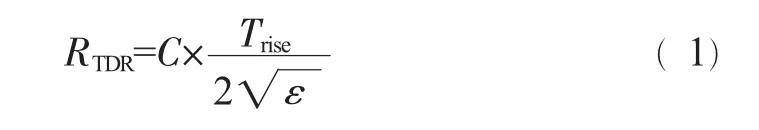

使用HFSS 的时域求解功能求解TDR(时域反射)以期定位阻抗不连续点。 由于TDR 存在分辨率的概念,TDR 分辨率公式如下所示:

式中,RTDR为TDR 的分辨率,C 为光速,Trise为信号上升时间,ε 为板材的介电常数。

考虑到最长的通道Net5 总长仅约1.5 mm, 需要获得较高的TDR 分辨率。综合分辨率与求解速度的考虑,设置TDR 上升沿为3 ps,获得的TDR 结果图如图3 所示。

可以看到在一个50 Ω 阻抗区域的两侧,有两个明显的阻抗偏低区域(见图4)。 由于初版设计时已经对走线进行了阻抗管控,因此可以看出,初版设计中的反射主要来源于过孔区域偏低的阻抗,设法提高过孔区域的阻抗将成为一个重要的优化方向,于是制定如下优化策略:

(1)减小过孔的阻抗不连续段的长度。初始设计为LGA 4 层板设计,修改为3 层板;

(2)尽量增加过孔区域的阻抗,核心策略是增大过孔周围的反焊盘,以期减小过孔与周围参考地之间的电容,增大电感,根据特性阻抗公式:

可以有效地增加过孔区域的阻抗。 基于此思路,对Net1~Net4 和Net5 通 道 分 别 进 行 优 化。 对 通 道Net1~Net4 的过孔区域设置优化变量,见表3 和图5。

图4 阻抗不连续区域(图中红字标示处)示意图

表3 通道Net1~Net4 过孔区域优化变量设置

图5 Net1~Net4 通道优化变量示意图

对于Net5 通道则不能使用这种方案。 由图6 可见,通道Net5 凸点周围分布着6 个地凸点,无法使用改变反焊盘半径调节过孔阻抗的方法,因此需要改变优化策略,使用阻抗变换线来进行阻抗匹配,且设计为渐变阻抗匹配线来获得更好的宽带匹配性能。

图6 通道Net5 过孔分布的地凸点(图中高亮处)

使用阻抗变换线重新建模后的Net5 如图7 所示。通道Net5 过孔区域优化变量设置见表4。

图7 使用了阻抗变换线重新建模后的Net5 通道

表4 通道Net5 过孔区域优化变量设置

优化前后过孔对比如图8 所示, 可见优化后过孔密度加大,直径增加且交错排布。

图8 优化前后过孔对比

如前所述,互连线间耦合长度、线间距、信号上升时间、介质厚度、介电常数等因素都会影响串扰的大小。 但案例中封装布局、工作频率、介质厚度和材料参数都已经确定(该案例对封装总厚度有要求),这些参数都不能作为优化的方向,因此最终决定优化地过孔排布, 使用地过孔的优化排列尽可能屏蔽信号串扰,优化方案如下:

(1)加密地过孔,在满足工艺允许孔间距要求的基础上尽量增加过孔密度;

(2)优化地过孔排列方式,第二排过孔尽量放置在第一排过孔之间,如图7 所示;

(3) 在工艺允许范围内加大过孔直径, 从80 μm增加到了100 μm。

4 优化结果与分析

回波损耗/插入损耗优化后结果如表5 所示。

表5 优化后回波损耗/ 插入损耗结果

串扰优化前后结果如表6、表7 所示。

分析优化结果可见:

(1)优化前后回损、插损都得到极大提高,回损提升10 dB 以上,使用了渐变匹配线的Net5 全频段内提升达到13 dB; 插损从-0.5 dB 左右减小到-0.2 dB 以下。 两项指标均满足设计要求。

(2)由于重点优化了Net5 周围的过孔排布,之前未通过的Net1、Net4 与Net5 之间的串扰明显改善,其他网络之间的结果略有提升,最终优化的结果同样达到了设计要求。

表6 优化前串扰结果

表7 优化后串扰结果

5 总结

如前所述,使用传统封装要达成毫米波频段的优化目标, 需要同时在封装形式/板材和局部结构等多方面进行针对性的设计和优化:

(1)封装形式/板材使用FC-LGA 封装,最短化信号路径;板材选用高频高速基板,走线全部进行50 Ω阻抗管控,以期在优化前就达到较好的基础性能。

(2)在重点信号的优化上,通过对一切可能影响到过孔阻抗的结构进行参数化建模并优化,以期平滑过孔与走线间的阻抗差异来达到减小反射的目的;通过优化地过孔排列来优化串扰。