改性PVDF及其多元共聚物在薄膜电容器中的应用

孟庆文 胡帅捷

(浙江巨化股份有限公司氟聚合物事业部,浙江 衢州 324004)

0 前言

近年来,介质电容器由于在现代电子电气系统中的广泛应用而受到越来越多的关注,如电动汽车[1]、智能电网[2]、脉冲电力系统[3]等。与超级电容器、锂离子电池等电化学介质电容器相比,介质电容器的功率密度较大,它通过局部偶极子的旋转来存储和释放能量。然而,电容器的能量密度仍然很低,无法满足紧凑、可靠和高效电力系统的要求。因此,提高介质电容器的能量密度是近十年来研究的关键问题。研究人员研究了诸如全聚合物介电材料、陶瓷填充PVDF基高介电材料、导电填料填充PVDF 基高介电材料、核壳结构粒子填充PVDF 基高介电材料等新型复合材料。

1 聚合物介电性能

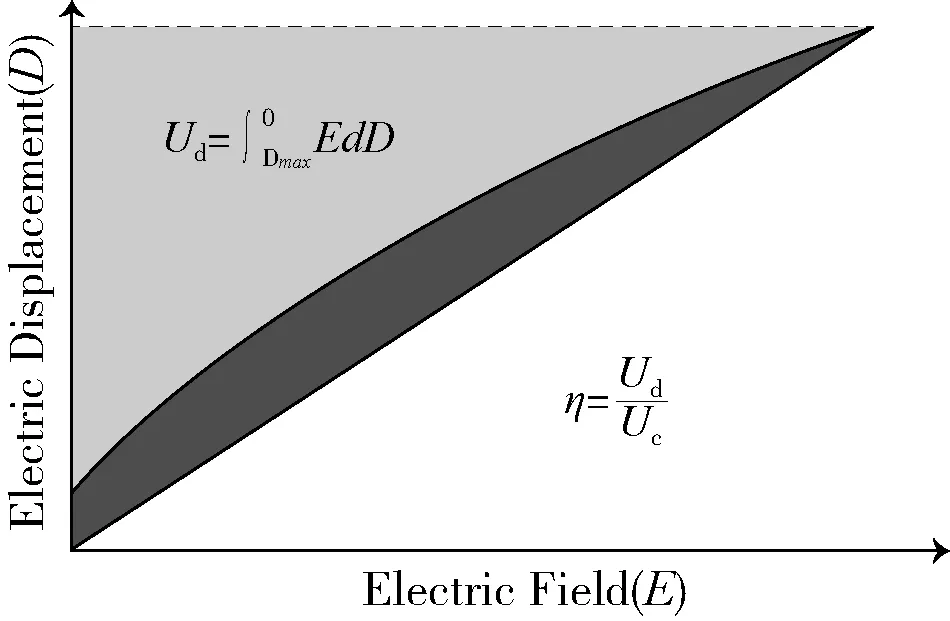

图1为D-E迟滞回线充放电循环示意图。

图1 D-E迟滞回线充放电循环示意图

一般情况下,在图1所示[4]的充放电循环中,介质中放电的能量密度(Ud)由外加电场(E)和电位移(D)共同决定[5],见式(1):

(1)

其中,电位移(D)与外加电场(E)有关,见式(2):

D=ε0εγE

(2)

式中,ε0为真空介电常数,ε0=8.85×1012Fm-1;εγ为相对介电常数即介电常数。另外,当外加电场(E)达到材料失效前的最大场强即为材料的击穿场强(Eb)时,将得到该材料最大的能量密度(Ud)。

对于线性介电材料,介电常数与外加电场无关,能量密度如式(3)所示:

(3)

对于非线性介质,因为存在能量损耗和放电效率的问题,D和E的充放电曲线通常不会相互重叠。对于线性介质,能量密度由图1中三角形区域决定。对于非线性介质,能量密度由浅灰色区域决定,深灰色区域是充放电循环中损耗的能量。 充放电效率(η)由充电电能(Uc)和放电电能(Ud)决定,见式(4):

(4)

因此,可以通过控制εγ、Eb和η,得到尽可能大的Ud。

2 增强击穿场强

击穿强度决定了适用于介质的最高电场。当外加电场超过击穿强度后,会发生不可逆的介质损伤,使储能电容器无法进行充放电循环。由式(3)可知,能量密度与线性介质的击穿强度成二次方关系。对于非线性介质,由于电位移仍然与外加电场成正比,能量密度由电位移和外加电场共同决定,所以该公式仍有意义。

击穿过程在现象学上定义为击穿路径的增长[6-8]。在这一过程中,内部击穿强度较低的区域首先击穿,击穿相由绝缘体变为导体。之后,随着电极间电场强度的进一步升高,击穿区域开始成长为路径并收敛。当击穿路径穿过纳米复合材料,连接两个电极时,发生整体击穿,材料失效。

对于PVDF基纳米复合材料而言,陶瓷纳米填料与高分子基质之间的界面将会是击穿过程中最为薄弱的环节。在非均相体系中,由于电介质材料中的介质分布不均匀或材料中存在晶格畸变、晶界、相界等缺陷[9-10],当施加电场时,这些区域成为自由电荷运动的阻碍,使之在界面处发生聚集,从而产生界面极化。虽然PVDF基聚合物的介电常数高于大多数聚合物,但仍比铁电陶瓷低几个数量级,这将导致聚合物/陶瓷界面附近的电场发生畸变,影响材料的介电性能。

因此,需要提高聚合物基质与填料之间界面的强度,以此来提升材料的击穿场强。

2.1 抑制载流子移动

目前研究表明,一些方法可以有效地提高复合材料的介电性能,提升击穿强度和保持低介电损耗。例如,采用绝缘表面活性剂[11-12]、接枝聚合物[13]或构建核-壳结构[14-15]等可抑制由导电填料产生的电荷泄露,同时也有助于提高介电常数。此外,采用具有多重核-壳结构的低维填料将进一步优化介质性能[16-17],提高击穿强度。

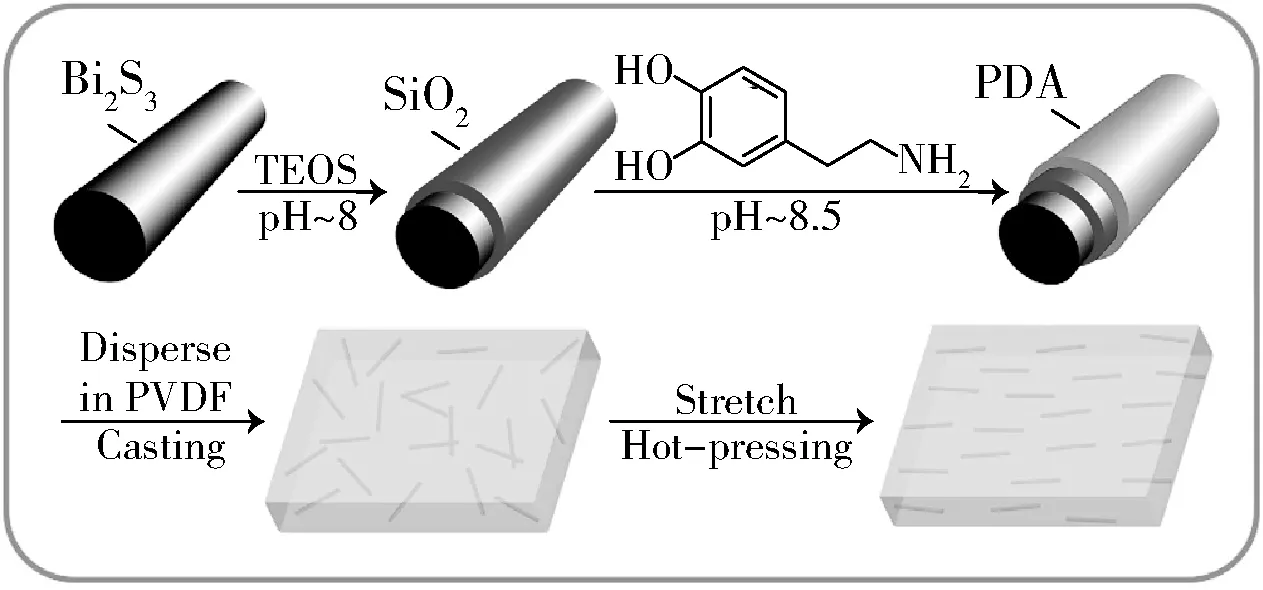

对于纳米导电填料,构建核-壳结构并控制其分布,使得在填料加入较少的情况下抑制介电损耗,同时保持高介电常数和击穿场强。有研究表明,在纳米复合材料中采用低维具有单层核壳结构的填料时可以极大地抑制界面极化产生的介电损耗,例如,高绝缘无机SiO2[18-20]或Al2O3[21]。然而,这种核壳结构的填料仍存在有机/无机不相容的界面。此外,还应考虑低维填料的分布。Zhang等[22]考虑了聚合物基质与填料的相容性以及它们在聚合物基体内的定向分布,通过采用具有双层壳核结构取向填料来有效抑制介电损耗并保持高介电常数。他们将一维半导体Bi2S3纳米棒依次涂覆绝缘SiO2和多巴胺(PDA),并通过高温拉伸和热压工艺对其进行排列,从而得到定向的Bi2S3@SiO2@PDA/PVDF复合纳米材料,其加工工艺如图2所示。

图2 Bi2S3@SiO2@PDA/PVDF复合材料加工示意图

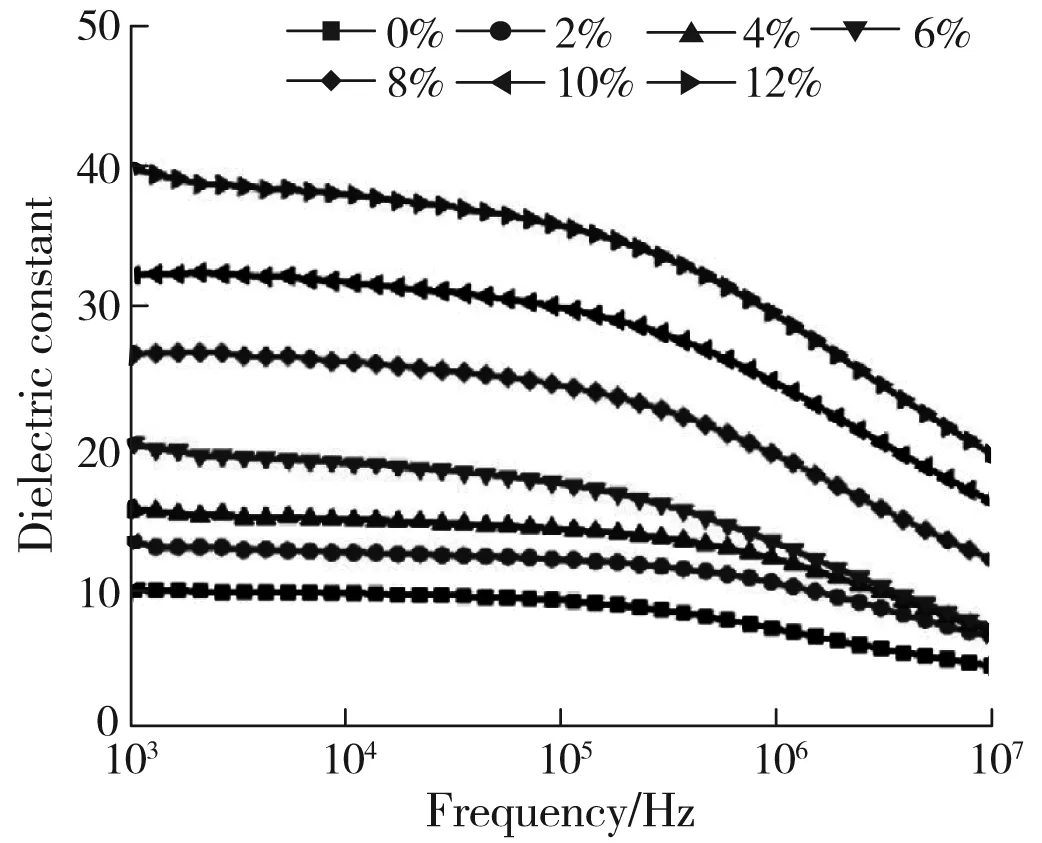

Zhang等[22]研究了具有取向的Bi2S3@SiO2@PDA/PVDF复合材料的介电性能、电学行为及其各向异性,并与无壳层或无排列的Bi2S3纳米棒复合材料进行了比较。对纯PVDF和不同填料含量的Bi2S3@SiO2@PDA/PVDF纳米复合材料在沿平行方向和垂直方向进行测试,其随频率变化的介电常数和介电损耗如图3所示。

(a) 平行填料方向的介电常数

显然,随着Bi2S3含量的增加,总介电常数增大;而在低频范围内,即使在平行方向上,损耗切线也很低(小于0.045)。由于绝缘的SiO2@PDA双涂层限制了载流子的运动,抑制了载流子在相邻半导体纳米棒之间的隧穿,从而有效地抑制了损耗[23]。

当采用Bi2S3@SiO2核壳结构时,由于Bi2S3被高度绝缘的SiO2包覆,界面电荷密度突然下降,损耗明显抑制。这里采用了双壳层外加PDA层,这将增强抑制损失的效果。

3 增加介电常数

在聚合物介质中,PVDF在103 Hz时的介电常数可达8.2,远高于其他类型的含氟聚合物。这主要是由于PVDF及其共聚物的结构和内部有强极性的C—F键以及自发偶极极化造成的。

单纯的聚合物材料已很难满足现有的工业需求,一个简单的方法就是向其中加入第二相的填料。目前,已有很多种聚合物被用作基体来制备聚合物基高介电复合材料。研究人员通常采用化学计量聚合、无机/有机纳米复合材料和聚合物共混以及后处理技术等方法来调整其化学组成和物理结构[24-25]。

通常,将高介电常数纳米粒子引入聚合物基质中制备介电纳米复合材料,其中高介电常数填充剂包括铁电陶瓷、金属颗粒和碳基纳米材料。例如,将具有超高介电常数的陶瓷颗粒,如BaTiO3[26]、Ba0.6Sr0.4TiO3[27]、Pb(Zr, Ti)O3[28]和CaCu3Ti4O12[29]引入PVDF基聚合物中,可增强材料的介电性能。

近年来,由于石墨烯优异的力学性能、高纵横比、优异的柔韧性、优异的电性能和导热性,得到了广泛关注。此外,石墨烯也是高介电常数聚合物纳米复合材料的理想填料。将石墨烯剥离为寡层石墨烯后再修饰功能化,可以使其在基质中得到均匀的分布,同时也可以增强材料的击穿强度。

Ye等[30]研究合成了超支化聚乙烯接枝聚(三氟乙基甲基丙烯酸酯)共聚物(HBPE-g-PTFEMA)。在氯仿溶液中加入天然石墨,同时加入HBPE-g-PTFEMA作为稳定剂,通过石墨烯之间的CH—π非共价键作用力,对石墨烯进行剥离和功能化。通过简单的溶液浇铸,将寡层石墨烯引入至聚(偏氟乙烯-三氟氯乙烯)[P(VDF-CTFE)]基体中,制备得到石墨烯/P(VDF-CTFE)纳米复合薄膜,其制备工艺如图4所示。

图4 石墨烯/P(VDF-CTFE)纳米复合薄膜制备示意图

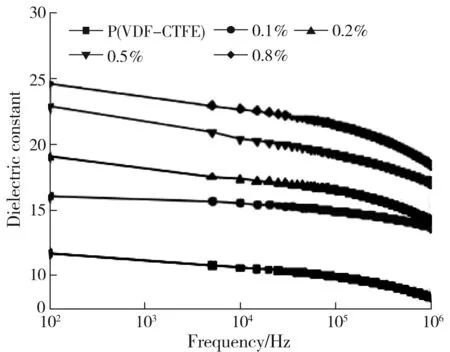

Ye等在室温下测试了石墨烯/ P(VDF-CTFE)纳米复合薄膜的介电特性,包括不同石墨烯体积分数的纳米复合薄膜的介电常数和介电损耗,结果如图5所示。

(a)薄膜介电常数

由图5可知,在102~106Hz范围内,随着频率的增加,介电常数逐渐减小。此外,加入石墨烯后,纳米复合薄膜的介电常数相比纯P(VDF-CTFE)更大。由于石墨烯的加入使得PVDF基质发生从α相到β相的相变,纳米复合膜中电活性相的相对含量增加,从而使纳米复合材料的介电性能更佳。

4 结语

薄膜电容器的电能存储常受聚合物介电常数低的影响。例如,商用的双轴取向聚丙烯(BOPP)在100 Hz时其介电常数仅为2.2,故而其能量密度仅为1.0 J·cm-3[31-32]。所以,基于PVDF的纳米复合材料因其具有高能量密度而成为商业薄膜电容器的重点研发材料。而PVDF基纳米复合材料最主要的优点是经过填料优化或结构设计后其能量密度得到了极大的提高。

另外,也可以通过提高材料充放电效率来提升介电薄膜电容器的效能。已经有研究人员发现,可以通过调整相组成、晶粒尺寸以及优化PVDF基聚合物与纳米填料之间的界面来提高放电效率[33]。

这些研究进展对进一步提高PVDF基复合材料的放电效率具有重要的指导意义。可以说PVDF基复合材料在未来一段时间内仍然是薄膜电容器的主要材料,而填料的优化设计和调节复合材料的相组成是提升材料能量密度的主要方法。