车辆电子设备组合逻辑电路的功耗估计方法*

赵海发

(济源职业技术学院电气工程系,河南 济源 454650)

对于车辆电子设备应用来说,低功耗是工业界所希望的,而且对于某些特殊应用来说,低功耗甚至是至关重要的[1,2,3];随着数字技术和超大集成规模电路(Very Large Scale Integration,VLSI)的发展,电路本身的功耗特别引人关注,尤其是在多芯片模块中,随着功耗的增加,散热成了一个日益严重的问题.因此,对于车载电路特别是车辆电子设备组合逻辑电路中的功耗估计成为近年来研究的热点问题之一;而组合逻辑电路大多由各种门电路构成,这些门电路的开/关切换必然消耗功率,所以对门的开/关切换的功耗估计就与门的开关(转换)量估计问题直接相关.

文献[4]针对目前集成电路功耗估计和低功耗设计的重要性以及常用技术进行了综述;随着集成电路工艺水平的提高,静态功耗也随之增加,文献[5]归纳分析了几种CMOS静态功耗的估计方法,并与HSPICE高精度模拟法在速度与精确度上进行了对比;文献[6]针对基准电路提出了一种功率估计方法,方法考虑了估计精度与估计时间之间的权衡.

基于概率方法的功耗或电流估计具有独特的优势,因为这种方法无需依赖耗时的仿真就可得到统计估计值;文献[7]针对组合电路的概率电流波形计算提出了一种概率峰值电流估计法;文献[8,9]对最坏情况下的功耗估计进行了研究,但由于需要分支定界搜索,故这些方法只能应用于小型到中等规模的电路;关于组合逻辑门电路的开关量的估计研究最初由文献[10]提出,而在国内鲜见报道.在文献[10]中,为了实现VLSI组合和时序电路中的平均功耗估计,笔者考虑了开关量对门延迟的影响,采用了一般的延迟模型来估计开关量,能自动计算出开关切换率和触发器输出之间的相关性;文献[11]针对开关量的估计提出了一种转换密度计算法,把转换密度对应于电路中门的平均开关速率.该方法将相互连接的组合逻辑模块(而事实上每个模块有一定的延迟)看成一个整体电路,尽管通过将全部模块归并为一个大模块来考虑其相关性,但转换密度通过组合逻辑模块传播,这样就会造成内部线路之间的相关性在传播过程中被忽略,从而造成单个模块的延迟信息被丢失;文献[12]讨论了VLSI电路中主要的功耗来源,重点研究了开关量的计算及其功率估计方法.

为了实现对车辆电子设备组合逻辑电路的功耗估计,本文提出了一种基于概率建模的功耗估计方法.方法把组合逻辑考虑为可变延迟模型,这样可以正确计算出由于门电路的多次转换导致在电路中产生差错的布尔条件,从而得到代表电路中的每个门在不同时间点的切换条件的一组布尔函数;然后计算出在任意特定时间点每个门的开/关概率,把全部门的这些概率加起来,获得整个组合逻辑电路在对应于一个时钟周期的所有时间点的开关量,从而建立起一般组合逻辑网络的功耗估计概率模型.

1 门电路功耗及开关量分析

1.1 功耗模型

首先来分析在对CMOS电路功耗的一个简化模型条件下,CMOS电路的功耗与开关量直接相关.为了分析方便和符合电路实际,假设如下:

1)在一个CMOS逻辑门中,电容仅在门的输出节点;

2)电流或者通过某条路径从Vdd流到输出电容,或者从输出电容流到地;

3)一个逻辑门中的输出电压的任何变化都源于Vdd到地,或者反之.

上述假设对于设计CMOS门来说都是合理的,而且每次CMOS逻辑门开/关消耗的能量输出变化大致等于存储在门的输出电容中的能量变化.如果门是由一个全局时钟控制的同步数字系统的一部分,则可得到门消耗的平均功率为:

(1)

式中Cload为负载电容,Vdd为电源电压,Tcyc为全局时钟周期,Et为每个全局时钟周期内门输出转换数量即开关量(文中的转换、开/关和切换为同一含义)的期望值[11],或每个全局时钟周期内门输出转换数量的等效平均数量.式(1)中的全部参数除Et外都可以从工艺或电路布局信息来确定,而Et取决于正在执行的逻辑功能和初始输入的统计特性.

1.2 静态概率

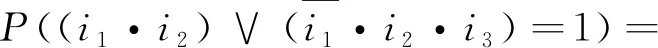

考虑在每个时钟周期的开始,全部门都被预充电,而且仅当门的相关布尔函数满足时,门才完成转换.例如,一个3输入的与或门的布尔函数可以是:

(i1·i2)∨(i2·i3)

(2)

式中i1、i2和i3为初始输入,这时门的输出转换数量的期望值是:

Et=2×P((i1·i2)∨(i2·i3)=1)

(3)

(4)

(5)

(6)

因为第一个乘积项和第二个乘积项不是独立的,而:

(7)

在一般情况下,给定一个由静态概率所描述的不相关输入的布尔函数的不相交覆盖,就能确定出函数值为1的概率,具体由以下两个定理给出[14].

定理1给定一个布尔函数的任意不相交覆盖,函数值为1的概率等于覆盖中每个立方体值为1的概率的总和.

定理2给定一个非相关输入的逻辑函数形式:

(8)

(9)

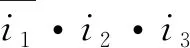

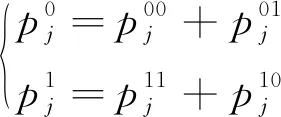

1.3 转换概率

对于静态CMOS组合逻辑来说,当门的输入变化而且仅当描述门的布尔函数的值不同时,门的输出才会变化.例如,一个2输入与门的输出在时钟周期t和t+1之间将变化为:

(i1(t)·(i2(t))⊕((i1(t+1)·(i2(t+1))

(10)

如果t的值为1,这里i1(t)、i2(t)和i1(t+1)、

i2(t+1)分别为在时钟周期t和t+1之间的门输入.式(10)的不相交覆盖为:

(11)

(12)

其他的转换概率遵循同样的方法.

静态概率可以从转换概率来计算,但反过来不成立,因为一个时间帧和下一个时间帧之间存在相关性.静态概率和转换概率之间的关系可以从式(4)和式(12)的定义得到,如:

(13)

静态概率和转换概率可用来计算逻辑电路的Et.例如,根据式(13),可得出式(11)的值为1的概率为:

(14)

对于全部初始输入来说,假设连续输入向量是不相关的,1或0是等概率的,这时全部转换概率可以假定为0.25,而且全部静态概率可以假定为0.5.当然,对于某个特定的初始输入,1或0也有可能不是等概率的,这将导致不均匀转换及其静态概率,这通常由用户提供.

2 功耗估计的概率建模

2.1 一般组合逻辑网络的功耗概率模型

计算一个CMOS组合网络中的平均功耗可以采用第1节的方法,即对于组合逻辑网络中的每个门gi,首先根据网络的初始输入确定出门的布尔函数fi,从而得到fi的不相交覆盖,然后采用定理1和定理2来计算P(fi=1)的值,最后得到整个组合逻辑网络的平均功耗概率模型为:

(15)

式中Ci为第i个门的负载电容,式中∑是对电路中的全部门求和.

一种类似的方法也可以用来计算一个静态CMOS组合网络中的平均功耗,但需要一个2向量输入序列来激活静态门.特别地,如果忽略门的延迟,则一个静态CMOS逻辑门的输出将随着初始输入向量从V0变化到Vt而转换,如果

fi=((hi(V0)=0)∧(hi(Vt)=1))∨

((hi(V0)=1)∧(hi(Vt)=0))

(16)

满足,式中hi为对应于门gi的输出的逻辑函数.

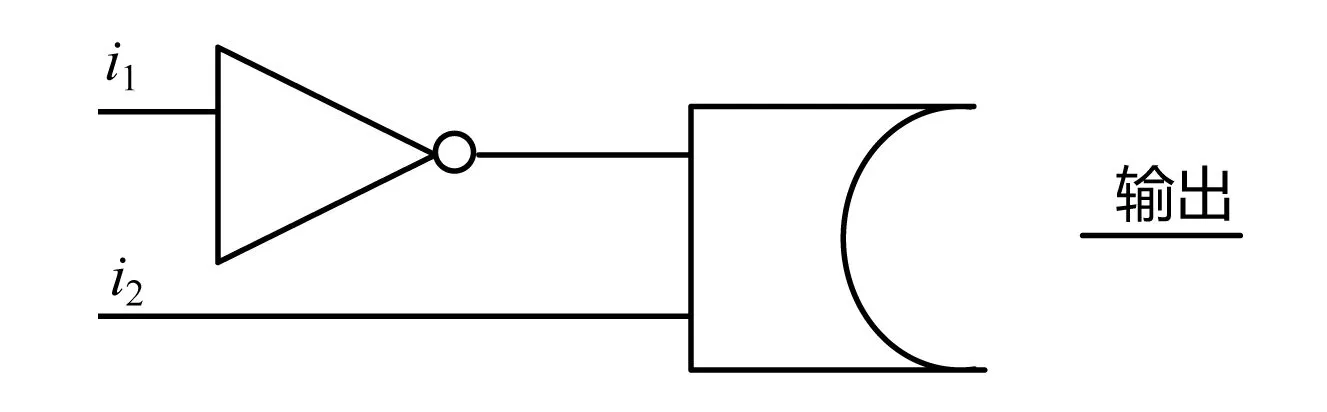

如上所述,对于静态CMOS电路来说,开关量必须基于所考虑的一对输入向量(V0,Vt)来分析.如果门有明显的延迟,则有可能存在输出误差,这种误差也可能导致明显的功耗.如图1所示电路,假设反相器和与门的延迟都是一个时间单位,如果首先应用向量(i1=0,i2=0),其次应用(i1=1,i2=1),则将在输出端得到一个误差,这个误差可能会导致功率损耗.下面就来讨论这种具有延迟的门的可变延迟模型的功耗估计.

图1 静态CMOS电路中的误差

2.2 延迟误差条件下的功耗估计

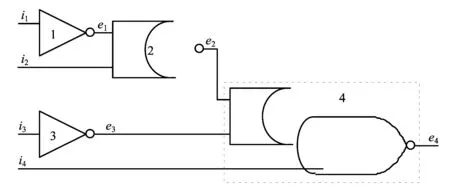

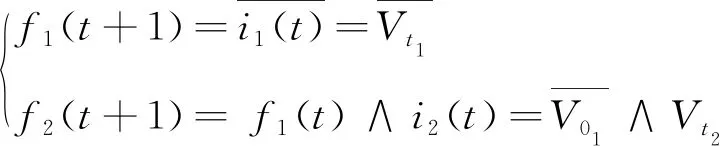

不失一般性,考虑图2所示的多级逻辑组合电路,它由4个CMOS门构成,有4个初始输入和1个输出,图3所示为初始输入节点的信号转换,以及网络内部节点上的可能转换,时间点为归一化时间单位.最初的3个输入i1、i2和i3在时间周期0和1之间同时转换;第四个输入i4是一个延迟到达信号,它在时间点5和6之间转换.在这个例子中,门1和门3的延迟是1个时间单位,门2有2个时间单位的延迟,而门4有4个时间单位的延迟.

图2 一种多级组合电路示例

图3中的ei波形表示第i个逻辑门上的输出信号,每个可能的转换ei,j表示在第j和第j+1个时间点之间的由低到高或由高到低的信号转换.一个门输出的全部可能转换数量可能等于在该门输入的全部可能转换的总和.这些转换被门的传播延迟所延迟.

图3 逻辑门的初始输入和输出信号波形

2.2.1 单位延迟模型

即使在一个单位延迟模型的理想情况下,一个多级网络的门输出节点在响应一个2向量输入序列时可以有多个转换.事实上,一个门输出可能有和网络级数一样多的转换.我们用单位延迟模型来构建描述在离散时间点门输出的布尔函数.也就是说,仅考虑离散时刻t,t+1,…,t+l,其中t是输入从V0变化到Vt的时间,l是网络的级数目.

对于每个门输出i来说,我们来构建l+1个布尔函数fi(t+j),j∈{0,…,l};当门的输出在时刻t+j为1时,则布尔函数fi(t+j)的值为1.注意,由于假设没有门有零延迟,而且在输入从V0变化到Vt之前网络已经是稳定的,则fi(t)为V0在第i个门输出上得到的逻辑函数.最后,就可以通过fi(t+j)和fi(t+j+1)的异或运算来确定是否在离散时间间隔t+j和t+j+1的边界发生转换.

考虑图1所示网络,则有:

(17)

假设两个门都有单位延迟,则:

(18)

则有:

(19)

对于该网络来说,有3个可能的转换:反相器从t到t+1改变状态,与门从t到t+1改变状态,与门从t+1到t+2改变状态.这些转换的布尔方程分别为:

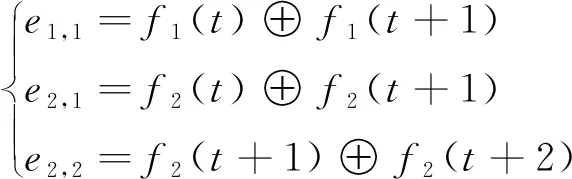

(20)

注意,在图2所示的组合逻辑电路示例中,2个向量序列(V01=0,V02=0)、(Vt1=1,Vt2=1)同时满足e1,1、e2,1和e2,2.

2.2.2 一般延迟模型

一个具有大扇入数的门可能有几倍的反相器的延迟.如果使用归一化时间单位,总可以在电路的门输出端引入单位延迟缓冲器(大于单位延迟)来对逻辑门间的不同延迟进行建模,于是本文提出的建模方法就能够对具有任意门传输延迟的电路进行建模,而无需在电路中引入任何单位延迟缓冲器.

2.3 基于概率建模方法的伪代码

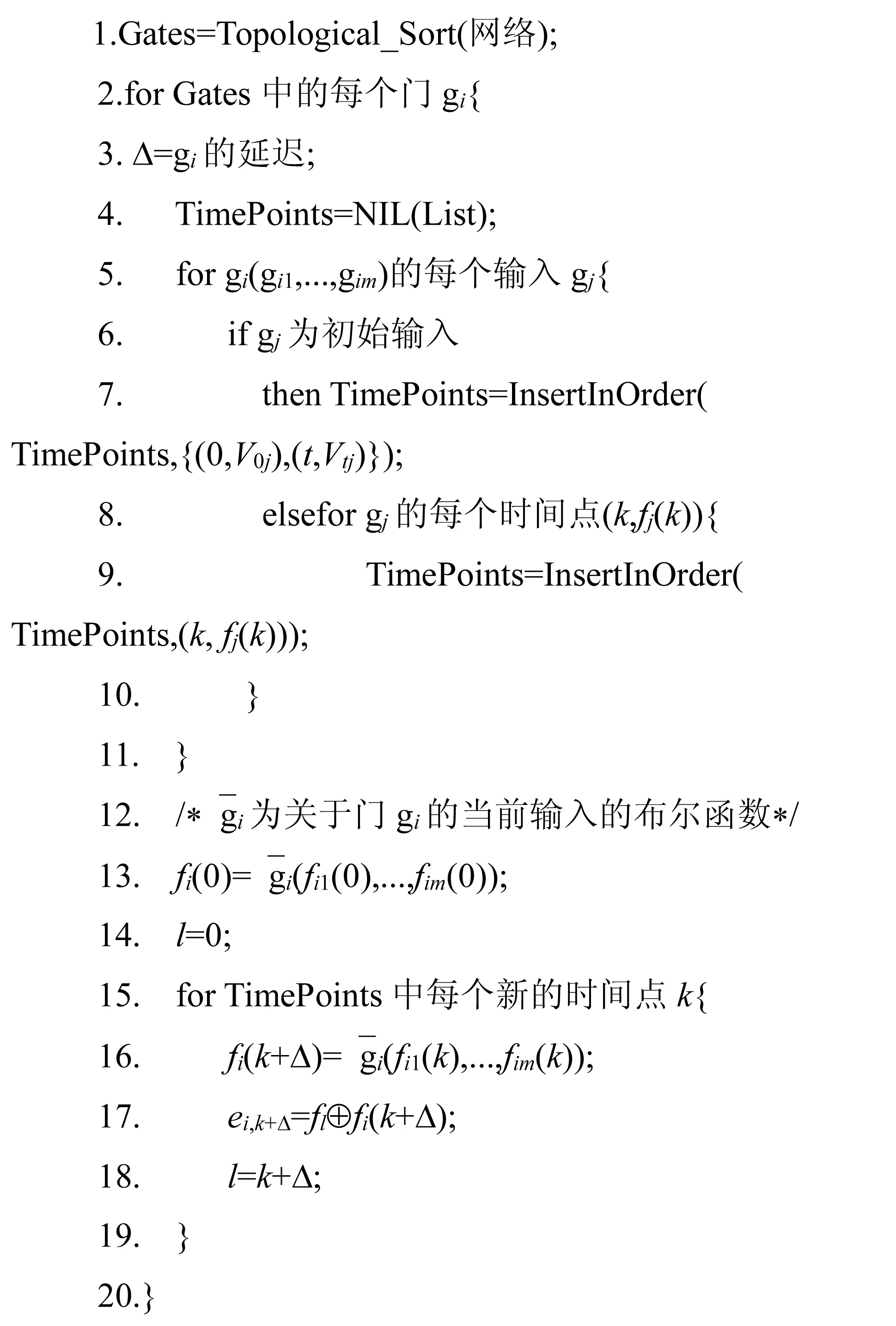

本文提出的基于概率建模方法的功耗估计实现伪代码如图4所示.功耗估计是一次处理一个门,从电路的初级输入到电路的初级输出.对于每个门gi,首先得到其输入的可能转换时间的排序列表,然后得到门的输出的可能转换,同时考虑了从每个输入到门输出的传输延迟.

图4 基于概率建模方法的功耗估计实现伪代码

3 实验结果及分析

3.1 算法仿真实验平台和设置

为了评价本文提出的基于概率建模的功耗估计方法,对于给定的每个门电路,在不同的延迟模型下来比较采用本文提出的方法,获得的电路中全部门相加起来的总的平均功耗估计值和所需执行时间与采用时序逻辑仿真方法获得的平均功耗估计值和所需执行时间.

为了测试本文所提出方法的有效性,我们用C++语言并结合Matlab语言来实现本文所描述的时延分析和功耗估计方法.采用Matlab中一个事件驱动的门级仿真器,该仿真器具有可伸缩的延迟定时模型(基于输出电容和扇出),在仿真初始阶段,引入一个30个周期的预热周期;实验在Pentium IV 2.0 GHz 的PC(512M内存)机和Windows XP操作系统环境下完成.使用来自于ISCAS-89基准套件的12个组合门电路实例进行分析测试,所采用的全部组合门电路参数如表1所示.在表1中,s27~s1238为ISCAS-89系列基准设置,add16是一个16位加法器,max16是一个16位的最大函数器.由于所采用的全部门电路为技术-映射静态CMOS电路,故门的负载电容值是已知的,对于全部电路来说,假设初始输入为0.5的均匀静态概率和0.25的转换概率,采用20 MHz的时钟频率和5 V的电源电压.对于全部门电路,仿真500~1 000个随机生成的输入向量,每个函数ei,j的信号概率收敛到0.1%以内.

表1 实验所用门电路参数

3.2 仿真实验结果

表2所示为在3种延迟模型下,对全部门电路采用本文提出的方法和随机时序逻辑仿真方法得到的门的总的平均功耗(μW)估计值和所需执行时间(s).

表2 实验结果

从表2可见,由于两种方法采用了不同的功耗估计方法,故得到的平均功耗估计值是不同的,显然,本文提出的方法得到的平均功耗估计值更准确,因为在每个可能的转换函数ei,j的信号概率收敛到0.1%以内,对于20 MHz的时钟频率来说,每MHz的平均功耗更低;在零延迟模型中,由于全部门有零延迟,因而它们瞬间切换,故总的平均功耗估计值最低,而且两种方法得到的结果大致接近;在单位延迟模型中,全部门有1个单位的延迟,单位延迟模型考虑了这种误差,但对于全部门来说是一个不变的延迟值,而可变延迟模型对于不同的门来说采用不同的延迟,可变延迟计算是最复杂的,因此这种模型下对于两种方法来说,它们总的平均功耗估计值要高于零延迟模型和单位延迟模型,但这种模型是最符合实际的模型.同时还可得出,本文提出的方法所需执行时间要少于随机时序逻辑仿真方法所需执行时间,因而更高效.这两方面的性能对于超大规模集成电路综合过程中的体系结构设计来说是必不可少的.

4 结论

本文提出了一种估计车辆电子设备组合逻辑电路中的开关平均功耗的方法,基于对开关静态概率和转换概率的计算,从而得到组合逻辑电路的功耗模型.实验结果表明,本文提出的基于概率的功耗估计建模方法可用于大规模的组合逻辑电路,而且在可变延迟模型下还兼顾了内部信号的相关性,相比于传统的随机时序逻辑仿真更准确和更高效.当一个给定的组合电路被嵌入在一个更大的时序电路中时,如果输入到一个门的信号能量持续时间太小,则信号不会迫使门切换,一个输入变化必须保证门切换的最小持续时间称为一个元件的惯性延迟,对于这种具有嵌入式和惯性延迟的传输门组合逻辑电路情况,将是我们下一步研究的重点.