高中频数字收发组件信号同步设计

胡子扬,陈文锋,丁庆东

(中国船舶集团有限公司第八研究院,南京 211153)

0 引 言

随着相控阵雷达技术和硬件水平的不断发展,雷达的数字收发组件向着带宽越来越宽、中频越来越高的方向发展。对于传统的低中频数字收发组件而言,往往有专门的变频模块实现信号的上下混频。此时,对于不同的通道,用于上下混频的本振信号具有相同的频率和相位。这样,信号经过上混频、发射、接收、下混频的过程所带来的相位变化可以相互抵消,也即在信号的发射和接收的过程中无需额外考虑信号因混频带来的相位变化。

数字组件采用高中频意味着从基带信号到中频信号之间要经过一级数字NCO进行DUC或者DDC。不同组件甚至通道之间的数字NCO的产生都是独立的。如果不对数字NCO进行同步设计,往往会导致收发组件间相位不同步,抑或无法实现相参积累。[1]

本文通过对数字NCO的原理和带来的相位影响进行分析,在基于硬件的基础上进行同步设计,以实现高中频数字收发组件信号的同步。

1 数字NCO混频原理简介

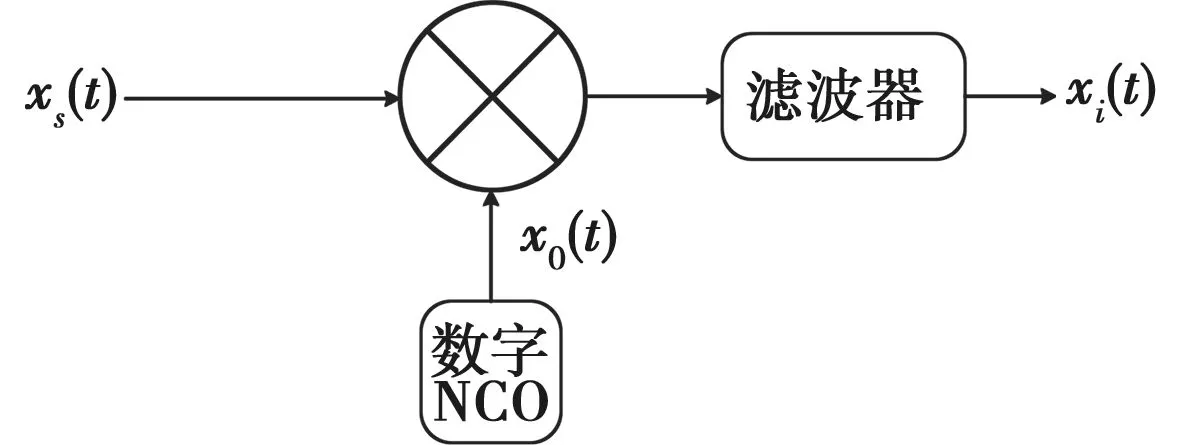

图1所示为数字NCO混频原理框图。假设xs(t)=cos (2πft+θ),其中f为信号频率,θ为信号初相。x0(t)=cos (2πf0t+φ),其中f0为本振频率,φ为本振初相。

图1 数字NCO混频原理框图

则信号经过数字NCO混频后,得到

xi(t)=cos(2πft+θ)cos(2πf0t+φ)

=cos[2π(f+f0)t+(θ+φ)]+

cos [2π(f-f0)t+(θ-φ)]

(1)

假设此过程为下混频,经过滤波后得到信号

xi(t)=cos [2π(f-f0)t+(θ-φ)]

(2)

若为上混频,则经过滤波后得到信号

xi(t)=cos [2π(f+f0)t+(θ+φ)]

(3)

可得到混频后的信号频率为f-f0,初相为θ-φ。可见,经过数字NCO混频后信号的频率和相位均发生了改变。

2 相控阵雷达对数字组件上下混频的要求

对于相控阵雷达来说,基带信号经过上混频后放大成电磁波发射出去,经物体反射回来后再经下混频变为接收基带信号进行处理,忽略模拟混频带来的影响。

假设上行基带信号为xs(t)=cos (2πft+θ),信号是以脉冲形式产生的,其中θ为脉冲起始时刻基带信号的初相。上行数字NCO产生的本振信号为x0(t)=cos [2πf0t+φ0(t)]。本振信号是连续产生的,其中φ0(t)为脉冲起始时刻本振信号的初相,为时间t的一次函数,斜率与频率f0有关。通过上变频后得到的信号:

文中涉及的记号与术语可参见[1,10-11]。若X是拓扑空间,F⊆X,F在X中的闭包记为clF,在涉及多个空间时,为区分起见也记作clXF。空间X的全体开集与全体闭集分别记为Ο(x)与Γ(x)。

xu(t)=cos {2π(f+f0)t+[θ+φ0(t)]}

(4)

相控阵雷达要求产生同频同相的信号进行移相后再进行空间波束合成。由于每个基带的信号xs(t)完全相同,因此每个通道的数字NCO产生的本振信号x0(t)也必须完全相同。

上行信号发射出去后,经过空间传播、反射,再接收回来后的信号在脉冲起始时刻初相不变,即

xd(t)=xu(t)=cos {2π(f-f0)t+[θ-φ0(t)]}

(5)

假设下行数字NCO产生的本振信号为x1(t)=cos [2πf1t+φ1(t)],下行本振信号同样为连续的,其中φ1(t)为脉冲起始时刻下行本振信号的初相,其为时间t的一次函数,斜率与频率f1有关。通过下混频后得到的信号:

xy(t)=xd(t)x1(t)

=cos {2π(f+f0-f1)t+[θ+φ0(t)-φ1(t)]}

(6)

为了实现脉冲相干积累,要求信号xy(t)的相位θ+φ0(t)-φ1(t)是一个常数,即φ0(t)-φ1(t)是一个常数。由于φ0(t)是f0的一次函数,φ1(t)是f1的一次函数,故要求f0=f1,或者当f0≠f1时在脉冲起始时刻φ0(t)=φ1(t),即每个脉冲周期之前都要复位一次上下行数字NCO的相位。

3 高中频数字收发组件同步设计

在第2节中可以看到,高中频数字收发组件分为两种情况,一种为相同的混频信号频率,一种为不同的混频信号频率。这两种情况在实际应用中都会遇到,前一种多为FPGA内部使用数字NCO进行上下混频,后一种多为使用AD、DA器件内部数字NCO进行上下混频。[3]

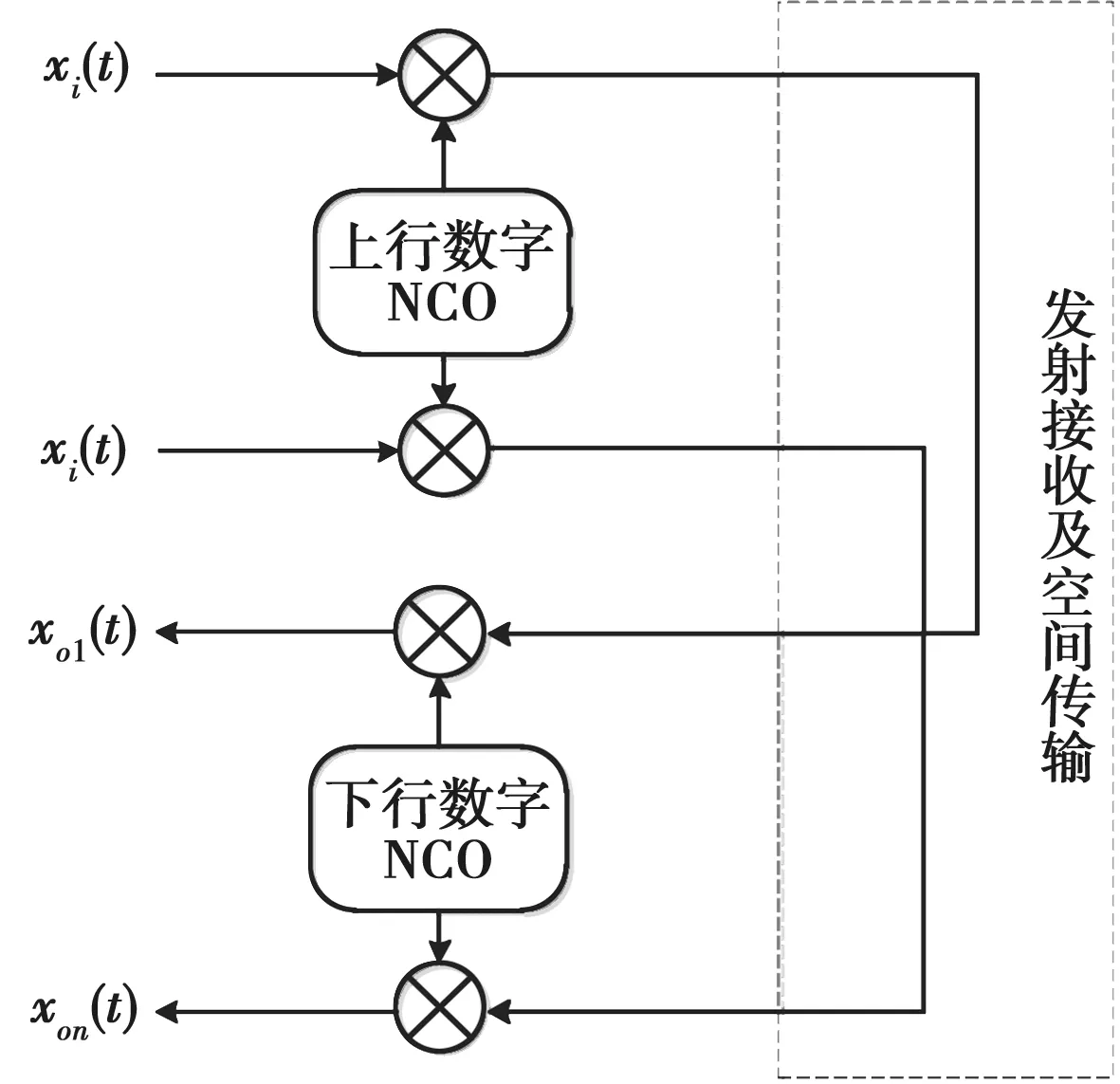

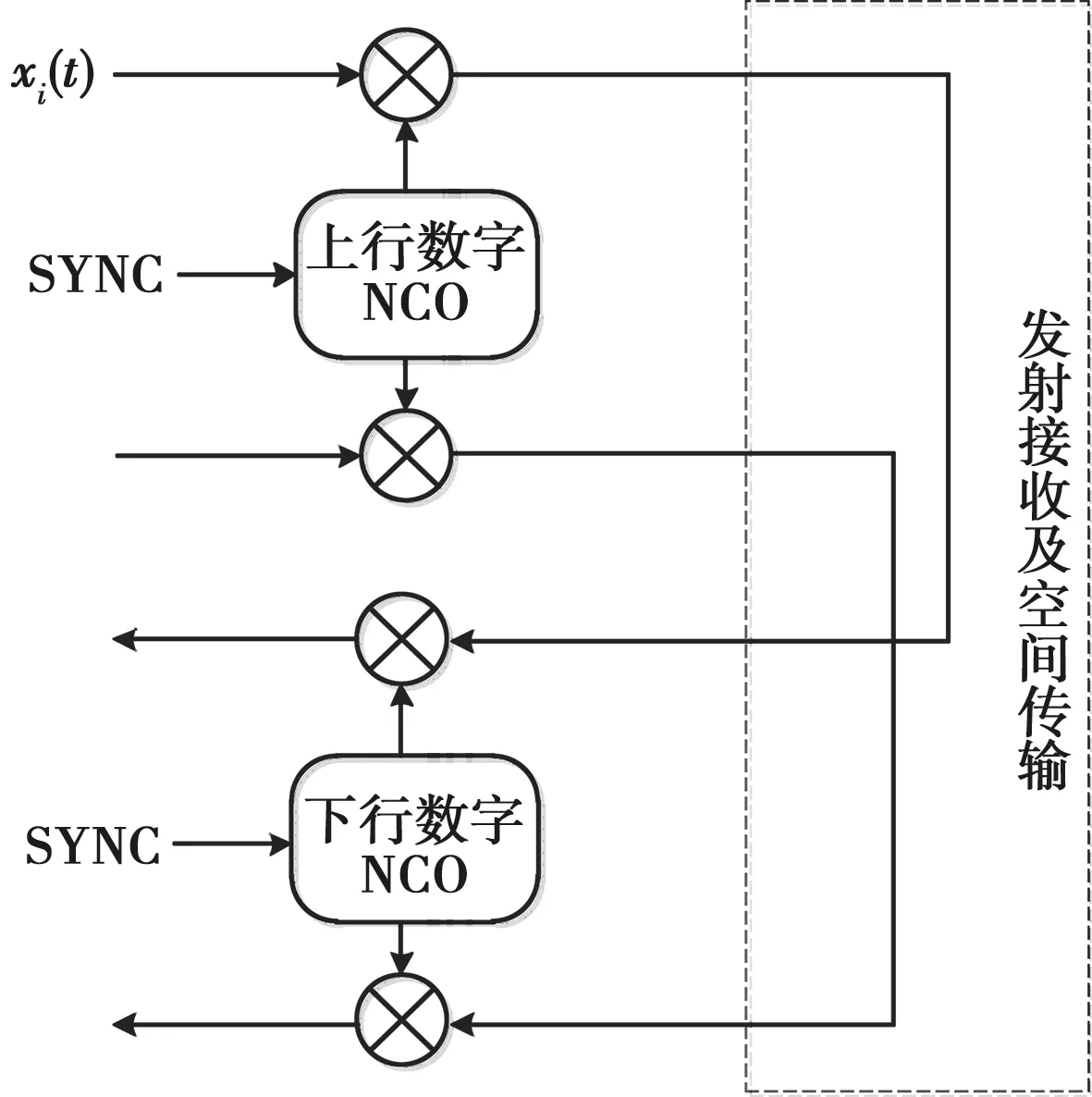

图2 同频本振系统设计框图

对于不同的混频信号频率,必须保证在脉冲之前复位上下行数字NCO,以使得脉冲起始时刻不同通道上下行数字NCO的初始相位在每个周期中保持相同,即可实现通道信号同步并可实现脉冲相参积累。其实现系统框图如图3所示。

图3 不同频本振系统设计框图

图3中,SYNC为用于NCO同步的触发信号,每周期一次。在利用AD、DA内部数字NCO进行上下变频的情况,需根据具体硬件情况设计同步方式,例如AD9680利用SYSREF信号同步,AD9154利用Data Key实现NCO同步等。[3]

4 系统仿真结果

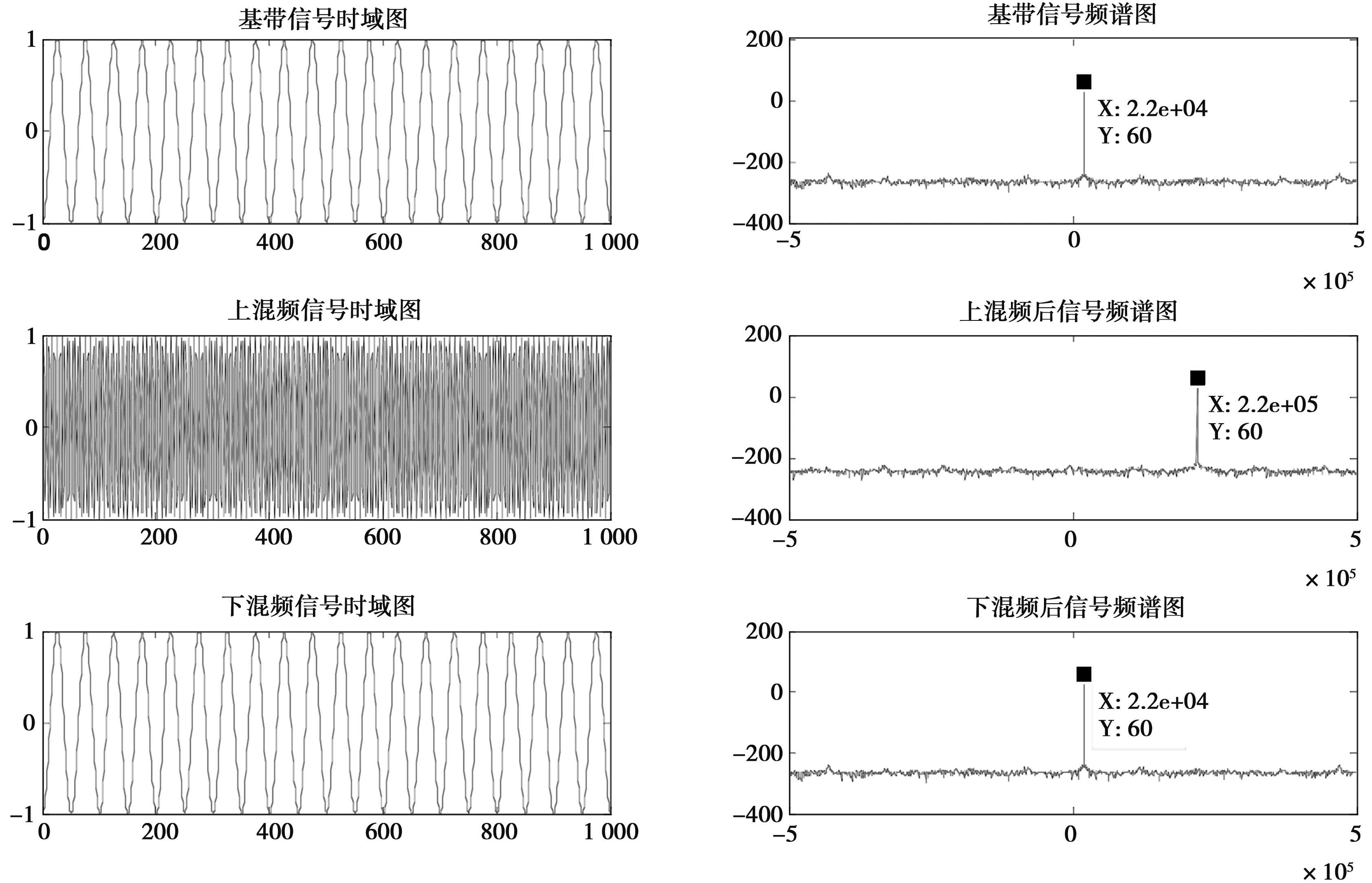

首先仿真同频连续本振信号。仿真中,设定系统采样率为1 MHz,基带信号为20 kHz,本振频率为200 kHz。为了方便显示结果,基带信号和本振信号均为复信号。[3]可以看到,基带信号经过上混频和下混频后频率变化如图4所示。

图4 同频连续本振混频仿真图

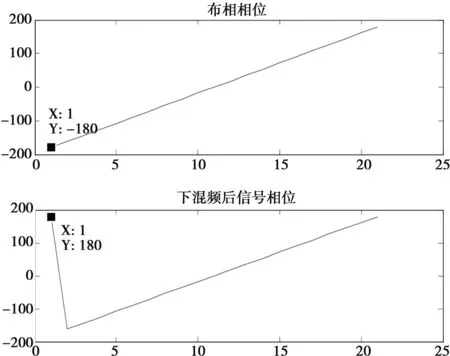

在该信号基础上,对多个通道信号进行上行布相,即在信号上混频后对21个上行通道进行布相,可以得到如图5所示结果。

仿真不同频本振信号。仿真中,设定系统采样率为1 MHz,基带信号为20 kHz,上混频本振频率为200 kHz,下混频本振频率为150 kHz。每个脉冲起始本振初相复位为0。为了方便显示结果,基带信号和本振信号均为复信号。可以看到,基带信号经过上混频和下混频后频率变化如图6所示。

图5 同频连续本振系统布相后相位结果

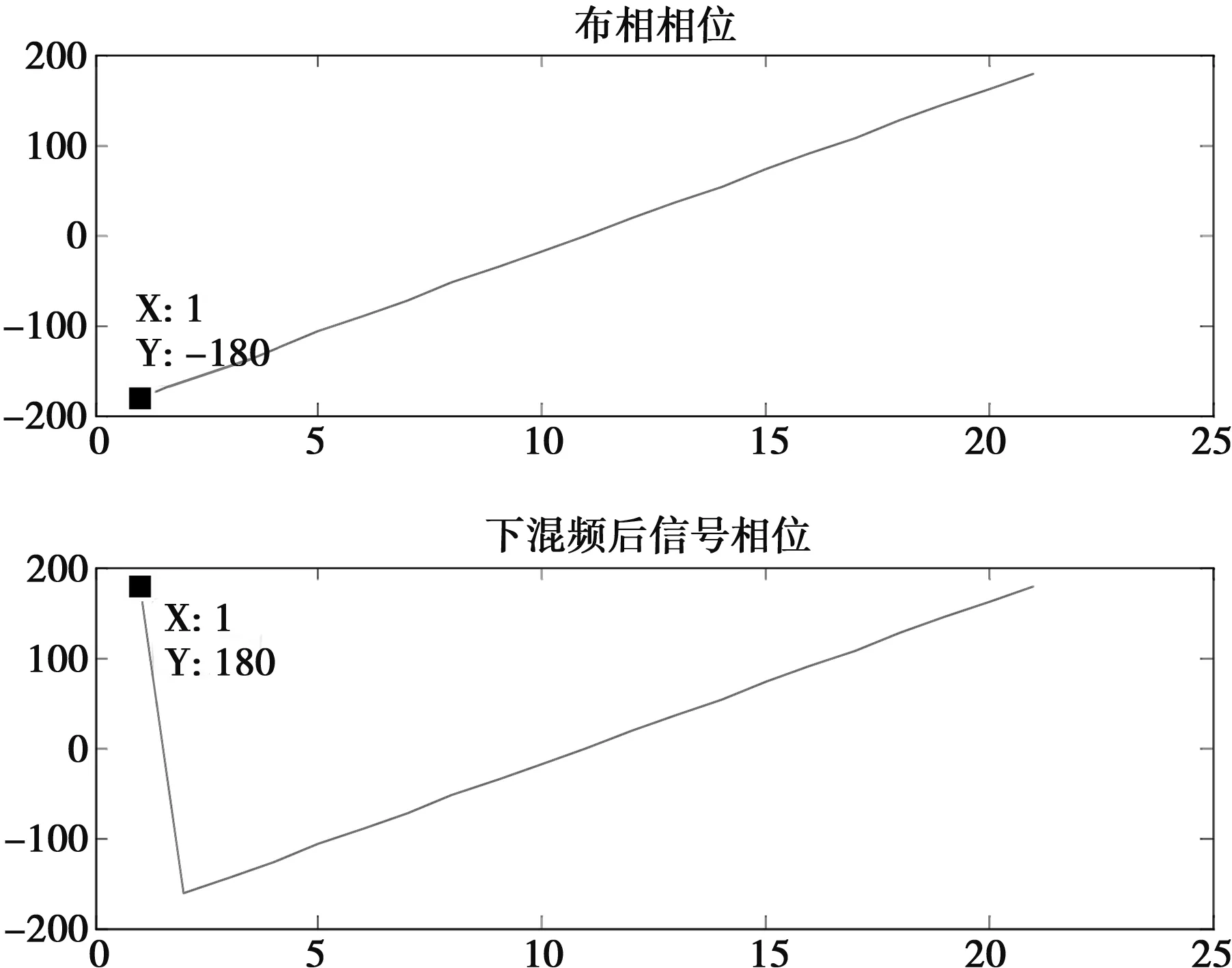

在该信号基础上对多个通道信号进行上行布相,即在信号上混频后对21个上行通道进行布相,可以得到如图7所示结果。

图7 不同频本振系统布相后相位结果

5 结束语

本文通过理论分析和仿真结果得出了高中频数字收发组件信号同步设计的基本要求:对于同频本振系统来说,要求:(1)所有通道上行数字NCO初相相同;(2)所有通道下行数字NCO初相相同。对于不同频本振系统来说要求:(1)所有通道上行数字NCO初相相同;(2)所有通道下行数字NCO初相相同;(3)每个周期对上下行数字NCO初相进行复位。

本文的结论不仅具有仿真验证结果,同时在硬件电路上进行了验证。验证结果表明,本文结论对于实现高中频数字收发组件信号同步具有实用意义。