基于VHDL的交通灯控制器的程序设计

余丽红,龙诺春,林春景,柳贵东

(广东白云学院 电气与信息工程学院,广东 广州 510450)

0 引言

超高速集成电路硬件描述语言(Very-High-Speed Integrated Circuit Hardware Description Language,VHDL)是电子产品设计的三大语言之一,其语法非常严格,是我国电子设计自动化硬件描述语言的国家统一标准[1]。VHDL的程序结构特点是将设计实体包括元件、电路模块或电路系统分成外部端口和内部实体。VHDL用简单的源代码来描述复杂的内部电路结构,采用分层设计、顶层统一的描述方法。在完成外部端口的定义和内部实体的开发后,就可以生成能被其他系统设计反复利用的模块,供电路设计人员共享,避免重复设计,提高设计效率。

1 VHDL模块化的设计方法

VHDL模块化的设计方法是借助库。库一般分为IEEE、WORK、STD、ASIC和用户自定库5种。库被用来存放预先编译好的程序代码数据,包括程序包集合定义、配置定义、实体定义和结构体定义。库的优势在于方便设计者共用已经编译通过的设计成果。设计者在设计电子产品的过程中,首先要明确电子系统的整体功能,并将大的功能模块划分为小的功能模块,功能模块进一步细分为功能子模块。子模块的设计用一个VHDL程序实现。VHDL自顶向下[2]的硬件模块化设计流程如图1所示。

图1 VHDL模块化设计流程

2 交通灯控制器的设计

2.1 设计思路

交通灯控制器综合了组合电路与时序电路,主要用来模拟交通路口红黄绿灯变化和倒计时的过程。交通控制器主要包括:时钟分频、红黄绿状态转换、红黄绿状态译码、倒计时显示译码模块。设计过程中所用实验设备的初始时钟为20 MHz。利用分频模块将20 MHz的频率转换为1 Hz,对应时间为1 s。分频模块是通过计数器来实现,红黄绿状态转换模块用于控制交通灯的状态依次为红、黄、绿,重复循环,并控制3种状态的倒计时时间。显示译码模块可以显示交通灯的状态和时间。状态译码将3种状态译为段码和位码,其中,段码用于显示3种状态倒计时的时间,位码用于控制相应数码管的亮灭。显示模块需要用3个LED灯和两个数码管,利用动态扫描原理来完成两个数码管的显示。每个时钟周期内扫描一个数码管,显示一位数据,显示的数据值由段码来控制,由于人眼的视觉暂留现象,只要时钟扫描>100 Hz,人眼观测到的所有数码管就是同时显示的[3]。系统设计的模块框图如图2所示。

图2 系统设计的模块框

2.2 系统的VHDL语言描述

完整的VHDL程序一般包括5个部分:库、程序包、配置、结构体和实体。库专门用于存储预先编译完成的实体、结构体、程序包集合和配置。程序包用于存放各设计模能够共享的常数、数据类型、子程序等基础设计单元。配置用于把特定的结构体关联到一个确定的实体上,为一个大型系统的设计提供管理和工程组织[4]。实体用于参数定义和描述模块的外部端口。结构体是VHDL程序的主体部分,用于描述模块的具体行为、结构和功能。

2.2.1 时钟分频模块

根据设计要求,分频模块的外部端口共有4个:初始时钟输入端口、复位控制输入端口、122 Hz的动态扫描脉冲输出端口以及1 Hz的计时脉冲输出端口。分频模块实体的VHDL语言描述如下:

ENTITY SZFP IS

PORT(CLK,RST: IN STD_LOGIC;

CT1,CT2: OUT STD_LOGIC);

END SZFP;

端口说明语句中,CLK是输入端口,表示初始时钟信号;RST是输入端口,代表复位信号;CT1、CT2为输出端口,表示分频以后的时钟信号,分别为1 Hz,100 Hz。

2.2.2 状态转换模块

状态转换模块的外部端口共有5个:1 Hz计时脉冲输入端口、复位控制输入端口、红黄绿状态输出端口、个位数据输出端口和十位数据输出端口。该模块实体的VHDL语言描述如下:

ENTITY ZTZH IS

PORT(CLK,RST: IN STD_LOGIC;

STATE: OUT STD_LOGIC_VECTOR(2 DOWNTO 0)

DL,DH:OUT STD_LOGIC_VECTOR(3 DOWNTO 0));

END ZTZH;

其中,STATE表示状态输出信号;DL,DH代表输出的倒计时数据。

2.2.3 状态译码模块

状态译码模块的外部端口共有两个:红黄绿状态输入端口和LED灯控制输出端口。该模块实体的VHDL语言描述如下:

ENTITY ZTYM IS

PORT(STATE: IN STD_LOGIC_VECTOR(2 DOWNTO 0)

LIGHT: OUT STD_LOGIC_VECTOR(2 DOWNTO 0));

END ZTYM;

2.2.4 显示译码模块

显示译码模块的外部端口共有6个:122 Hz动态扫描脉冲输入端口、复位控制输入端口、十位数据输入端口、个位数据输入端口、控制数值的段码和选择芯片的位码。该模块实体的VHDL语言描述如下:

ENTITY XSYM IS

PORT(CLK,RST:IN STD_LOGIC;

DL,DH:IN STD_LOGIC_VECTOR(3 DOWNTO 0);

DT:OUT STD_LOGIC_VECTOR(6 DOWNTO 0);

EN:OUT STD_LOGIC_VECTOR(1 DOWNTO 0));

END XSYM;

2.2.5 顶层系统模块

顶层系统模块将时钟分频、计数器状态转换、译码、显示4个分模块整合在一起。在VHDL程序中利用元件例化语句来建立顶层模块与子模块之间的连接关系。元件例化语句由元件声明语句和元件例化语句[5]两部分组成。元件声明(component)是对顶层要调用的较低层次的实体进行端口说明,相当于完成底层元件的封装。元件例化(port map)是在调用较低层次的实体时建立起端口之间的一一对应关系。设计最终借助元件例化实现交通灯控制器的功能。顶层模块设计实体共有5个端口:20 MHz初始时钟输入、复位控制输入、LED灯控制输出端口,段码输出和位码输出,相对应的VHDL语言描述如下:

ENTITY JTD IS

PORT(CLK,RST:IN STD_LOGIC;

DT:OUT STD_LOGIC_VECTOR(6 DOWNTO 0);

LIGHT: OUT STD_LOGIC_VECTOR(2 DOWNTO 0));

EN:OUT STD_LOGIC_VECTOR(1 DOWNTO 0));

END JTD;

元件例化语句如下:

U0:SZFP PORT MAP(CLK,RST,CT1,CT2);

U1:ZTZH PORT MAP(CT1,RST,STATE,DL,DH);

U2:ZTYM PORT MAP(STATE,LIGHT);

U3:XSYM PORT MAP(CT2,RST,DL,DH,DT,EN);

其中,DL、DH、CT1、CT2为内部信号。

3 交通灯控制器的硬件实现

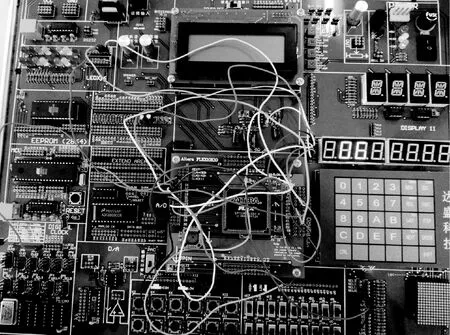

交通灯控制器的硬件实现选用Altera公司的MAX+PLUSⅡ软件。硬件实现之前先完成4个模块的时序仿真,接下来完成顶层模块的时序仿真,然后在目标芯片上进行管脚分配,连接好对应引脚后就可以进行程序下载和硬件实现。本设计的硬件实现如图3所示。

图3 交通灯控制器

4 结语

VHDL语言对于初学者来讲是比较难掌握的,文章根据多年的教学经验设计交通灯控制器的程序,用以帮助学生掌握自上而下的模块化程序设计思想,让学生对VHDL语言中的顺序语句、并行语句(特别是进程语句)有更深刻的理解。