高速线缆组件插入损耗优化技术研究*

(中航光电科技股份有限公司,河南 洛阳 471000)

0 引言

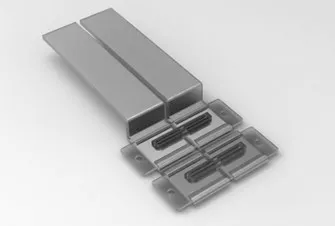

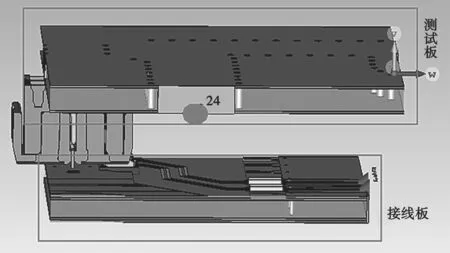

高速线缆组件是一种低沉本、短距离的高速互联解决方案,广泛应用于通信设备、计算机及其周边、医疗设备、航天军工、消费电子及汽车等领域[1]。高速线缆组件一般包含2 套连接器、多路线缆[2]、多处端接及接线PCB 等,如图1 所示。链路中各个部分给组件带来的损耗,已成为制约线缆组件传输速率提升的瓶颈。目前,各大应用领域对高速线缆组件的传输速率提出了更高的要求,因此优化链路中各部分的插入损耗成为高速线缆组件设计及优化的关键环节[3]。

张华[4]等采用仿真方法对高速连接器及背板系统的信号完整性进行了研究,分析了影响信号完整性的关键因素,并针对研究的结构提出了优化方案,可指导高速链路的设计。但是,上述研究未对线缆组件的端接部位、接线PCB 等影响信号完整性的关键因素进行深入分析。

图1 一种线缆结构

本次研究对影响线缆组件插入损耗的关键因素进行分析,借助仿真软件,对比了不同结构参数时线缆组件的高速性能。根据对比确定了线缆组件的优化方法,并进行了实物验证。优化后的线缆组件插入损耗降低,高速性能提升显著,且形成的优化方法可用于其他高速线缆组件的设计。

1 链路损耗的主要影响因素

1.1 插入损耗

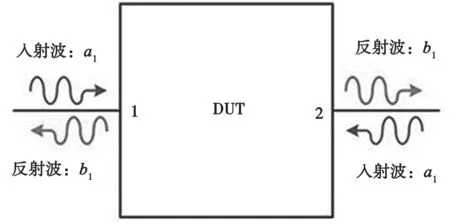

插入损耗通常是指系统传输的信号从信道的端口1 传输到端口2 时发生的能量损失,如图2 所示。

图2 常见的二端口网络

插入损耗可由输入信号和输出信号的电压幅度表示,数学模型为:

式中,IL为插入损耗,V代表电压幅度值,P为功率值。实际链路中,插入损耗通常和介质损耗、导体损耗、耦合到临近线和对外辐射、阻抗不连续4 个因素密切相关,其中介质损耗和导体损耗是链路插入损耗的主体部分。

1.1.1 介质损耗

当导体上施加电压时,在电场的作用下,原本排列杂乱无章的电偶极子会趋于整齐,与电场的方向一致。电偶极子的负端向施加电压的正端移动,不断消耗能量而产生介质损耗。通常用介质耗散因子描述电偶极子造成的影响,即:

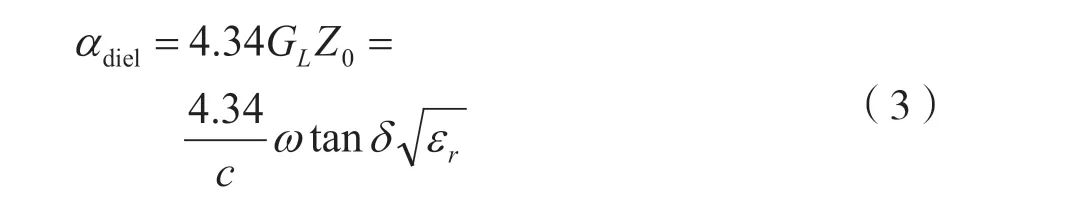

式中:tanδ表示介质损耗因子;n表示介质中电偶极子的密度;P表示偶极矩,是对电荷和偶极子间距离的度量;θmax表示电场中偶极子摆动幅度。介质损耗主要和材料的固有性能、信号频率以及传输线长度有关。介质损耗引起的单位长度衰减为:

式中,αdiel表示介质损耗引起的单位长度衰减;GL表示单位长度电导;ω表示信号的角频率;tanδ表示材料的介质损耗因子;Z0表示导体的特性阻抗;εr表示相对介电常数,无量纲;c表示真空中的光速。

1.1.2 导体损耗

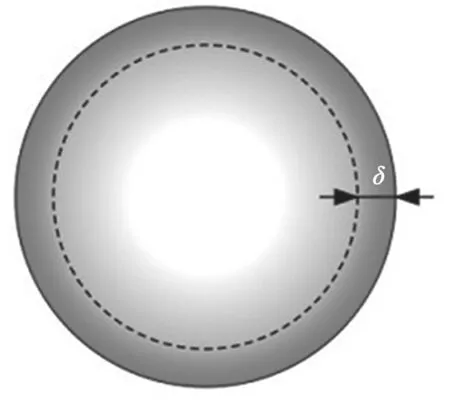

在高速传输领域,导体损耗主要与趋肤效应和导体表面粗糙度有关。高频电流流过导体时,导线电阻在交流情况下处于一种频变状态。随着频率的升高,电流集中在导体表面传输,导致阻抗升高,导体损耗增加。高频时,铜的趋肤深度如图3 所示。

图3 趋肤深度

它的计算公式如下:

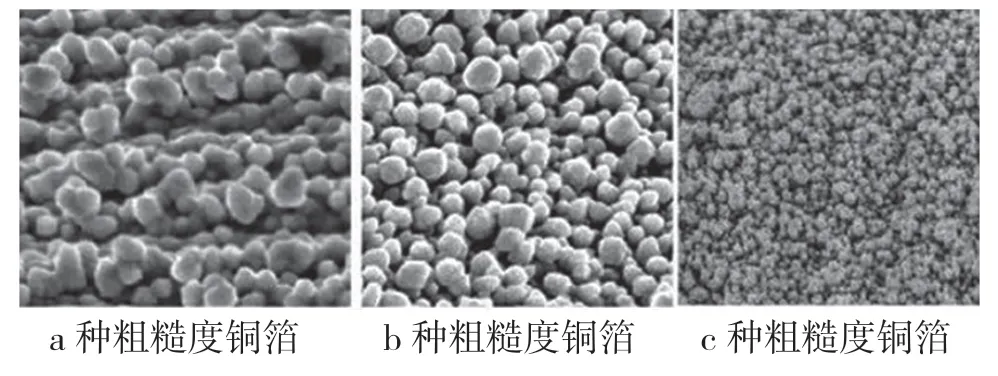

式中:δ为穿透深度;ω为角频率,ω=2πf,f为磁场频率;μ为磁导率;ρ为电阻率;σ为电导率。此外,不同粗糙度的铜箔表面会产生不同的寄生电感,导致铜箔表面的阻抗一致性变差。表面粗糙度大的铜箔,阻抗失配也更加严重,会引入更多的导体损耗。图4 为3 种铜箔的导体损耗,其中a 种>b 种>c 种。

图4 不同粗糙度的铜箔

导体的单位长度损耗可表示为:

式中:αcond表示由导体引起的单位长度衰减,单位为dB;RL表示单位长度导体的串联电阻;Z0表示导体的特性阻抗。

1.1.3 耦合到临近线和对外辐射

在多导体系统中,导体间通过电场和磁场发生耦合。两条走线相距较近时,会在临近的走线上引起噪声,把信号一部分的能量传递到临近的导体上,会部分损失自身能量而产生损耗。

1.1.4 阻抗不连续

信号以电磁波的形式在走线中向前传播。当互连线中出现阻抗突变时,在两个阻抗不同区域的分界面上会发生反射,能量会被反射回源端,导致传输到末端的信号幅度减小而产生衰减。

1.2 高速线缆损耗

实际应用中,高速线缆组件的损耗主要有3 个部分组成。

1.2.1 线缆的损耗

线缆是高速线缆组件的主体部分。通常情况下,线缆的损耗与导体线径、材料以及绝缘层的介质损耗因子等相关。随着频率的增加,线缆的损耗逐渐增大,在线缆组件整体的损耗中占据主体部分,如图5 所示。

1.2.2 连接器、接线PCB 及测试PCB 带来的损耗

高速线缆组件的核心元器件是连接器和接线PCB。连接器损耗主要与自身结构和选用的绝缘体材料有关。接线PCB 是连接高速连接器和高速线缆的过渡元件,如图6 所示。它的损耗与板材、走线形式及长度、有无过孔等因素相关。

图5 不同频率下的线缆损耗

图6 接线PCB

1.2.3 端接部位焊接及线缆剥线等工艺控制引入的损耗

连接器和接线PCB 端接部位焊接一致性、焊锡量、焊接和剥线长度的一致性等,直接影响了线缆组件的损耗。端接部位焊接一致性和焊锡量与钢网结构参数相关。焊接位置如图7 所示。

图7 焊接位置

2 高速线缆组件的设计优化

针对高速线缆组件类产品插入损耗的主要来源,从以下3 个方面进行仿真与优化。

2.1 线缆的优化与选择

对不同规格的线缆进行仿真,结果如图8 所示。性能更好的线缆可显著降低插入损耗,应用中应根据线缆组件支持的传输速率选择合适的线缆。

在线缆本身的测评及选用时,除了直接关注线缆自身插入损耗指标时,一些如阻抗、时延差等和插入损耗相关联的指标也需要进行评估。各项指标均选用最优时,组件的插入损耗才能达到最小。

2.1.1 线缆阻抗

高速线缆的阻抗和4 个直接因素相关[5],分别是介质的介电常数、内导体外径、外导体内径及两内导体的中心距离。在选择线缆阻抗时,可根据以上几点因素折衷考虑。

本次高速线缆组件设计的目标阻抗是85 Ω。由图9 可以看出,选用的线缆阻抗值处于86.49~88.04 Ω,上下浮动不足3 Ω,满足了高速线缆阻抗一致性的要求。

图8 不同线缆的插损差异

图9 高速线缆的阻抗测试曲线

2.1.2 传输时延差

传输时延差是指不同线缆之间的传输时延的差值。传输时延与信号路径长度和传播速度直接相关。传播速度可表示为:

式中:ε0表示自由空间的介电常数;εr表示材料的相对介电常数;μ0表示自由空间的磁导率;μr表示材料的相对磁导率。

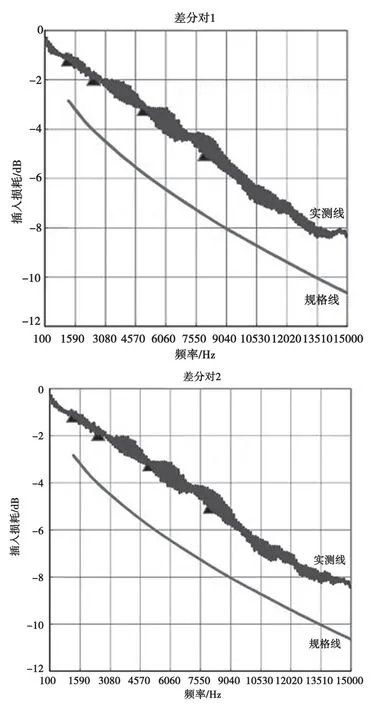

当两信号线有时延差产生时,除了控制线缆的长度外,可以依据式(6)中涉及的影响因素,考虑更换不同介电常数的材料来进行补偿。综合考虑以上参数,对选用的线缆进行时延差测试,结果如图10 所示,1 m 长线缆的时延差值在2 ps 以内。

图10 差分对1 和差分对2 时延差测试结果

2.2 接线PCB 及测试PCB 的优化

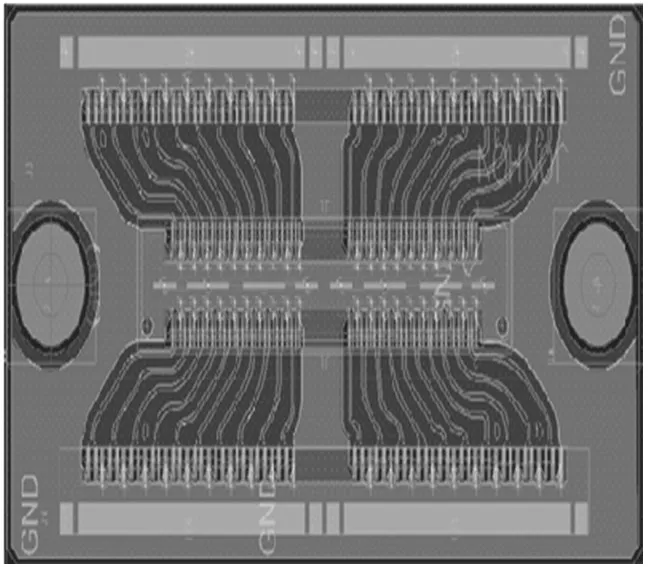

2.2.1 接线PCB 的仿真优化

本次研究的线缆组件PCB 采用过孔换层的形式实现双面出线,通过仿真对比了差分走线上是否存在过孔时的损耗大小。接线PCB 如图11 所示,左侧两路差分无过孔,右侧两路差分有过孔。对以上4 路差分进行仿真,损耗对比如图12 所示。

图11 左侧无过孔,右侧有过孔

由图12 可知,接线PCB 去掉过孔后,插入损耗衰减幅度明显降低。应用中,可采用线缆绕线方式去除过孔,降低线缆组件的插入损耗。

2.2.2 测试PCB 的优化

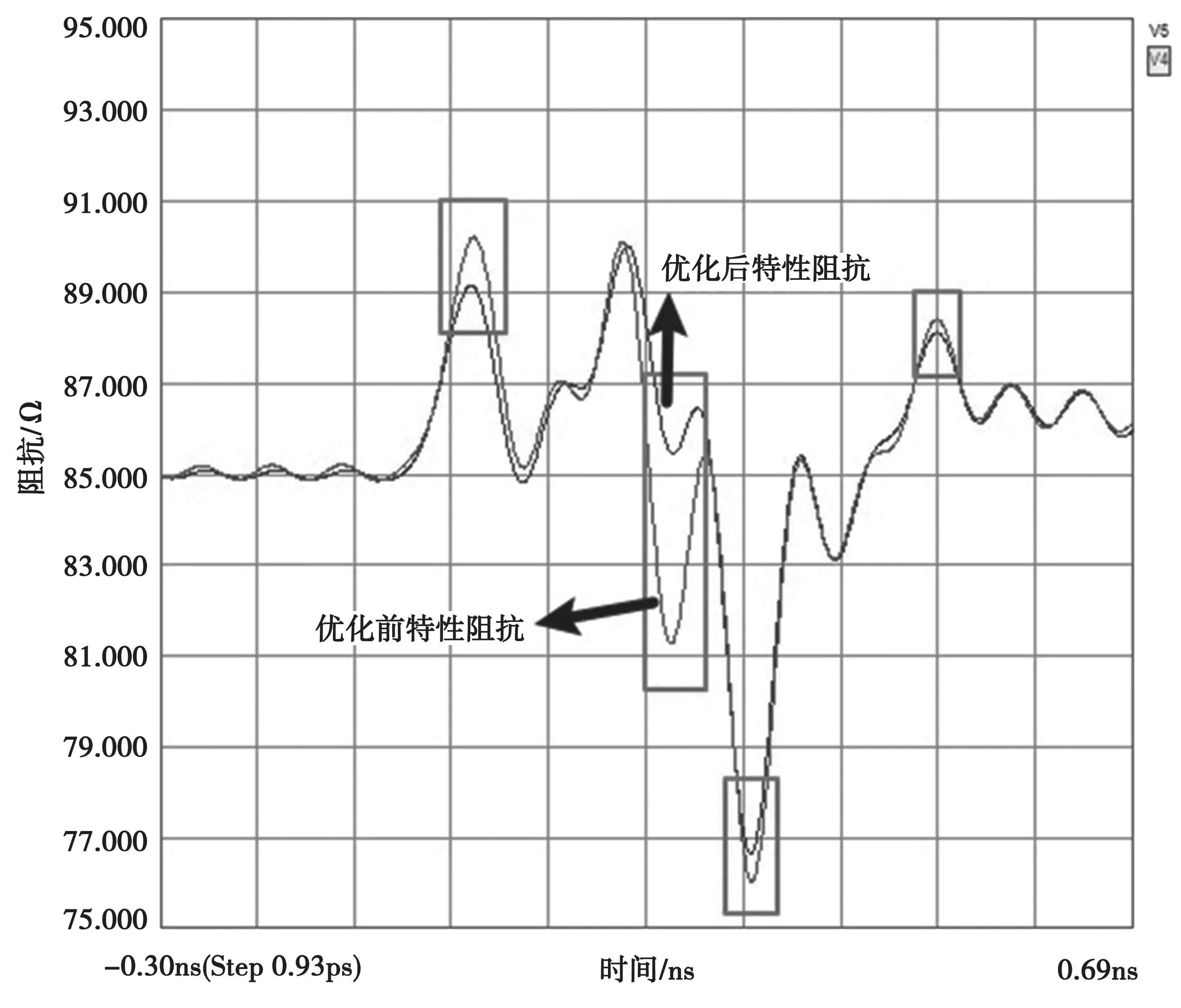

通过仿真和测试对比不同大小焊盘和反焊盘尺寸的测试板对线缆组件测试结果的影响,结果如图13 和图14 所示。

由图14 可知,反焊盘增大、焊盘减小后,测试板焊点处的阻抗提升了约6 Ω,整体的阻抗波动性变小,线缆组件测试出来的插入损耗更加平滑,谐振及幅值均相应减小。因此,增大测试板的反焊盘,同时减小焊盘、优化走线形式,可显著提升测试板性能,进而优化线缆组件在测试中的插入损耗。

图12 有无过孔插损对比

图13 优化的测试板仿真模型

图14 特性阻抗对比

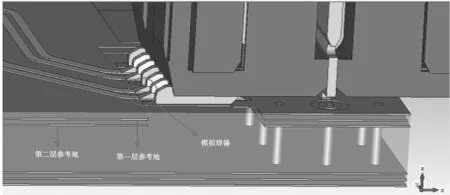

为进一步降低阻抗的波动,在第二层参考地上再新增一层反焊盘,模型如图15 所示。新增反焊盘前后的对比结果如图16所示。新增一层反焊盘后,在原来优化的基础上阻抗波动更小,相应的插入损耗也变小,进而可实现线缆组件的优化。

2.3 焊接及剥线等工艺控制

焊接部位焊锡堆积过多,易造成焊点处阻抗值偏低。产品焊锡量的多少和钢网尺寸紧密相关,因此对钢网的结构参数进行了优化。

(1)将钢网厚度由1.3 mm 更改为1.0 mm,显著减小了涂覆到焊盘上的锡量;

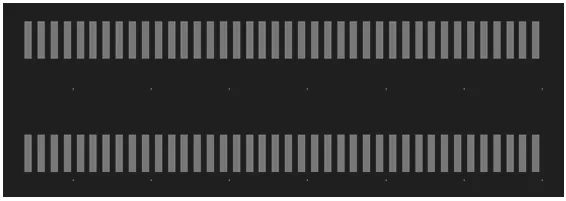

(2)在保证焊接可靠性的前提下,减小钢网上各个pin 脚的大小也能减小焊脚处锡量,提升焊点阻抗,进而减小损耗。钢网上pin 脚大小如图17所示。

图15 测试PCB 模型

图16 特性阻抗对比

图17 PASTEMASK 层pin 脚大小

剥线长度不一致会造成Skew 较差和阻抗失配而引入插损谐振[6]。因此,在新产品的改进过程中,采用激光剥线技术,严格保证剥线长度和剥线质量。此外,焊线及连接器表贴也采用机器焊接,提升焊点一致性[7],避免手工焊接带来的偏差。

3 产品测试验证

优化后产品如图18 所示。

图18 线缆实物

测试夹具规格如下:

(1)测试印制板由高速板材TU883 制成,板厚1.6 mm;

(2)采用2.92 mm 射频同轴连接器;

(3)测试夹具走线长度16 mm。

优化后的插入损耗测试,结果如图19 所示。0.55 m 长线缆组件的插入损耗在8 GHz 以前均大于-5 dB,较优通路可以达到-4 dB 以内,线缆组件损耗优化显著,达到了设计要求。

图19 新版线缆的IL 测试结果

线缆组件折弯180°的插入损耗压力测试。折弯前后插入损耗测试结果如下:差分对1 在8 GHz 时,折弯前损耗为-4.58 dB,折弯后损耗为-4.67 dB;差分对2 在8 GHz 时,折弯前损耗为-4.24 dB,折弯后损耗为-4.43 dB;差分对3 在8 GHz 时,折弯前损耗为-4.03 dB,折弯后损耗为-4.17 dB。综上,折弯前后,3 个通道在8 GHz 时的损耗的变化量均小于0.2 dB。由此可见,折弯180°使用时,线缆组件的插入损耗无明显恶化,在该应用场景下仍可正常使用。

4 结语

对影响高速线缆组件插入损耗的关键因素进行分析,采用仿真方法对实际应用中的线缆组件进行优化,结合实物测试验证了优化方法的可靠性,可得出以下结论:

(1)接线PCB 由双面走线变为单面走线,去除换层用的过孔,可提升插入损耗1 dB 左右;

(2)增大测试板的反焊盘,同时减小焊盘、优化走线形式,可显著提升测试板性能,焊点处阻抗低点提升约6 Ω,阻抗一致性提高,组件的插入损耗测试结果更加平滑;

(3)采用性能更好的线缆,可显著降低组件的插入损耗,应用中应根据线缆组件的传输速率选择合适的线缆;

(4)加强端接处的阻抗控制,即可通过优化钢网的结构尺寸由1.3 mm 变为1 mm,有效提升阻抗一致性,进而降低损耗。