典型模拟电路性能退化仿真技术研究

聂国健, 于 迪, 常玉春, 刘 岩, 杨 云, 李欣荣

(1.工业和信息化部电子第五研究所 可靠性数据中心, 广州510610; 2.大连理工大学 微电子学院, 辽宁 大连116000)

0 引 言

随着器件工艺进入深亚微米时代, 电路集成度不断增高, 使器件内部的电场和电流密度增加, 电路可靠性问题变得越来越重要。 可靠性问题不仅会对电路的性能造成影响, 而且也会严重影响工艺技术的缩减[1], 为此, 基于可靠性的性能退化研究工作势在必行。 结合电路研制周期、 成本及复杂的使用环境等多重因素影响, 虚拟验证成为验证发展的必然。 因此, 设计出切合实际的可靠性虚拟仿真是当前电路验证的挑战之一。

近年来, 国外Cadence、 Synopsys 和Mentor 公司联合推出的UVM(Universal Verification Methoclology)验证方法学, 是基于System Verilog 验证语言建立的一套新一代的功能验证方法学, 在许多国外IC 设计公司得到了广泛应用[2], 并开发出了一系列可靠性仿真工具, 如Cadence 公司开发的Relxpert 软件模块、 Mentor公司的Eldo 软件、 马里兰大学的maCRO 软件、 TI 公司的HOTRON 软件等工具均已成为成熟的应用产品。

值得关注的是, 工信部电子五所、 北京大学微电子所、 西安电子科技大学微电子学院等通过开展半导体器件与集成电路的可靠性技术研究工作[3-4], 推出了CARMES、 ICSES、 XDRT 等可靠性仿真工具[5-6], 但上述工具主要是建立在国外HCI ( Hot Carrier Induced)、 NBTI ( Negative Bias Temperature Instability)及互连等失效模型复用基础上, 其系统性、 全面性和准确性还有待进一步完善提升。 此外, 对大规模集成电路, 其模拟电路部分与数字电路部分相比更容易失效, 且集成电路失效的原因80% 都是由模拟电路部分失效造成的[7]。 卿健等[8]建立了基于NBTI 效应的VerilogA 等效受控电压源, 有效反映NBTI 退化对电路性能的影响; 藏范军等[9]提出两种电平转换电路方案, 解决了传统电平转换电路性能较差, 且易产生误码的问题; 刘红等[10]采用基于信息熵的方法生成被测容差电路的故障特征, 可对容差电路的软故障进行诊断定位; 此外, 还有许多研究人员分别对模拟乘法器、 QFP(Quad Flat Package)封装互连结构、 电路板和IGBT(Insulated Gate Bipolar Transistor)等模块进行了性能退化研究[11-14], 但上述研究均是针对某一特定模块开展的, 未形成通用、 系统性的性能退化仿真方法。 综上, 笔者通过对失效机理模型的深入研究, 完成了仿真流程模型设计、 失效物理模型推导及模型参数提取3 项关键工作, 最终得到了一种准确、 可行的模拟电路性能退化仿真方法。

1 模拟电路性能退化机理模型研究

1.1 HCI 模型

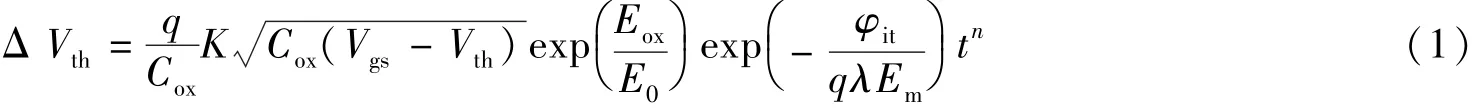

随着集成电路器件特征尺寸的减小, 器件沟道中的电场强度会增大。 在高电场作用下, 沟道内会形成热载流子, 当其能量大于栅氧化层势垒时, 载流子会进入到氧化层内部, 产生界面态陷阱和氧化层陷阱电荷, 引起氧化层的损伤, 从而导致阈值电压、 迁移率等电学性能的改变。 其中, 阈值电压的变化ΔVth和界面态陷阱的关系[15]可表示为

其中Eox是栅压作用下的垂直电场;Em是漏极电压作用下的最大横向电场;λ是热电子的平均自由路径;φit是热电子产生一次碰撞电离所需要的最小能量。

迁移率的退化μ计算公式为

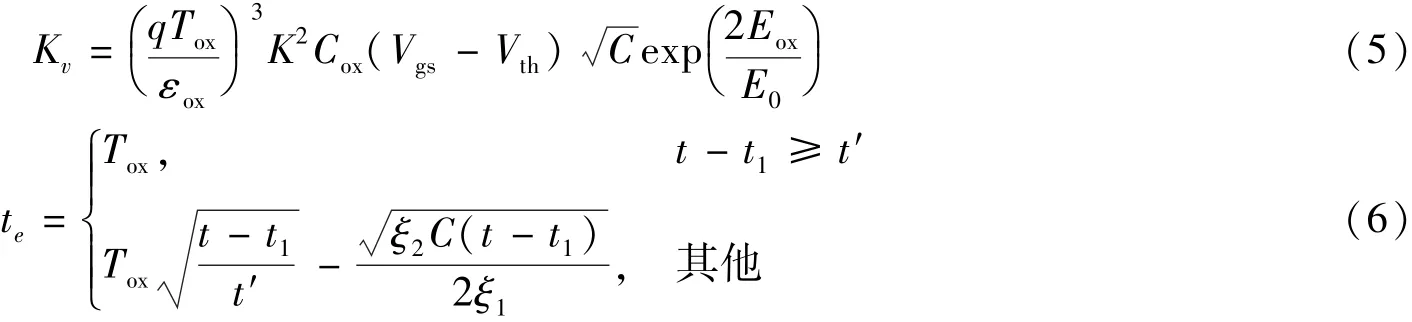

模型中部分参数取值如表1 所示。

表1 HCI 模型系数取值Tab.1 HCI model coefficient values

1.2 NBTI 模型

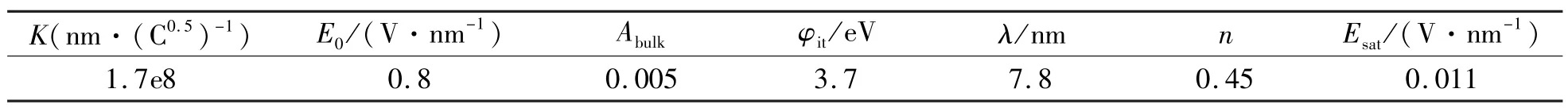

在高温和负栅压作用下, 器件沟道中的空穴会向Si-SiO2界面移动, 在进入栅氧化层后, 将造成界面陷阱电荷或氧化层中固定正电荷的积累, 进而引起阈值电压等电学性能的变化。 为了能捕获应力和恢复周期初始时的阈值电压的突然变化, 采用基于反应扩散的预测模型。 阈值电压变化模型[16]如图1 所示。

图1 阈值电压变化模型Fig.1 The variation model of threshold voltage

在应力(stress)阶段, 即时间t在t1~t2阶段时, 阈值电压变化可表示为

式(3)、 式(4)中部分参数可由

计算得到。 其中t′对应于载流子扩散到距离为Tox的时间, 如对1.2 nm 厚的栅氧化层,t′的默认值为2.5 ms。 研究表明, 采用一个长期( long-term) 的闭环模型, 可以处理多个周期内应力和恢复阶段循环作用下的阈值电压的变化, 该模型可根据氧化层厚度、 电压、 占空比和信号概率进行扩展, 模型公式为

其中β为占空比,Tp为周期。 模型中部分参数默认值如表2 所示。

表2 NBTI 模型系数取值Tab.2 NBTI model coefficient values

1.3 TDDB 模型

受工艺尺寸减小的影响, 栅氧化层所处的电场强度会增大, 在较高的电场下工作一段时间后, 氧化层的品质会发生改变, 进而导致栅电流等电学性能的改变。

TDDB 服从于weibull 分布[17], 累计失效概率可表示为

其中α是特征寿命(CL: Characteristic Lifetime),β是weibull 斜率参数, 表示失效率的趋势。 在综合考虑温度和栅氧表面的面积, 超薄(氧化层厚度小于5 nm(0.25 μm 工艺及以下))氧化层的TDDB 寿命模型可归纳为[17]

其中F为假设试验条件下的累积失效百分位数相同条件下的累积失效百分位数,a,b,c,d,ATDDB是通过试验确定的模型拟合参数。 它们的典型值[18]分别为β=1.64,F=0.01%,a=-78,b=0.081,c=8.81×103,d=-7.75×105。

2 基于退化的spice 仿真器仿真流程

2.1 生成退化的spice 仿真器

根据退化模型公式, 修改BSIM4.5 模型源代码, 再将退化的BSIM4.5 模型和spice 仿真器结合。 即:将BSIM4.5 和spice 仿真器结合, 在visual studio 中将生成可执行文件(该可执行文件是新生成的可靠性模型的仿真器)。

2.2 spice 模型选取

将生成的spice 仿真器放到IC-CAP2018 调用模型的路径下, 以使IC-CAP 进行模型仿真时, 调用的是新建立的可靠性模型。 在使用IC-CAP 仿真时, 需要先进行如下操作: 首先, 设置IC-CAP 中的set up;其次, 提供符合IC-CAP 需要的spice 电路网表文件; 最后, 在前两步的基础上进行仿真。

2.3 模型参数提取

事实上, 上述失效物理模型的确定还需要经过测试、 拟合和参数提取等步骤, 测试的目的是采集数据, 并用其数据进行曲线的拟合和参数的提取。 对HCI、 NBTI 和TDDB 的性能退化模型, 测试方法为:1) 不同Vgs下(Vgs从0.8 V ~3.3 V), 在Vbs=0 V 时测试Ids与Vds, 得Id-Vd曲线; 2) 不同Vgs下, 在Vbs=-1.5 V时测试Ids与Vds, 得Id-Vd曲线; 3) 不同Vbs下, 在Vd=0.1 V 时测试Ids与Vgs, 得Id-Vg曲线; 4) 不同Vbs下, 在Vd=3.3 V 时测试Ids与Vgs, 得Id-Vg曲线。 在施加应力阶段内选取特定时间点进行测试, 在每个时间点均会得到4 个mdm 文件。

参数提取的基本流程如图2 所示, 将测量得到的mdm 文件导入ICCAP2018 中, 将同一应力阶段内每个时间点的参数曲线拟合好, 再对比各个时间点下的模型卡的参数, 从而得到各个参数随时间变化的关系。

图2 BSIM 模型参数提取流程Fig.2 The extraction process of BSIM model parameter

2.4 模拟电路部分的仿真

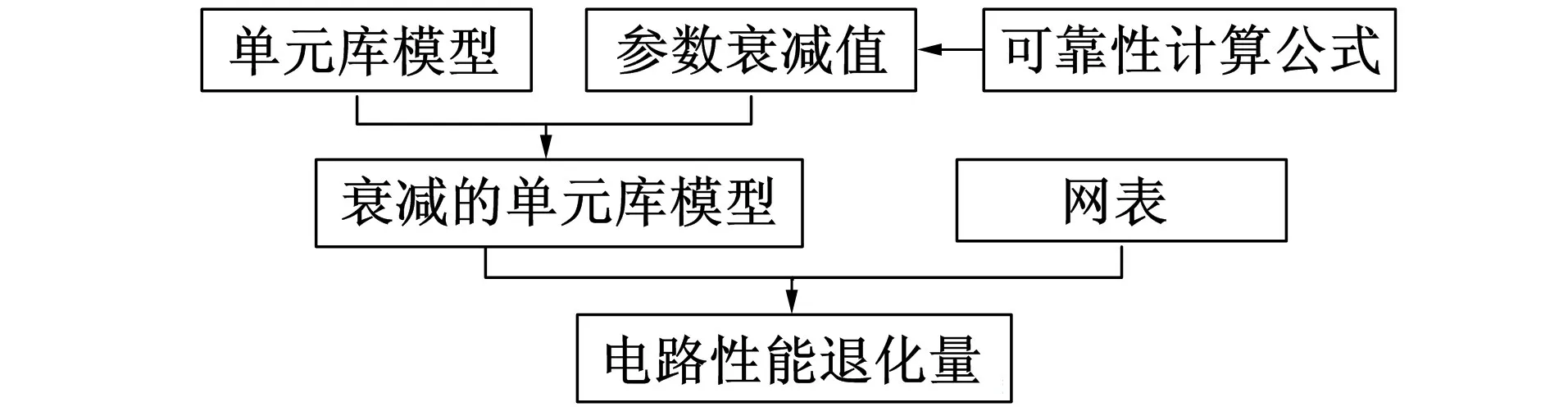

流程如图3 所示, 根据晶体管级可靠性计算公式和参数衰减值, 修改单元库中的模型文件, 使其包含由失效机制导致的参数漂移值, 生成退化的模型参数文件, 最终利用衰减的单元库模型与网表, 即可计算模拟电路中性能的退化量。

图3 模拟电路部分退化仿真流程Fig.3 The degradation simulation of simulation circuit

3 典型运算放大器性能退化研究

3.1 电路原理图及测试图绘制

采用Cadence virtuoso 软件绘制由3.3 V MOS 管搭建的轨到轨(Rail to Rail)运放电路原理图(见图4)及电路测试图(见图5)。

图4 轨到轨运放电路原理图Fig.4 Rail-to-rail operational amplifier circuit schematic

图5 运放电路测试图Fig.5 The test chart of operational amplifier circuit

3.2 测试电路网表及衰减模型获取

测试电路网表及部分带有衰减的spice 模型分别如图6a 和图6b 所示。

图6 测试电路网表及衰减模型Fig.6 Test circuit netlist and attenuation model

3.3 仿真结果分析

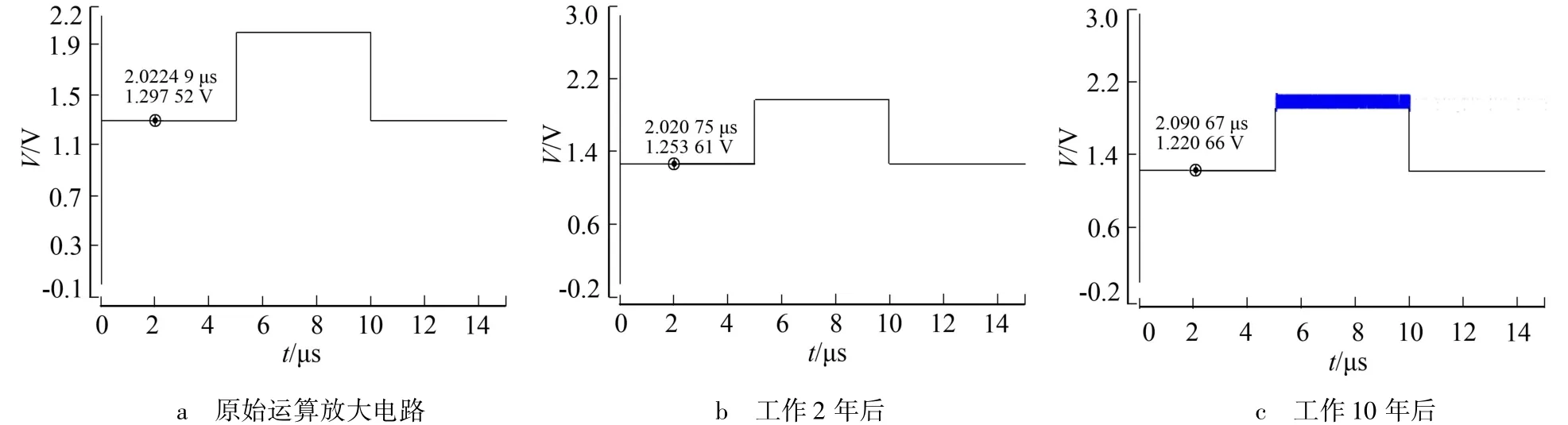

笔者采用Cadence spectre 对轨到轨运放电路性能退化进行测试仿真, 仿真结果如图7 所示。 从图7a可以得出, 运放电路在25 ℃下工作2 年后,阈值电压值漂移约为46.37 mV; 从图7b 中可以得出, 运放电路在25 ℃下工作10 年后, 阈值电压值漂移约为80 mV。 按照JEDEC-JASD28 标准规定, 阈值电压较正常时漂移50 mV, 则该器件失效。 因此, 工作2 年后, 该器件正常工作; 但在工作10 年后, 该器件失效。

图7 运算放大电路25 ℃下性能退化仿真结果Fig.7 The simulation results of performance degradation at 25 ℃

4 结 语

笔者通过对国内外模拟电路虚拟化验证技术现状进行分析, 阐述了模拟电路虚拟化验证工作的必要性; 提出了模拟电路虚拟化验证流程, 并对常见的HCI、 NBTI、 TDDB 失效物理模型进行深入理论研究,总结出了模型参数提取方法; 选取3.3 V MOS 管搭建的轨到轨运放电路进行验证, 得出在25 ℃环境温度下, 工作2 年和10 年后的阈值电压漂移值及器件的失效状态。 概括来讲, 该项研究以理论结合具体仿真工具的方式, 实现了对典型模拟电路性能退化的虚拟化验证, 这对后续集成电路的虚拟验证工作的开展提供一定技术支撑。