基于SiTCP通信协议的FPGA可回滚远程固件更新方法

陈 长 王 铮 胡 俊

1(中国科学院高能物理研究所 北京 100049)

2(中国科学院大学 北京 100049)

3(核探测与核电子学国家重点实验室 北京 100049)

在大型高能物理实验领域,探测器的集成度越来越高,对后端读出电子学数据处理及数据传输能力的要求也越来越高;现场可编程门阵列(Field Programmable Gate Array,FPGA)作为可编程器件以其强大的数据处理能力、丰富的高速数字接口设计和灵活的功能实现,成为高能物理实验电子学系统中的核心器件之一。常用的FPGA多属于掉电易失器件,每次上电时都需要从板上Flash存储器加载固件到片上内存(Random Access Memory,RAM)才能实现相应功能。

需要更新固件时,专用上位机软件通过JTAG(Joint Test Action Group)加载器将数据发送给FPGA,对Flash 进行编程,修改存储内容;再次上电时 ,FPGA 从 Flash 内加载更新后的固件。JTAG 加载器还能直接向FPGA的片内RAM发送固件,这种方式耗时更少,但重新上电后内容丢失。这两种方式都需要在现场通过线缆接到电路板上的预留JTAG接口进行操作,而大型高能物理实验的探测器和电子学系统往往安装在地下、水下、辐射场等特殊环境中;因此,使用传统的专用JTAG 线缆对单个FPGA进行更新变得不再合适。

1 背景介绍

大型高能物理实验的电子学系统中普遍实现了FPGA 远程更新功能。北京谱仪第三代(Beijing Spectrometer,BESIII)改造工程的Muon鉴别器电子学读出系统采用了PLD(Programmable Logic Device)器件控制的Multi-Passive Serial配置方式[1]:更新固件通过VME(Versa Module Eurocard)总线发送给接口FPGA,对其附属的Flash 进行编程;接口FPGA 再向各条链路的主控FPGA 发送固件,主控FPGA 完成对其附属Flash 的编程;最后每条链路的主控FPGA 向各电子学插件下发固件,完成665 块FPGA的更新。

CMS(Compact Muon Solenoid)实验的电磁量能器off-detector 电子学系统共有738 块使用FPGA的电路板,研究人员设计了JTAG 分发板(JTAG Distribution Board,JDB),它和其他电子学插件都安装在VME机箱内;JDB作为电脑和需要远程更新的电路板之间的桥梁,电脑连接到JDB,通过VME 机箱背板的MTM(Module Test and Maintenance)总线来连接其他插件,或者由JDB 直接接出多根JTAG信号线到其他插件[2]。

ITER(International Thermonuclear Experimental Reactor)实验由于处于强中子辐射场,其电子学系统 主 控 板 通 过 PCIe(Peripheral Component Interconnect express)链路连接到上位机,由上位机接收远端发来的更新固件并下发给FPGA[3]。江门中微子实验(Jiangmen Underground Neutrino Observatory,JUNO)为了精确采集波形而采用了源端数字化方案,整个读出电子学系统包含近7 000块电路板,密封置于水下靠近探测器的位置。该电路板上使用一块较小的FPGA 作为控制器,通过网络接收固件,专用于给主FPGA 进行更新[4]。其他如北京同步辐射装置上实验站的像素探测器读出系统,也因为处于辐射环境而采用基于XVC(Xilinx Virtual Cable)技术的远程更新方法[5],利用ARM 处理器模拟JTAG时序对FPGA片内RAM进行配置。

综上所述,现有的FPGA远程更新方法,一般需要额外的器件或设备,如PLD、ARM等,增加了硬件设计复杂度和成本;额外器件也降低了系统的可靠性,如更新过程中额外辅助器件出错且无法恢复,将造成无法修复的系统崩溃。本文提出并实现了一种基 于 SiTCP(Silicon Transmission Control Protocol)协议的可回滚远程更新方法,利用板上现有的数据传输接口,无需额外硬件;且带有安全机制,保证FPGA能从更新故障中恢复,提高可靠性。

2 方法及实现

本设计在FPGA内实现纯硬件的TCP/IP网络协议,结合Xilinx 的QuickBoot 功能,无需外部额外硬件配合,实现远程通过网络协议更新FPGA 固件的目标。同时调整Flash内固件存储的结构,添加跳转指令和一块存放早前版本固件的区域,实现故障情况下的回滚功能;更新出错后,下次上电会加载早前正确版本的固件。

2.1 硬件设计

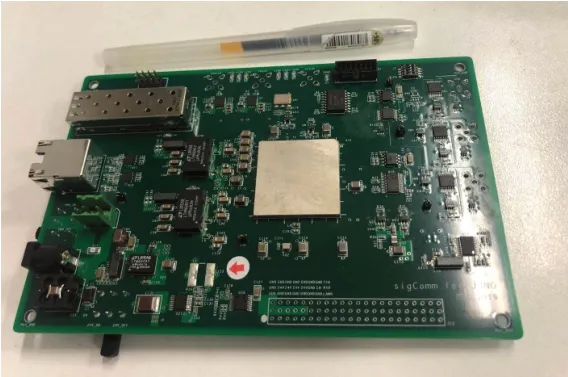

本设计中的FPGA更新方式不依赖于外部硬件设计,因此采用了一块自设计的板卡。硬件电路包括一块Xilinx XC7K325T系列FPGA,一块用于存储FPGA 固件的 Micron N25Q256A Flash 存储器,外部接口为基于SFP(Small Form-factor Pluggable)的网络接口,实物如图1所示。

图1 测试板实物图Fig.1 Photograph of a test board

2.2 FPGA固件设计

FPGA 固件主要包括以下模块:基于SiTCP 的网络传输模块、FIFO(First In First Out)缓存、远程更新的FSM(Finite State Machine)状态机和控制Flash读写的SPI(Serial Peripheral Interface)接口[6]。

SiTCP 协议[7]是一款商用的、基于硬件的 TCP/IP 协议,用FPGA 硬件描述语言的代码和Xilinx 的IP 核实现了从传输层到数据链路层的功能,因而不需要MAC(Media Access Control)硬件控制器。本设计中,使用FPGA 的高速数字接口GTX(Gigabyte Transceiver)作为物理层的 PHY(Physical)接口,因此无需外部额外的PHY 芯片,从而完全在FPGA 内实现了硬件的TCP/IP 协议。这种基于FPGA 实现TCP/IP 协议的方法,无需额外以太网芯片,降低了硬件设计复杂度和成本,有较好的灵活性,被一些高能物理实验的电子学读出系统所采用[8-9]。

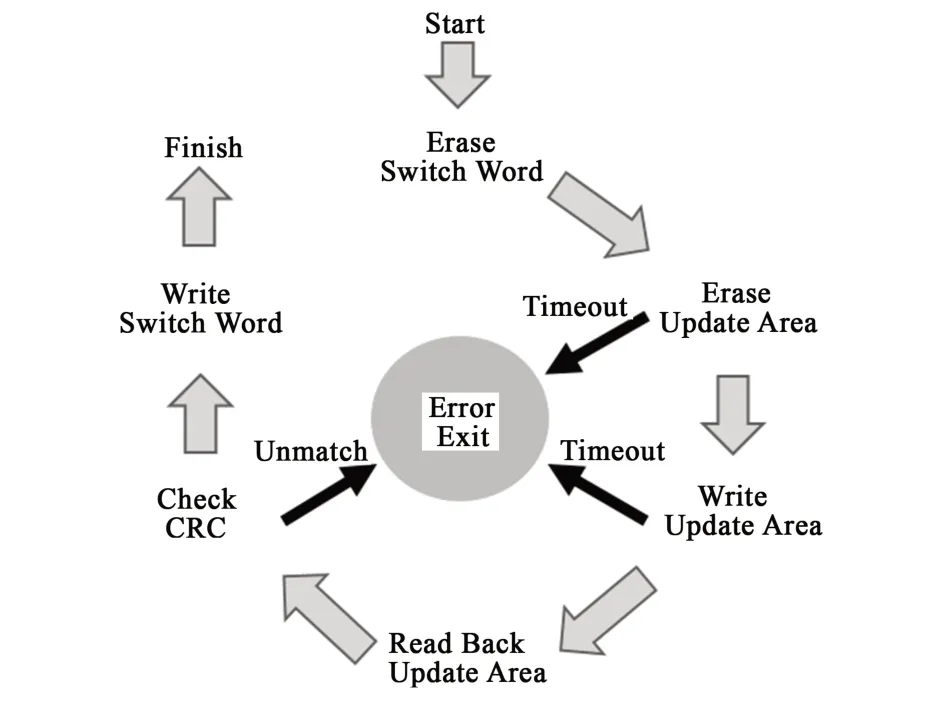

经SiTCP 解析后的数据,以8 bit 的长度送入FIFO 进行缓存,然后以32 bit 的长度送给FSM 状态机。作为远程更新功能的核心控制模块,状态机完成以下功能,其状态转换如图2所示。

1)查询指定寄存器的值,确定是否开始远程更新操作。

2)远程更新开始后,先执行擦除Flash内跳转指令的动作。跳转指令的作用是当FPGA加载到此处时,指定跳转到特定位置继续加载。所以当跳转指令存在时,FPGA会跳转到更新区域去加载固件;反之则会在当前位置继续向后加载,读取到的就是回滚区域内的早前版本的固件。因此跳转指令是保证更新异常后FPGA仍能正常工作的关键。

3)擦除更新区域的内容;接收上位机发送的固件数据,写入更新区域。

4)回读更新区域的内容,计算CRC(Cyclic Redundancy Check)校验值,并与写在更新区域末尾的校验值进行比较。

5)CRC 校验通过后,进行写跳转指令的操作,更新完成。

图2 远程更新状态机跳转示意图Fig.2 State transition diagram of the remote update process

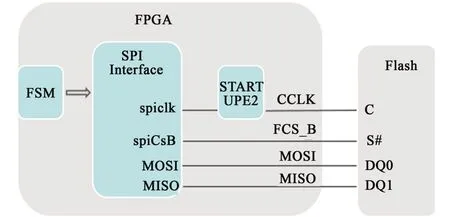

SPI 接口模块是一个串行/解串器,接收状态机的8 bit 数据输出,以串行方式输出到Flash 的DQ0管脚。模块输出的Flash读写时钟spiclk需要通过原语STARTUPE2连接到FPGA专用管脚CCLK上,再连接到Flash,用于驱动Flash读写,如图3所示。

图3 spiclk共享FPGA专用管脚CCLK连接示意图Fig.3 Block diagram for user spiclk pin connected to FPGA dedicated CCLK pin using Xilinx STARTUPE2 primitive

2.3 FPGA固件的生成与处理

FPGA固件设计完成后,用Xilinx提供的ISE设计软件生成bit文件,该文件可写入FPGA片内RAM用于直接加载,但掉电后会丢失固件信息;也可进一步生成mcs 文件写入Flash 中,掉电后不会丢失,FPGA将在上电后自动加载Flash中的固件信息。

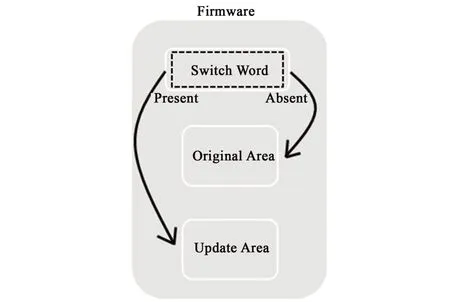

为了实现回滚功能,需要在生成mcs 文件时进行一些特殊处理。普通的mcs文件只包含一块存放固件的区域,本设计中的mcs文件包含两块区域(回滚和更新区域)及跳转指令,示意图见图4。首先,将这份包含跳转指令、回滚区域和更新区域的固件通过传统的JTAG方式下载到Flash。当需要更新固件时,新的固件也要含有§2.2 中所述的必要FPGA功能模块,且状态机内的更新区域起始地址保持不变。由于mcs文件中不仅包含要写入Flash的数据,还有地址和校验位;而新的固件会在状态机的控制下写入特定的Flash地址,因此需要生成不含地址和校验位的bin文件,用于上位机向FPGA发送。

图4 实现回滚功能所需的固件结构,跳转指令是否存在将决定加载方向Fig.4 Firmware structure for rollback function,existence of switch word determines FPGA loading process

2.4 上位机固件发送程序

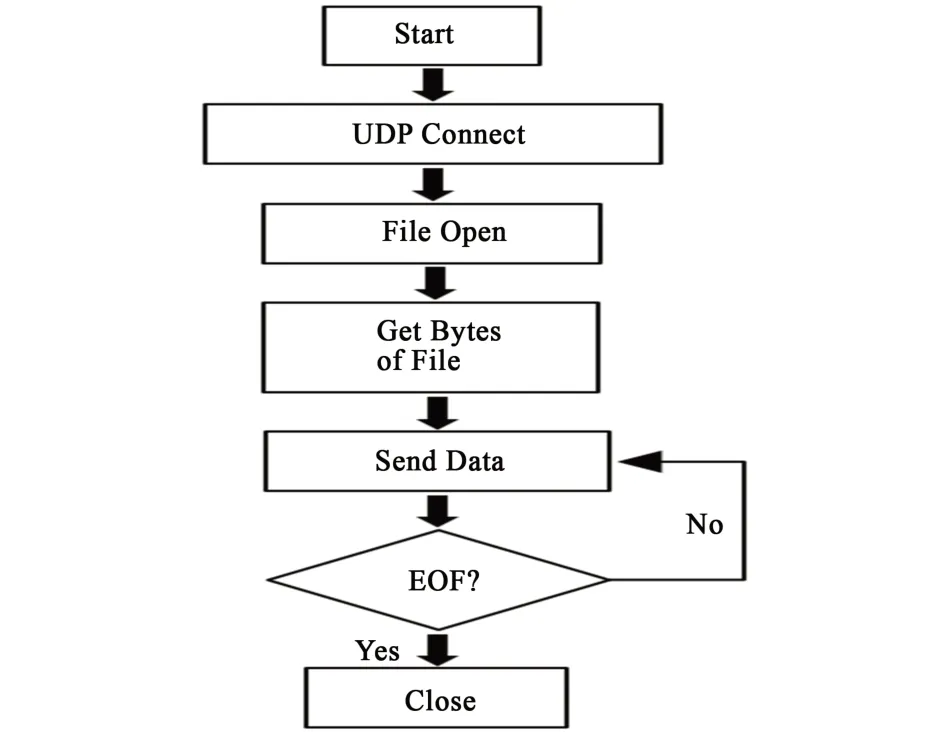

使用MATLAB 编写发送程序,该软件封装了UDP 函数,使用方便。写好FPGA 的IP 地址和端口号,即可建立UDP 连接。以读的形式打开bin 二进制文件,遍历文件以获取字节数。按照SiTCP 的UDP 包格式[7]来组装要发送的数据,设置一个包内的数据长度,按照数据长度读取二进制文件,向FPGA 进行发送。程序流程图如图5 所示。FPGA解析得到数据后由两个功能模块分别完成Flash 编程的状态控制,以及与Flash的SPI接口功能。

图5 上位机固件发送程序流程图Fig.5 Flow chart of MATLAB sender in host computer

3 功能测试

按照§2.3 的步骤生成一份三段式的固件,通过JTAG 方式下载到Flash 并加载到FPGA。拨动板上拨码开关以置位寄存器,开始远程更新流程。等待Flash 擦除操作完成后,上位机运行MATLAB程序,通过网络协议向FPGA发送一个版本号和功能均不同的更新固件,开始写Flash。CRC校验以及写跳转指令完成后,一系列寄存器会置位以表示不同的状态,如CRC校验是否通过、跳转指令是否写入、更新是否完成,以及一系列错误提示如超时等。提示更新正常完成且无错误指示,重新上电;可见LED 以不同的方式闪烁,使用Xilinx 的iMPACT 软件读取到正确的自定义版本号UserID,说明远程更新成功。

安全回滚功能的测试,以在更新过程中断掉电源的方式进行。经多次验证,在更新过程中不同时点掉电(发生异常),再次上电后FPGA 均可以回滚到早前版本的固件,不至于无法工作。

4 结语

本文介绍了一种带有回滚功能的FPGA远程更新方法。该方法基于SiTCP 通信协议,由上位机向FPGA 发送更新固件,对Flash 进行编程,无需增加额外以太网芯片或辅助器件。它有以下特点:利用FPGA自身资源实现PHY和MAC芯片的功能,不需要额外芯片且具有灵活性,降低了硬件设计成本和复杂度;带有保障机制,更新异常时可以回滚到安全的版本正常工作,提高了可靠性;对于使用SiTCP作为网络传输协议的电子学系统,不需要集成其它通信协议;采用UDP 协议发送固件,能利用广播向多个FPGA发送,具有扩展性。