一种用于高能离子注入机射频加速的数字移相器设计

刘 辉,王新辉,杨 追,周志英

(1.长沙学院 电子信息与电气工程学院,长沙 410022;2.湖南普奇地质勘探设备研究院,长沙 410201)

0 引言

兆电子伏特(MeV)以上高能离子注入是微电子工艺中的一种重要的掺杂技术,在大规模集成电路制造中有着广泛应用,射频(radio frequency)加速是实现离子束高能量的关键技术[1-2]。兆伏级高能离子注入一般采用线性双腔结构的射频谐振加速,对离子束加速是用一系列双腔结构的射频谐振腔进行加速,每个加速腔室均采用独立的射频功率电源系统,每个双腔加速腔独立控制,通过多级串联加速,将离子束的能量提高至兆电子伏特以上。本文利用直接数字合成技术,设计了一种高精度和稳定可靠的数字移相器,保证射频功率电源时间相位正好与进入腔体的离子束同步,满足MeV能量的离子注入机控制要求。

1 系统总体设计

本设计以STM32单片机作为微处理器,由主控计算机,通信接口电路,石英晶体振荡器,时钟分配芯片AD9510,直接数字式频率合成器DDS(direct digital synthesizer)芯片AD9959,16路滤波放大电路和16路输出通道组成,系统电路组成方框如图1所示。

STM32处理器向DDS芯片的每一个输出通道写入输出正弦信号频率控制字、相位控制字和幅度控制字,各输出通道写入的相位控制字不同,输出的正弦波形就会产生相位差,从而保证每个输出通道正弦信号频率和幅度一致且同步,而相位差精确可调。

时钟分配芯片AD9510主要解决时钟信号送到每一个DDS芯片上的时间同步问题,在多通道数字移相器印制电路板上,每个DDS芯片距离时钟分配芯片AD9510的时钟线长短不同,系统时钟频率是500 MHz,单个时钟周期为2 ns。必须要考虑时钟线长短不同而导致的相移,STM32处理器根据输出时钟到达各DDS芯片的不同时钟线长度,向时钟分配芯片AD9510每路输出的寄存器写入不同的值,产生多组不同延时的时钟信号输出,确保到达各DDS芯片输入引脚的高频工作时钟边沿对齐。

图1 系统电路方框图

如图2所示,每个双腔加速腔中,两边为电地极,中间电极为加速电极。离子源发出的连续正离子束,由射频加速腔进行调制、压缩,形成间断的正离子束,从电地极和中间电极的孔隙中穿过,当正离子束通过前腔时,如果中间电极上的电压正好为负半周,进入的离子束被内部电场加速。加速后的离子束经过中间电极后,进入后腔,如果此时中间电极上电压正好变为正半周,离子束就仍然被加速。由于离子束的能量不断增加,速度越来越快,之后的加速腔中间电极的波形就要根据不同能量的离子束进行同步调整,使离子束进入该加速腔时正好是处于加速状态。通过多级串联,将离子能量加速至MeV以上。

图2 相位控制原理框图

中间电极通过同步调谐相位控制器与射频电源连接,数字移相器的各输出通道连接各同步调谐相位控制器。同步调谐相位控制器通过电压探头采集调谐筒内电极上电压信号送到相位检测单元输入端,并将由数字移相器某通道的输出信号经过功率放大电路放大后送到相位检测单元参考端作为基准同步信号,相位检测单元根据基准同步信号及调谐筒内负载信号相位实时检测值的差值产生一个直流信号,经过一个放大器放大去调控一个压控振荡器,压控振荡器的输出经过二分频后去控制射频电源的同步端,最终使得射频输入与基准同步信号一致并将输出相位锁定。

2 系统硬件设计

2.1 主控单元

主控单元选用STM32F405RGT6微处理器,是带有FPU的ARM Cortex-M4内核的32位高性能CPU,自适应加速器,允许0等待状态执行。处理器频率高达168 MHz,速度为210 DMIPS。高达192+4 Kbytes的SRAM和1 MB的Flash,且配有15个通信接口、136个快速I/O接口,具有处理速度快、功耗低和较强的控制能力。STM32F405RGT6微处理器负责移相器的控制,通过串行通信接口接收上位主控计算机发送的控制命令和参数设置;对AD9510芯片进行操控,控制AD9510芯片输出四路不同延时的带有驱动输出的时钟信号;对AD9959芯片进行操控,控制4个AD9959芯片输出16通道不同相位、满足多腔同步射频加速的正弦信号。

2.2 AD9959芯片接口电路设计

AD9959芯片是美国ADI公司生产的一款高集成度高速频率合成器,能产生 500 MHz的正弦波信号。该芯片内部含有四路直接数字频率合成(DDS)通道,每个通道有一个专门的32位频率控制字,14位相位偏移控制字和一个10位输出振幅控制字,各通道输出信号频率、相位、振幅都可以独立编程。所有通道共用一个系统时钟,可以执行16级的频率、相位和幅度调制[3]。

AD9959使用节省空间的56脚LFCSP封装,接口电路如图3所示,本设计中使用的主要引脚功能如下:

MASTER_RESET:高电平有效复位输入引脚,将使AD9959内部寄存器复位到缺省状态;

PWR_DWN_CTL:外部电源掉电控制引脚;

DAC_RSET:输入引脚,DAC设置参考电流,通过一个1.91 kΩ电阻接地;

I/O_UPDATE:输入引脚,该脚的上升沿使I/O口缓冲中的数据送至激活的寄存器中,I/O_UPDATE信号应与SYNC_CLK信号保持同步,并须满足建立时间与保持时间的要求,以保证到DAC输出的数据有固定的延迟管道;

SCLK:I/O操作的串行数据时钟,数据位在SCLK的上升沿写入数据,下降沿读出;

SDIO_0:串行数据输入和输出引脚;

SDIO_1、SDIO_2:用于串行数据引脚或启动输出幅度的斜坡上升或下降;

SDIO_3:用于串行操作数据输入输出,也可用于控制DAC输出幅度的斜率;在单位或者2位模式,此引脚用于SYNC_I/O。

CH0_IOUT ~CH3_IOUT:输出通道,4个通道各有一个互补输出端;

CS:片选串口使能信号端,低电平有效;

SYNC_IN:输入引脚,可同步多片AD9959;

REF_CLK:参考时钟或振荡输入端。

图3 AD9959芯片接口电路图

AD9959具有SPI串行通信接口,通过SDIO_0~SDIO_2、CS和SCLK等引脚实现与微处理器的通信。

2.3 AD9510芯片接口电路设计

高精度低抖动的时钟源是整个系统得以实现的最基本保证。AD9510是美国模拟半导体公司推出的一款精确时钟分配芯片,该款芯片通过SPI串行编程来控制输出时钟间的相位延迟,它提供多路输出时钟分配功能,低抖动、低相位噪声时钟分配,能够极大地提升DDS芯片的时钟性能[4-5]。

AD9510芯片接口电路如图4所示。14、15脚CLK1和CLK2B接用户输入参考时钟频率,16脚FUCTION接1 kΩ电阻接地,可以通过编程实现复位、同步和下拉。OUT0、OUT0B、OUT1、OUT1B、OUT2、OUT2B和OUT3、OUT3B输出4路独立时钟,为高速4片DDS芯片提供时钟信号,SCLK、SDIO、SDO和CSB作为与STM32处理器的串行通信接口。STM32微控制器通过SPI接口(serial peripheral interface)对AD9510芯片所有内部寄存器状态进行读写,设置AD9510芯片满足系统时钟需求。

图4 AD9510芯片接口电路图

2.4 滤波放大电路设计

图5是滤波放大电路原理图,AD9959芯片的DDS通道由数模转换器输出模拟信号,滤波器电路将其平滑为连续的正弦波形,经过射频耦合变压器输出给U20运算放大器电路进行放大,通过输出通道输出所需要峰-峰值10 V的正弦信号。

图5 滤波放大电路图

3 系统软件设计

3.1 主程序设计

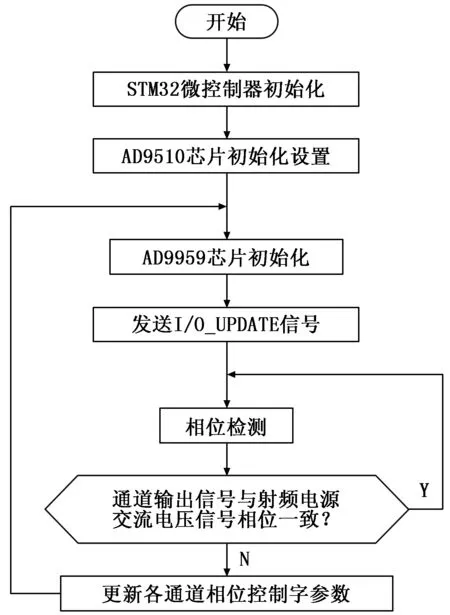

软件设计主要包括STM32微处理器程序设计以及主控计算机程序设计。主控计算机采用VB语言编写人机交互界面。STM32微处理器程序采用C语言编写,其程序流程如图6所示。首先对STM32微处理器的时钟和I/O口配置,然后对AD9510芯片相关寄存器进行配置和参数设置,再对AD9959芯片进行初始化。

图6 主程序流程图

当向AD9959不同的通道写入相同的频率字、不同的相位字时,AD9959 输出相同频率、具有一定相位差的正弦信号。主程序运行过程中循环检测各调谐负载信号的相位值,计算与数字移相器通道各输出的基准同步信号之间的相位差,自动调节射频电源的同步端,控制射频电源的输出相位与基准同步信号相位完全一致。

3.2 AD9959初始设置程序

通过STM32微处理器的SPI接口来对AD9959芯片进行初始设置,先初始化各个寄存器、数据寄存器,再进行串口传输模式、初始频率输出设置、工作模式等,然后选择DDS通道,分别向其中写入频率控制字、相位控制字和幅值控制字,再后发送I/O_UPDATE信号,所有通道输出所设置频率及相位的正弦信号[6-7]。流程图如图7所示。

图7 AD9959初始化流程图

本移相器要求输出的正弦波为13.56 MHz固定频率的连续信号,所以设置AD9959为单频模式。单频模式下,只需将频率控制字 FTW,相位偏移字POW 以及幅度控制字ASF 分别写入AD9959各通道的寄存器 CFTW0、 CPOW0和ACR中。每个DDS通道输出的信号频率是频率调谐字FTW和系统时钟频率fs的函数,计算公式是:fout=(FTW*fs)/232,设AD9959芯片的主频fs为500 MHz,可以计算出频率控制字FTW=6F15619H,使用串行I/O口,发送各通道所需要的频率控制字到I/O Buffer。在所有通道设置完毕后,发送 IO_UPDATA信号,将I/O Buffer中的数据传送到内部寄存器即可输出多路同步信号。

3.3 AD9510初始设置程序

A9510芯片的时钟分配模块提供八路相互独立的输出,四路LVPECL(low voltage positive emitter coupled logic)电平输出和四路LVDS(low voltage differential signaling)或CMOS(complementary metal oxide semiconductor)输出,分配由8个可编程的分频器对应控制,可对每路输出频率取1~32整数倍分频,还可以通过各分频器改变每路输出脉冲频率占空比和相位偏移。相位偏移功能用于实现时序粗调。某些输出还提供可编程延迟特性,通过一个5位字进行编程,提供32个可用的延迟时间,最长延迟时间10 ns。本设计中使用AD9510产生四路100 MHz的LVPECL电平时钟给四路DDS芯片作为输入时钟。

4 测试结果与分析

在确定了数字移相器硬件结构后,搭建了硬件实验电路,并通过软件编程、系统调试后,使用示波器、频谱分析仪等设备分别对数字移相器输出的单通道正弦信号的频率精度、两通道正弦信号相位差精度进行了测量,测试结果如表 1、表 2 所示。

表2 两通道正弦信号相位差测试结果

由表1可知该数字移相器产生频率范围0~100 MHz的单通道正弦信号,分辨率能够达到0.02 Hz;由表2可知,该移相器能够完成任意两路之间的相位差调节和设置,输出信号相位值精度高,分辨率达到0.025°。

5 结束语

本文针对高能离子注入机多腔射频加速同步加速控制这一问题,设计了一种基于STM32F405RGT6微处理器和AD9959DDS芯片的多通道数字移相器,介绍了系统组成、工作原理及硬、软件开发设计。测试结果表明:该数字移相器结构简单,输出信号频率范围广、稳定度高、频率和相位分辨率高,各通道正弦信号的频率、幅度和相位等指标都可以独立调整。作为同步参考信号发生器用于控制多级串联双腔射频加速高能离子注入机的同步加速,能够满足射频电源的时间相位控制要求,可以实现离子能量连续加速至兆电子伏特(MeV)级以上,在实际工程应用中具有很好的前景,将对射频加速高能离子注入机的国产化产生重大助推作用。