基于FPGA 的数字电路“口袋实验室”设计

王 嵘,张元树,杨富琴,万永菁

(华东理工大学 信息科学与工程学院,上海 200237)

创新人才、服务创新型社会是大学人才培养的中心任务[1]。一般而言,创新实验只给定实验任务和实验要求,鼓励学生广泛查阅资料,充分发挥学生的主观能动性和积极性,创造性地使用多元化的实验方法完成实验任务[2-3]。

数字电路作为一门专业基础课,除了介绍数字电路的理论知识外,更需要通过配套的实验平台将理论知识和实践环节相结合,培养学生的动手能力和实践创新能力。为此,自主开发了基于FPGA 的数字电路“口袋实验室”。该“口袋实验室”基于目前流行的FPGA 芯片开发,已经实际应用于数字电路教学实践中,得到了学生的好评。此外,该系统还为本科生创新教育、大学生创新创业计划和各类学科竞赛提供了服务[4-6]。

1 总体设计

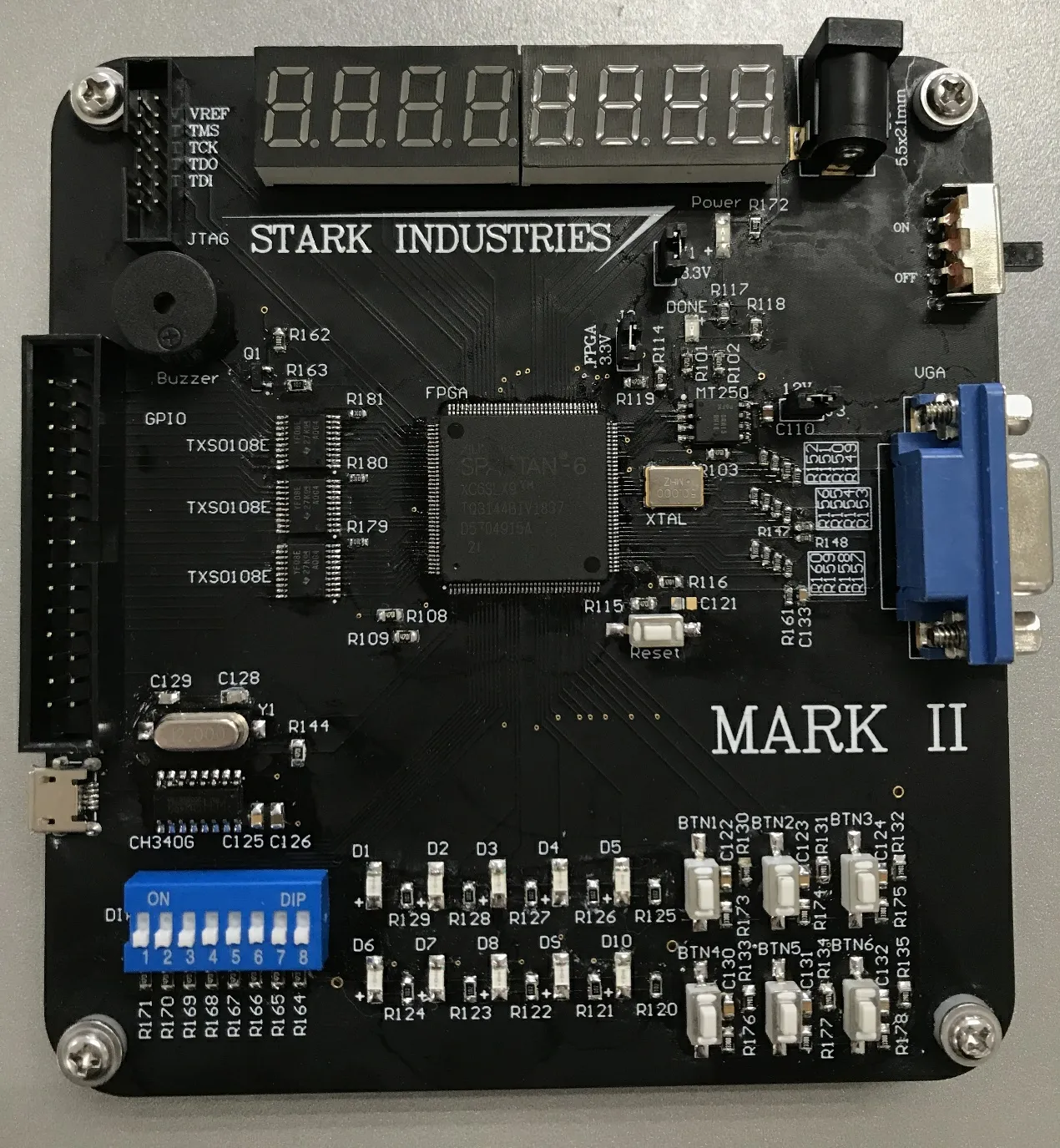

“口袋实验室”的电路包括电源、FPGA、下载电路、数码管、VGA 接口、拨码开关、按键、LED灯和双排针扩展接口。其总体框图见图1,实物图见图2。

图1 系统总体框图

图2 系统实物图

XC6SLX9 是Xilinx 公司的Spartan 系列FPGA,采用45 nm 工艺,共有9 152 个Logic Cells、1 430 个Slices、90 kB 分布式RAM,共有144 个引脚,其中102 个是通用I/O 口,资源相对丰富。XC6SLX9 内核供电电压为1.2 V;I/O 口的电平可以设置为LVTTL、LVCMOS、LVDS 等多种电压标准;内置高性能的时钟管理模块,1 个CMT 包含1 个PLL 和2 个DCM,能进行分频、倍频;XC6SLX9 支持主动模式和被动模式,以及SPI、BPI、JTAG 等多种配置方式。

设计中预留了30 个扩展接口,由双排针引出,其中24 个是FPGA 的通用I/O,3 个3.3 V 引脚和3 个地引脚。串行通信采用CH340G 串口芯片,用于FPGA和PC 机之间的通信。“口袋实验室”拥有2 个4 位共阳极数码管、1 个无源蜂鸣器、1 个八位拨码开关、1个VGA 接口以及10 颗LED 灯和6 个按键,可以满足数字电路基本的实验需要[7-9]。

2 电路设计

2.1 电源电路

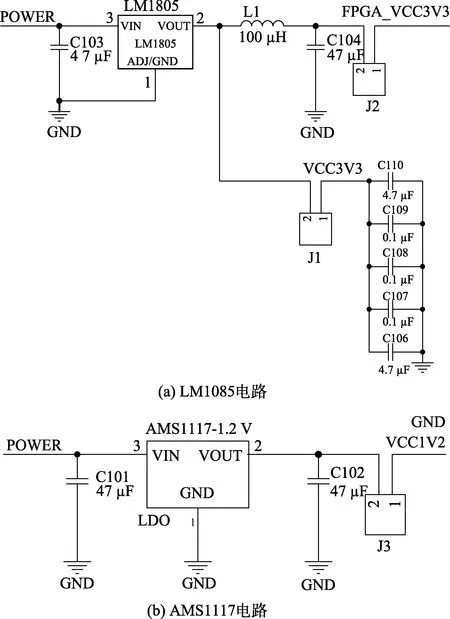

电源系统为整个系统提供能量,是系统的基础。采用LM1085 芯片提供3.3 V 电压,采用AMS1117 芯片提供1.2 V 电压[10]。

考虑到XC6SLX9 的3.3 V 电源和其他外设共用一个电源芯片,为保证其他外设电流突变时不影响XC6SLX9 的正常供电,使用一个功率电感以隔离FPGA 和外设的电源。具体电路设计见图3[11]。

XC6SLX9 对电源的要求较高,电源引脚附近需要多个去耦电容,以减小电源瞬变,保证电源完整性。电源部分还设计有1 颗LED 灯用于指示FPGA 电源是否正常。

2.2 配置电路设计

配置电路一个是使用JTAG 配置的电路,另一个是使用FLASH 的主动SPI 配置电路[12]。

图3 LM1085 电路和AMS1117 电路[11]

2.2.1 JTAG 配置电路

JTAG 配置电路见图4。

JTAG 的主要引脚TMS、TCK、TDI、TDO 经4.7 kΩ电阻上拉,以保护电路。JTAG 引脚在印刷电路板(PCB)上通过14 针2.0 mm 间距的简易牛角座引出。简易牛角座采用防反插设计,以保证JTAG 连接正确。

PROGRAM_B 引脚默认上拉,通过按键接地,可以用于FPGA 的软复位。DONE 引脚上拉,且有LED指示FPGA 是否配置完成。

2.2.2 FLASH 电路

设计所选用的FPGA 基于SRAM 工艺,掉电后不能保存数据,因此在重新上电之后必须从外部的配置存储器加载配置。FLASH 电路见图5(a)。MODE0 和MODE1 的电平决定了FPGA 的配置方式,当MODE0拉高以及MODE1 拉低时,FPGA 使用主动SPI 配置模式。接口电路见图5(b)[13]。

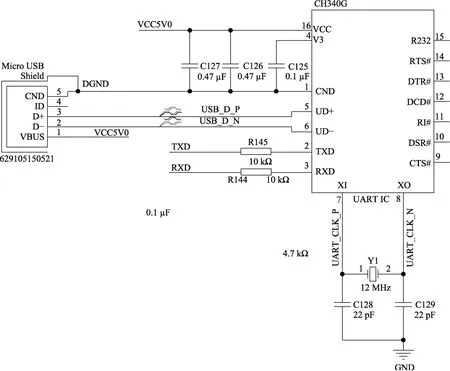

2.3 串口通信设计

选用CH340G 作为FPGA 和PC 机之间通信的转换芯片。CH340G 是常用的USB 转串口的芯片,兼容5 V系统和3.3 V 系统,由于本设计中选用的XC6SLX9属于3.3 V 系统,因此CH340G 的供电电压设置为3.3 V,如果供电电压调整为5 V,则串口通信将发生故障,数据不能通过串口发送至PC 机。串口部分电路见图6。

图4 JTAG 配置电路

图5 FLASH 电路和FPGA 的FLASH 接口电路

2.4 扩展接口设计

为保证“口袋实验室”的扩展能力,在设计时将FPGA 的24 个通用I/O 口通过双排排针在PCB 上引出,可供使用者外接电路。

为了防止FPGA 的I/O 接口接入过高的电压或者通过过大的电流而损坏FPGA,设计中使用双向电平转换芯片TXS0108E 对FPGA 的I/O 口和外部接口进行隔离,以保护FPGA 芯片。

3 实践教学实例

3.1 数码管显示实验

实验要求使用数码管显示时间精度为100 ms 的秒表,最低位数字每100 ms 加1。

3.1.1 实验硬件电路

“口袋实验室”选用的数码管是4 位共阳极数码管,其中公共端使用三极管驱动,其余A、B、C、D、E、F、G、DP 8 个引脚分别和FPGA 的I/O 口连接。电路如图7 所示。

3.1.2 FPGA 代码设计

FPGA 代码设计思路如下:将系统的50 MHz 时钟分频为50 Hz 的逐位扫描时钟和10 Hz 的计数时钟,最低位通过10 Hz 的时钟进行计数,计数使用8421BCD 码表示,并转化为数码管显示的8 位二进制代码输出。由于是共阳极数码管,当引脚公共端高电平,其他引脚为低电平时,对应的LED 才会亮。数码管二进制码的最高位为小数点位。实验仿真及实际运行效果见图8。

由于实际仿真时间过长,因此在仿真时缩短了计数的时间。表1 为BCD 码与数码管二进制码对应表。

图6 串口通信部分电路

图7 数码管电路

图8 数码管仿真时序图与数码管实验实际运行图

表1 数字的BCD 码与数码管二进制码对应表

3.2 蜂鸣器控制实验

实验要求通过编程控制无源蜂鸣器,使之在输入不同频率的PWM 波情况下,发出不同音调频率的声音。

3.2.1 实验硬件电路

无源蜂鸣器的硬件电路设计见图9。

图9 蜂鸣器电路图

3.2.2 FPGA 代码设计

无源蜂鸣器输入不同频率的PWM 会发出不同频率的声音,频率和音调对应见表2。

表2 频率和音调对应表

通过ISE 的Clock Wizard 将50 MHz 的系统时钟频率分频为12 MHz,然后通过计数输出不同的频率,计数的上限值由拨码开关和按键控制,拨码开关用于选择3 个音调,按键用于选择各个音调下的7 个不同频率,以此实现输出不同音调频率的声音。图10 为蜂鸣器控制仿真图。

图10 蜂鸣器控制仿真图

4 结语

结合创新实验人才培养的需求,采用“专业性及综合性强、使用简单灵活、维护便捷、成本低廉”的设计原则,完成了基于FPGA 的数字电路“口袋实验室”的设计。该平台编程简单、调试方便、可移植性较好,具有较强的创新性和实用性[14-16]。

目前,该“口袋实验室”已应用于我校数字电路实验课程、学科竞赛及大学生创新创业培育项目中,并取得良好的效果。以我校自动化和信息工程专业为例,学生通过在“口袋实验室的”学习,增强了学习数字电路的兴趣,提高了数字电路设计水平。在2019年第十六届“挑战杯”上海市大学生课外学术科技作品竞赛中,我校学生的 “基于FPGA 的导盲辅具”项目获得特等奖。在2018 年第三届全国大学生智能互联创新大赛中,我校学生的“小型智能化管道检测维护系统”获得华东赛区一等奖。上述奖项的获得,反过来又促进学生对电路设计的兴趣以及实践能力和创新能力的提升。