五十一进制计数器的设计与仿真实现

龚猷龙

(重庆工商职业学院 重庆九龙坡 400052)

一、设计思路

计数器由计数器、译码器、显示器三部分电路组成,再由555定时器组成的多谐振荡器来产生方波,充当计数脉冲来作为计数器的时钟信号,计数结果通过译码器显示。

我们采用一个十位进制和六位进制来实现五十一进制。十位可以用74ls160芯片来实现六进制,个位可以使用74ls160芯片来实现十位制。实现五十一进制可以用一个十位进制和六位进制来实现。十位可以用74ls160芯片来实现六进制。个位可以使用74ls160芯片来实现十位制。

1.构成六进制计数器可以利用74ls160置零法和置数法来实现。采用74ls160置零法的实现原理:计数器从全零状态开始计数,当脉冲信号的上升沿或者下降沿到来,计入一个脉冲,直至计入6个脉冲后,译码产生低电平信号将74ls160清零,从而得到一个六进制计数器。

2.同理,各位十进制也可以利用74ls160来实现[1]。

二、计数器设计

(一)计数器的原理

计数器其实可以看成是一个加法器。如果把计数的步调设置均匀且间隔为1秒,那计数器又可以看成是一个秒表。因此,计数器产品有很多功能。如果要将计数器设置为任意进制的,那可以按照数字逻辑电路的知识,通过异步复位或者预置数的功能,完成计数状态的重置,以达到实现任意进制计数器的效果。例如,计数器先从0开始计数,直到计数器到达50,计数器再计一次数,则重新回到0。这样,计数器就有五十一个状态,也即是五十一进制计数器[2]。

(二)设计论证

本次设计是五十一进制计数器,需先按照一个60进制计数器来设计,即个位是十进制加法器,十位是六进制,待计数到50,再来一个脉冲信号,则重新将计数结果置零,这样就实现了五十一进制计数器的设计。计数器输出的信号经译码器/驱动器处理之后,再送到数字显示器对应的笔划段,最终显示为五十一进制计数器。

1.555定时器电路:555定时器电路提供一个稳定且准确的方波信号(频率为32768赫兹),确保计数器是均匀计数。

2.分频器电路:分频器电路将555定时器产生的高频方波信号(频率为32768赫兹),经32768次分频后得到低频方波信号(频率为1赫兹),用于计数器按照每1秒钟完成一次计数。分频器实现的功能就是计数器。

3.计数器电路:个位和十位计数器电路构成,而根据设计要求,需选择51个计数状态,即个位和十位计数器为五十一进制计数器。

4.译码器驱动显示电路:译码驱动电路将计数器输出的8421BCD码转换为数码管需要的逻辑取值,同时提供足够的工作电流以保证数码管正常工作。

三、仿真实现

(一)五十一进制计数器电路元件的选择与计算

1.7400四通道两输入与非门集成电路。7400是广泛应用的数字IC之一,它内含4个独立的2输入端与非门,其逻辑功能是:输入端全部为1时,输出为0;输入端只要有0,输出就为1。

2.7447:数码管译码器。7447数码管译码器的主要功能:将二进制BCD码转换为7段LED数码,并通过LED数码译码驱动显示。7447输出的低电平可驱动7段共阳极LED数码管,并显示对应的数字[3]。

3.7段发光二极管显示屏(7段数码管)。

(二)仿真

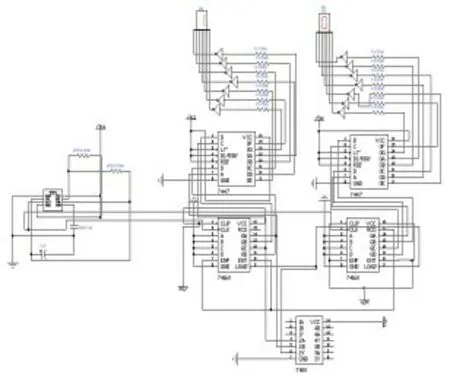

图1 五十一进制计数器仿真结果

采用multisim软件进行仿真,仿真图如图1所示。我们可以看到计数器的变化:从0一直计数,直到50停止。这可以看出实现了五十一进制计数器的功能[4]。

(三)应用拓展

其实,在实际应用中,我们用到五十一进制计数器的场景不多。虽然上面设计的是五十一进制计数器,但如果要设计其他进制计数器,其原理是相通的,同样通过555定时器电路,通过控制计数器的状态取值及改进设计的方法,就可以实现任意进制计数器。

四、结束语

计数器是数字逻辑电路中经常碰到的一种电路,由于其应用十分广泛,在很多教材中会单独提出这种电路,另外还有很多种优化或者改进的电路。然而,对于计数器电路来说,我们需要认真分析设计,掌握计数器的原理及设计方法,并采用仿真软件完成计数器电路的仿真及功能验证。因此,掌握计数器的原理及设计方法是学习数字逻辑电路的基础。