L-DSP片上调试电路的设计与实现

白创,李帆,汪东

(1.长沙理工大学 物理与电子科学学院,湖南 长沙 410114;2.柔性电子材料基因工程湖南省重点实验室,湖南 长沙 410114;3.湖南毂梁微电子有限公司,湖南 长沙 410005)

随着半导体制造工艺的不断进步,芯片的集成度越来越高,实现的功能越来越复杂,使得芯片正确性调试与故障定位的需求难以得到保证[1].同时芯片的快速市场化又使得其研发周期越来越短.因此,可靠的调试手段显得尤为重要,准确、快速的调试方法直接影响到芯片的开发效率与进度[2].

根据通信接口的不同,常用片上调试方法包括基于串口通信、基于BDM 接口和基于JTAG 接口3种调试方法.基于串口通信的调试方法,其功能虽然完善,调试过程也十分简便[3],但因其占用芯片一些引脚资源,存在无法进行自我调试等弊端,使得该方法在某些场合并不适用[4-5].而基于BDM 接口的片上调试技术虽然被业界广泛使用[6],但是没有相关协议支持边界扫描功能,需要开发者自行承担风险.基于JTAG 接口的调试方法是目前包含军事领域在内大部分芯片采用的调试方法,具有良好的灵活性和扩展性且占用较少的引脚资源等特点[7-12].因此本文针对L-DSP 调试需求,设计实现一种基于JTAG 接口的调试电路来完成L-DSP 的调试功能.传统JTAG调试方法需要CPU 传输调试数据,当数据量过大时会占用CPU 大量资源,导致调试效率不高.为提高调试效率,本文在调试电路中增加DT-DMA 模块实现调试数据直接在外设与内存之间传输,缩短调试周期.

1 片上调试电路设计方案与实现

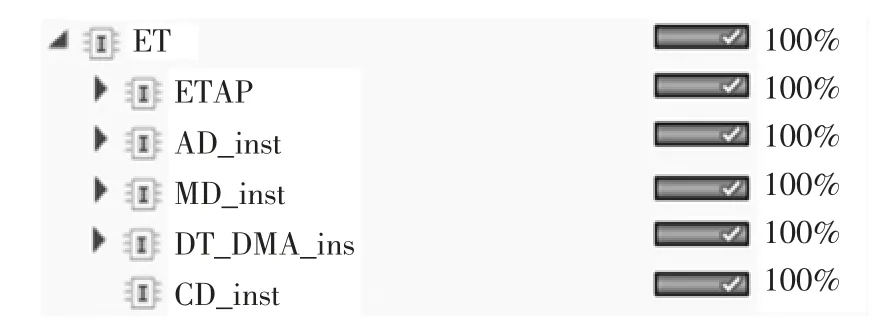

在调试模式下,调试电路(Emulate and Test,ET)通过来自仿真器的串行输入接收调试指令,经过串并转换、异步时钟处理、指令译码等操作来完成相应的调试工作.图1 为ET 总体设计框架图,包括ET调试端口、芯片存储访问、流水线控制、事件分析、DT-DMA 5 个部分,其中ET 调试端口提供整个调试系统的控制机制,是调试软件通过JTAG 接口进行系统访问的入口;事件分析模块提供包括硬件断点、数据、地址观察点,以及一些其他重要参数的统计等功能;DT-DMA 模块提供调试数据传输通路,调试数据导入、导出芯片时采用此条通路,不占用CPU 资源.

图1 ET 总体设计框架图Fig.1 Framework of ET

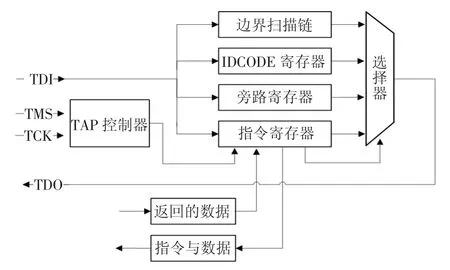

1.1 ET 调试端口

ET 调试端口是ET 的核心控制部分,是符合IEEE 1149.1 协议标准[7]并扩展的仿真调试端口,ET结构如图2 所示.TAP(Test Access Port)控制器是一个同步有限状态机,掌握着整个JTAG 协议的状态,其状态迁移如图3 所示,通过TDI、TMS、TCK 端口接收调试软件发出的指令并进行译码,发送具体命令给指定的模块去执行,通过TDO 端口输出芯片返回调试数据给调试软件.

图2 ET 调试端口结构图Fig.2 Structure of ET debug port

图3 JTAG 状态机状态迁移图Fig.3 State transition of JTAG state machine

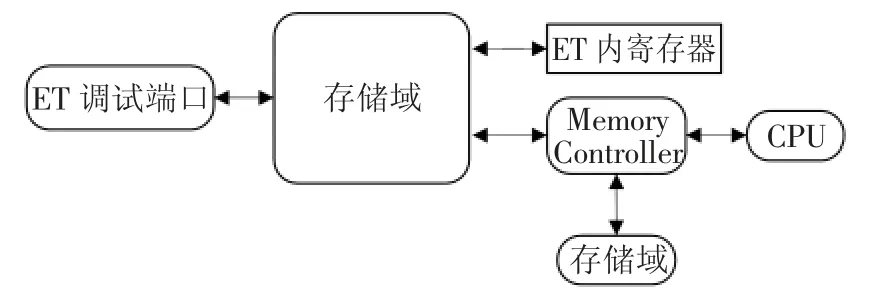

1.2 存储访问与流水线控制

存储访问部分提供调试软件访问芯片存储的接口,实现对芯片内外存储空间以及特殊编制寄存器的读写,使除开受保护的地址区域外其余存储资源对外是透明的.整体结构如图4 所示,存储访问模块将ET 内寄存器空间和其他地址空间(Memory 存储和CPU 寄存器)进行区分,避免了即使访问ET 内部寄存器也需要绕到存储控制器的情况,提高工作效率.

流水线控制部分实现调试软件对处理器流水线的精确控制,指令包括暂停、运行、复位CPU、单步执行指令等.直接将来自ET 调试端口的流水控制指令进行译码,产生相应的控制信号发送给处理器.调试模式下,在控制CPU 的同时会发出信号去控制相应的外设,避免外设出现失控的情况.

图4 存储访问结构图Fig.4 Structure of storage access

1.3 事件分析

事件分析部分实现了硬件断点、硬件观察点、参数统计等功能.本文调试电路提供两个硬件断点、一个硬件观察点和一个用于统计重要参数的计数器.硬件断点用于监控程序指令地址,设置一个硬件断点寄存器用来保存目标指令地址,将程序地址总线接入事件分析逻辑内与目标值进行比较,程序运行后当程序地址总线上出现目标值后ET 立即发出流水线暂停信号.硬件观察点用于监控数据总线与地址总线上的值,行为与硬件断点一致,工作流程如图5 所示.参数统计功能实现了对目标地址、数据等一些重要参数出现次数的统计;搭配硬件断点/观察点,实现了对从程序起始到硬件断点/观察点处指令运行周期的统计.

图5 硬件断点/观察点工作流程图Fig.5 Hardware breakpoint/watchpoint work flow chart

1.4 DT-DMA

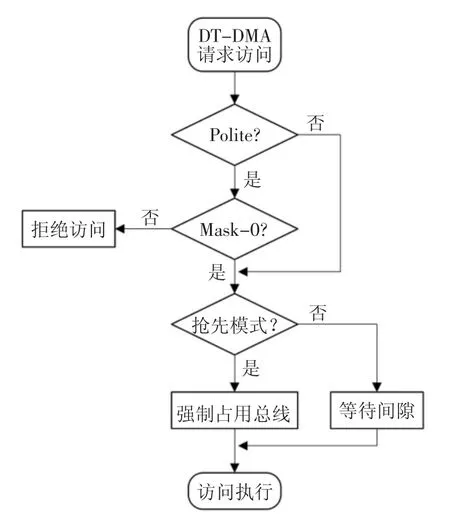

DT-DMA 是一条专门为调试数据设计的传输通路,用于代替CPU 对调试数据进行传输,并且在数据传输过程中不会影响CPU 的正常运行.DT-DMA有两种方式实现调试数据的传输,一是从开始地址传输一定数据量的方式;二是从开始地址传输至结束地址.DT-DMA 接收到请求后会依次对存储进行访问,数据传输不占用CPU 资源.

DT-DMA 传输机制能被ET 或CPU 分时来控制,其请求处理流程如图6 所示,在Polite 模式下仿真器的请求会受到调试掩码寄存器的影响,掩码为1 时无法实时传输调试数据;Rude 模式下忽视掩码寄存器.DT-DMA 有抢先和非抢先两种工作模式,抢先模式下,DT-DMA 使用总线的优先权高于CPU,会打断CPU 强制占用总线资源直到数据传输完成;非抢先模式下,DT-DMA 利用CPU 不使用总线的间隙进行数据传输.

图6 DT-DMA 请求处理流程图Fig.6 Process for handling a DT-DMA request

2 ET 逻辑功能验证与DC 综合

2.1 ET 逻辑功能验证

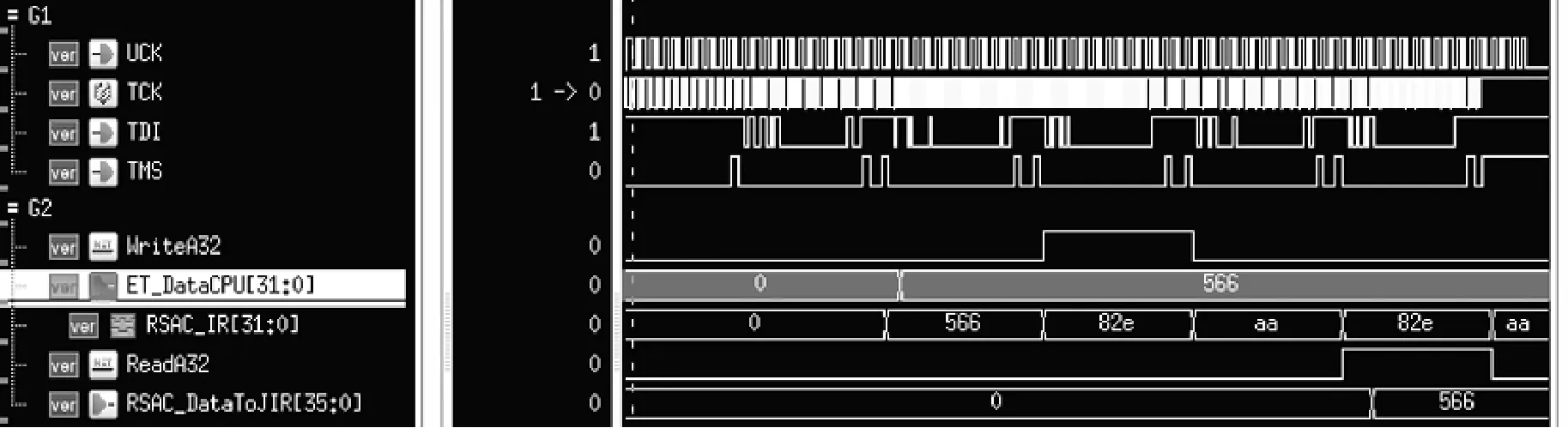

采用Cadence 软件中的NC-Verilog 仿真工具,根据JTAG 协议,针对调试功能编写相应的测试激励输入到调试电路逻辑,用Debug 工具Verdi 查看仿真结果,用IMC 仿真工具查看代码覆盖率.

图7 逻辑功能验证图Fig.7 Function verification diagram

图7 为功能仿真示意图,示例为ET 内寄存器读写,将目标数据给到ET_DataCPU 寄存器中,在写使能有效时将数据写到指定地址(仿真中数据为0x566,地址为0x82e);读数据时,给出读指令,在确认读数据信号有效后把返回的数据给到RSAC_DataToJIR 寄存器中,图7 中可以看出寄存器读写结果均正确.同理,在相同环境下依次验证其他调试功能,调试功能均正确.所有调试功能仿真完成后对代码覆盖率进行统计,图8 为屏蔽了toggle 后的代码覆盖率结果,结果表明覆盖率达到100%.

图8 代码覆盖率Fig.8 Coverage

2.2 DC 综合

采用Synopsys 公司的Design Compiler 综合工具,在0.18 μm CMOS 工艺下对本文调试电路进行综合.综合时系统时钟频率为150 MHz,调试时钟频率为10 MHz,综合后面积开销为167 234.76 μm2,功耗为8.89 mW.

3 FPGA 原型验证

FPGA 原型验证环境如图9 所示.将L-DSP 全芯片代码固化至FPGA,采用TI 公司的CCS 调试软件作为仿真工具,通过XDS 仿真器与FPGA 相连,针对每种调试功能,依次进行验证.验证同时,将JTAG 信号用逻辑分析仪捕获备份,经过处理后返回编译环境.

图9 FPGA 原型验证环境Fig.9 Environment of FPGA prototype verification

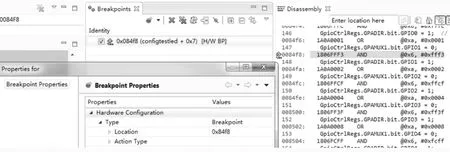

图10 为硬件断点功能验证示意图.在调试模式下,新建硬件断点(图中为0x84f8),运行后CCS 显示程序停在了指令地址为0x0084f8 的地方,与预期结果相同.同理,针对所有调试功能依次进行验证,结果表明调试功能均正确.

图10 硬件断点功能验证Fig.10 Verification for hardware breakpoint

DT-DMA 数据传输速度验证部分,分别用CPU和DT-DMA 两种方式从调试软件传输同一段数据至FPGA,将逻辑分析仪抓取到的JTAG 信号进行整理,再用Debug 工具Verdi 查看波形,找到这段数据传输始末位置,对比两种方式所用传输时间.图11展示了5 次传输不同数据量的实验,统计了两种数据传输方式所用的时间,统计结果表明DT-DMA 所用传输时间明显少于CPU.因为调试数据首先会被仿真器通过JTAG 串行通信传输至ET,再由两种传输方式传输至指定区域,所以数据传输速度会受到JTAG 串行通信的限制,但实验表明,DT-DMA 平均所用时间仍是CPU 传输的32.15%.

图11 两种传输方式时间对比Fig.11 Time contrast of two methods

4 结论

针对L-DSP 的调试功能,本文设计了一种复用JTAG 接口的调试电路,能够有效、快速地实现存储空间访问、流水线控制、硬件断点/观察点、事件统计等调试功能.同时通过引入DT-DMA 模块实现调试数据在外设与内存之间直接传输,经FPGA 原型验证,调试数据传输速度是CPU 传输的3 倍,有效提升了调试效率.