基于VPX平台的数字波束形成新架构

白晓慧

(中国电子科技集团公司第38研究所,安徽合肥230088)

0 引言

数字波束形成(DBF)是在原来模拟波束形成原理的基础上,引入数字信号处理方法后建立起来的一门雷达新技术[1]。它是针对阵列天线,利用阵列天线的孔径,通过数字信号处理在期望的方向形成接收波束。这种技术充分利用了阵列天线所检测到的空间信息,可以方便地获得超分辨和低副瓣的性能,实现波束扫描、自校准和自适应波束形成等。原则上讲,数字波束形成技术对雷达系统的发射和接收都可应用,但是在接收状态下才真正体现出它的特点:1)同时形成多个可控波束,以适应在特定的干扰环境下对多个目标进行探测、跟踪;2)波束位置的无惯性捷变,实现重复周期内的波束时分控制和功率匹配;3)天线方向图可以实现有源干扰的自适应置零,从而有效抑制干扰等。DBF技术的成功应用必将对现代雷达技术的发展产生重大影响。本文充分利用FPGA资源丰富、处理灵活的优势以及PPC实时多核的特点,在基于VPX开发平台上进行了DBF的工程实现。

1 数字波束形成基本原理

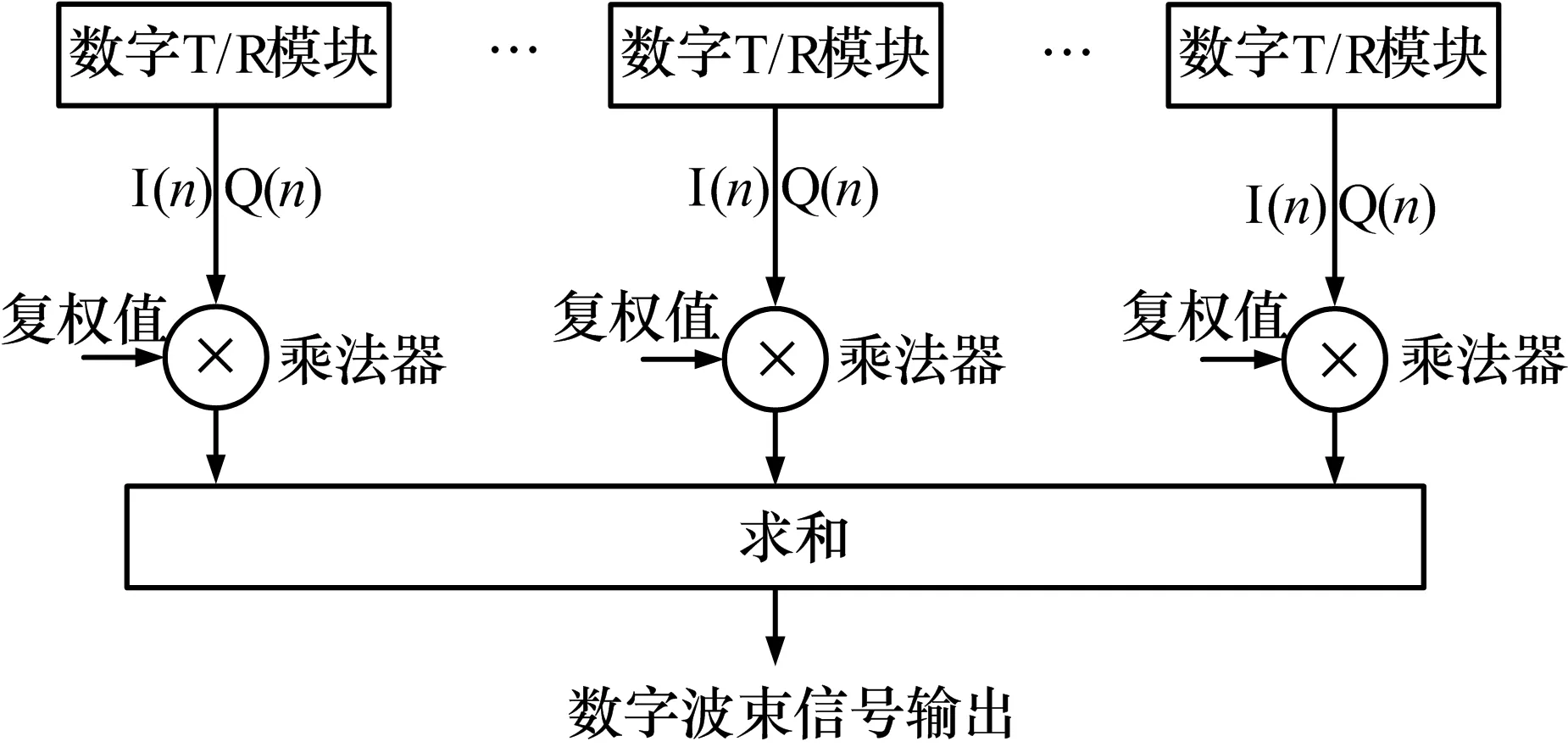

数字波束形成就是用数字处理方法[2],对于某一方向入射信号,补偿由于传感器在空间位置不同而引起的传播波程差导致的相位差,实现同相叠加,从而实现该方向的最大能量接收,完成该方向上波束形成。图1示出了数字波束形成的原理方框图。

图1 数字波束形成原理方框图

在数字阵列雷达中,阵列天线的每一个阵元都接有一个数字T/R模块,数字T/R模块具有独立的接收通道和发射通道[3]。每个阵元接收的射频回波信号送至数字T/R模块的接收通道,经过低噪声高放、下变频转换成中频信号,对中频信号进行A/D采样和数字鉴相,最后输出正交的I/Q数字信号。对每个T/R模块接收通道输出的I/Q数字信号分别进行复加权和求和运算处理,形成所要求的波束。

2 基于VPX平台的DBF新架构

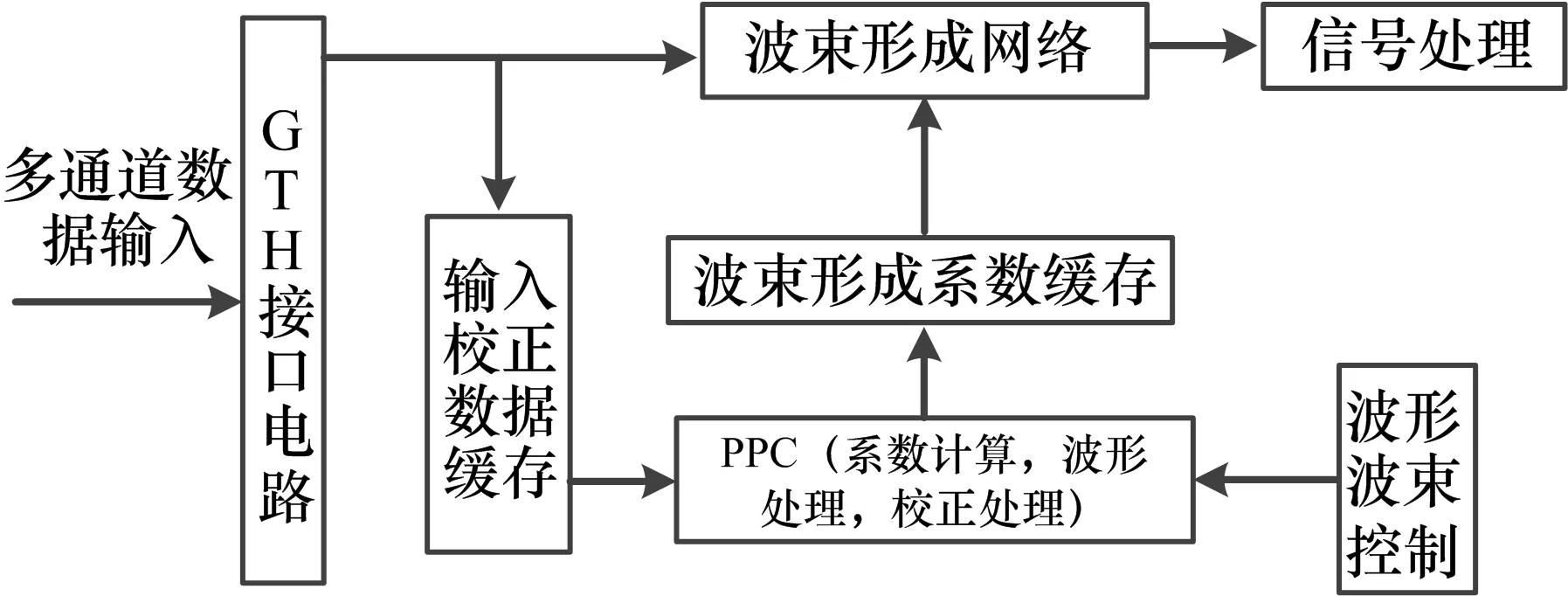

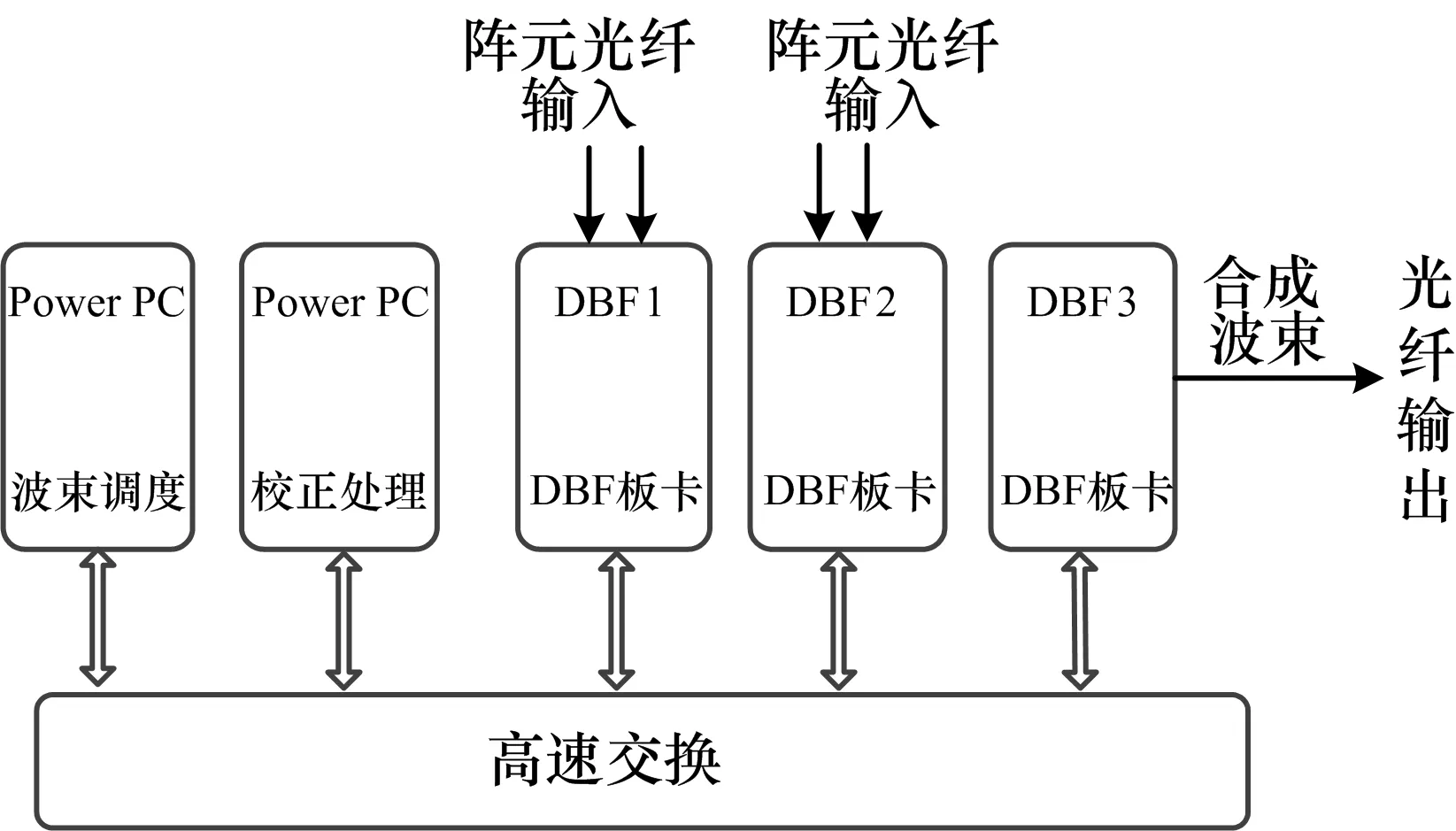

数字波束形成设计采用FPGA+PPC的VPX架构的信号处理设备。数字波束形成算法的核心主要包含接收权重计算和波束权重合成处理2个模块。其中,接收权重计算由PPC通过软件编程实现,主要包括权重相位计算、幅度加权计算和自适应抗干扰权重计算等功能;波束合成的过程通过FPGA实现,输出对应的波束数据,如图2所示。

图2 数字波束形成实现框图

2.1 DBF处理器硬件平台

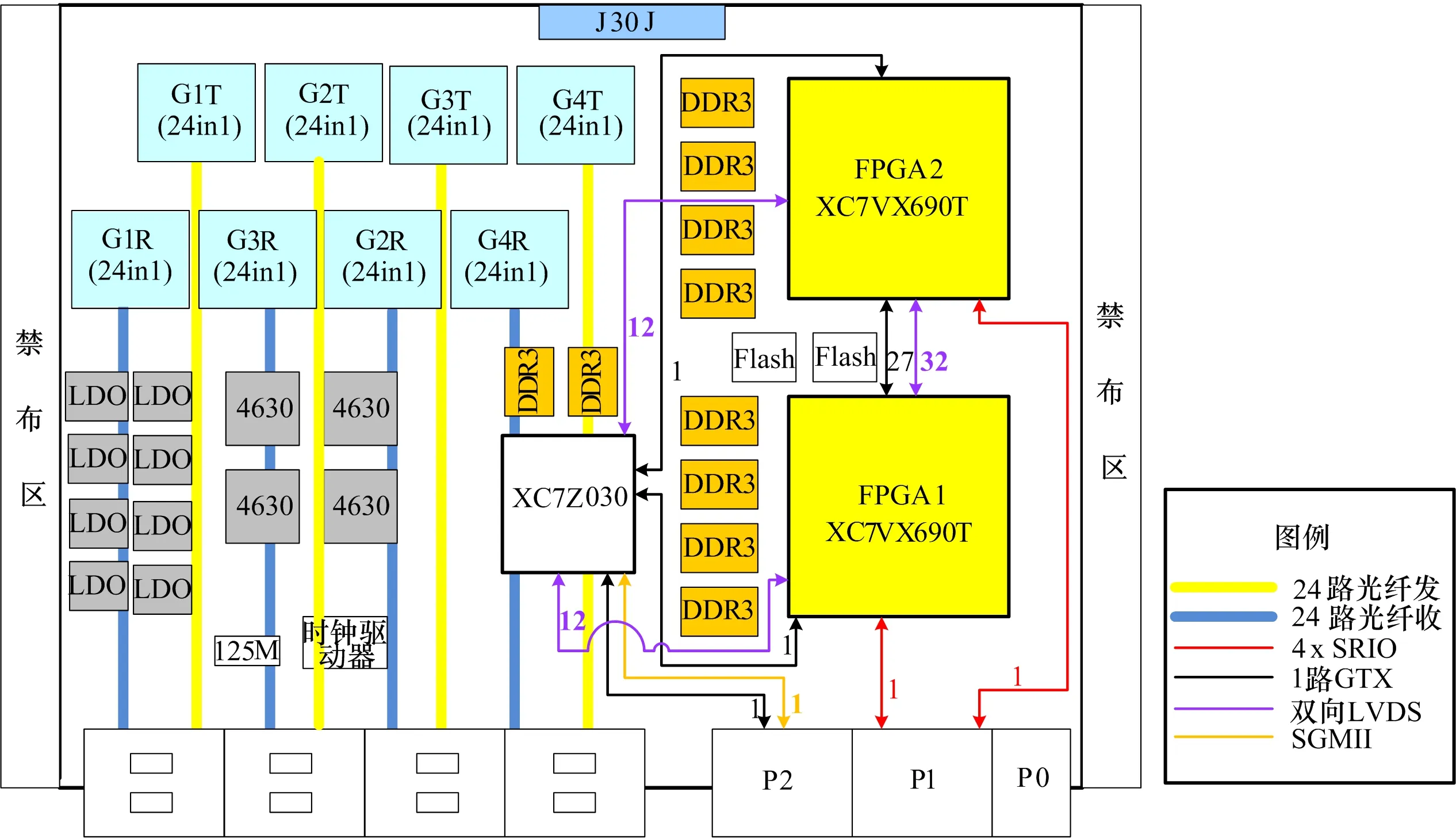

DBF板中有2片XC7VX690T的FPGA。该FPGA内部具有3 600个乘法器单元和80个GTH高速收发器,保障了任务的资源需求。每片FPGA外接48通道光纤模块,每路数据率不低于10 Gbps。DBF分机中DBF处理模块的处理能力决定了设备量的大小,DBF处理模块包含2片Xilinx V 7 690T大规模FPGA、8个24合1光模块(4收4发)。96通道DBF模块通过板载的96路光纤通道,接收前端宽带采集模块传输过来的AD采样量化后的信号数据,通过光纤将DBF处理后多波束I/Q数据输出给服务器。图3为VPX接口Xinlix-DBF板资源组成示意图。

该模块主要实现波束形成器的功能,完成校正模式以及正常工作模式下的数据采集,与天线阵元DAM之间的接口控制和信号处理服务器后端的接口控制等功能。波束形成实现整个阵面发射波束控制和接收数字波束形成。

2.2 PPC模块处理器

PPC模块处理器是一款符合VITA 46规范的6U VPX信号处理版,板载2颗高性能T 4240芯片的12核24线程的PowerPC处理器。每颗处理器独享6 GB DDR3L SDRAM,采用Serial RapidIO 2.1内部和外部数据交换、VSILIB AltiVec运算库,以ReDes系统开发和调试平台,采用风冷散热设计。

恩智浦公司的T 4240时本板主要的计算处理单元。外部系统时钟为100 MHz,为处理器内部Platform总线和外部的DDR3L SDRAM提供600 MHz的工作时钟,为处理器提供1 500 MHz工作时钟。T 4240运行VxWorks操作系统,支持12核24线程SMP工作模式。

每颗T 4240处理器有3个独立的DDR3内存控制器,每个控制器外接64位宽、2 048 MB DDR2 SDRAM,支持ECC校验。全板共有12 GB DDR3L SDRAM内存,由24片16 bits×32 Meg×8 banks的内存芯片组成。

每颗T 4240处理器的总线上都配有一片NOR FLASH芯片,容量为256 MB,位宽为16位,可用于存储boot loader、操作系统和应用程序等。

程序开发使用风河公司的Work Bench 4.0,这是一款基于Java的仿真开发软件。WorkBench 4.0集成开发软件上可以运行VxWorks嵌入式操作系统。

3 基于VPX平台的DBF的工程实现

3.1 设计思路

项目中,基于VPX平台的DBF处理过程,首先需要建立PPC与FPGA之间的RapidIO通路,通路建立完成后,PowerPC与FPGA之间就可以通过DMA传输方式进行数据的交互。在这种传输机制的基础上,PowerPC从波束调度通过RapidIO方式读取波位包信息,在PowerPC内部进行自适应权值的计算和控制码的计算。然后将权值通过RapidIO传输给FPGA,FPGA将权值缓存,控制码通过光纤传送给DAM之后,进行数据采集,采集到的数据和缓存的权值进行波束合成,最终将合成的结果通过RapidIO总线发送给信号处理机箱。DBF的工程实现如图4所示。

图3 VPX接口Xinlix-DBF板资源组成示意图

图4 DBF工程实现图

3.2 DBF权值计算

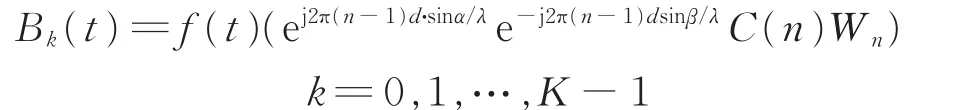

对于某一方向的数字波束形成要完成下列计算[4]

式中,f(t)为目标接收信号,k为波束号,d为相邻阵元的间距,λ为发射载波波长,α为目标信号相对天线阵面发线的入射角,n为第n个通道,N为天线阵面上垂直向排列的阵元数,W为加权系数,C为校正系数,β为波束指向。

可以看出,当满足α=β时,该波束接收到的信号最大,其他方向的波束信号幅度下降。影响波束形成加权系数的因素有以下几个方面:接收波束的空间角度;波束指向系数;对应频点的校正系数以及内外场差系数;窗函数。

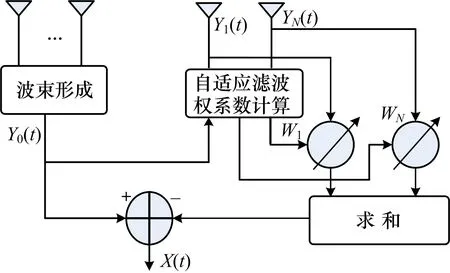

下面着重介绍抗干扰自适应波束形成权重计算。图5给出了自适应抗干扰处理框图。自适应处理器根据主、辅通道接收的信号计算出一组权系数,调节辅助通道的幅度与相位,从而在有源干扰方向自适应形成零点,达到抑制有源干扰的目的。

图5 抗干扰自适应波束权重计算

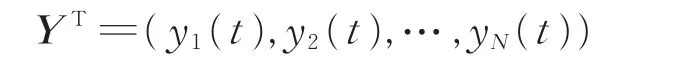

图5中y0(t)表示在t时刻主天线的接收信号,y1(t),y2(t),…,yN(t)为各辅助天线接收信号,N为辅助天线数。t时刻辅助通道接收电压矢量表示为:

由相应算法得出的最优权值矢量表示为:

根据最优化算法,自适应权值为:

式中,R0=E(X×y*0(t)),表示主通道与辅助通道的互相关矩阵。R=E(Y×YH)表示各辅助通道间的协方差矩阵。

同时对主辅通道进行采样,然后形成互相关矩阵和协方差矩阵,从而求出自适应权值,调节辅助通道的幅度与相位,再与主通道信号进行叠加,完成对消运算,达到抑制有源干扰的目的。

3.3 接收校正

接收通道幅相一致性是影响DBF性能的关键因素[5-6]。实际工程应用中,要求DBF处理采用多个接收通道,各个通道之间的幅度相位一致性和通道本身的平稳性是DBF实现的关键。实际上采用的是用测试信号对通道进行校正,以此对外部回波进行波束形成得到各个不同波束指向的接收信号。

数字波束网络校正主要测量通道间的相对延迟和各个频点上幅相误差。内校正源和外校正源发射测试信号,内校正源通过功分器同时耦合到具体列阵元上,所有接收通道在FPGA中根据采集触发信号,同时采集校正数据,在PPC中通过计算校正数据的幅度、相位和时延等信号参数来完成校正系数的计算。

系统控制内/外校正源发射测试信号,对整个工作频段按照一定的步进进行扫描,计算出每一频点的通道间幅相误差。

4 结束语

数字波束形成技术具有很多优点:可同时产生多个独立可控的波束而不损失信噪比;波束特性由权矢量控制,灵活可变;天线具有较好的自校正和低副瓣能力等。更为重要的是,由于在基带上保留了天线阵单元信号的全部信息,因而可以采用先进的数字信号处理理论和方法,对阵列信号进行处理,以获得波束的优良性能。基于VPX平台的数字波束形成系统,遵循通用化、系列化、组合化设计原则,以FPGA和PPC为基本平台,具有软件化、开放式架构,满足新一代雷达信号处理系统的技术发展要求。■