IPM模块抗ESD能力研究

冯宇翔

广东美的制冷设备有限公司 广东顺德 528311

关键字静电;智能功率模块;IGBT

1 引言

环境中存在静电,这种静电电压从几百伏到几千伏不等,甚至更高,如果没有任何静电保护结构,集成电路在存储、运输以及使用工程中很容易被静电损伤。静电放电(ESD)是两个靠近的带电体之间电荷再次平衡的过程,当带静电的人或物体与MOS器件的引脚接触,并通过器件向地或者其他物体放电时,高电压及其产生的大电流可能造成器件的损伤。ESD保护结构能将高压静电转化成瞬态低压大电流,最终将电流泄放,从而达到保护集成电路的目的。工业调查表明由ESD造成的芯片失效占失效总数的50%左右,所以ESD对提高芯片的可靠性至关重要。[1,2]

2 实验

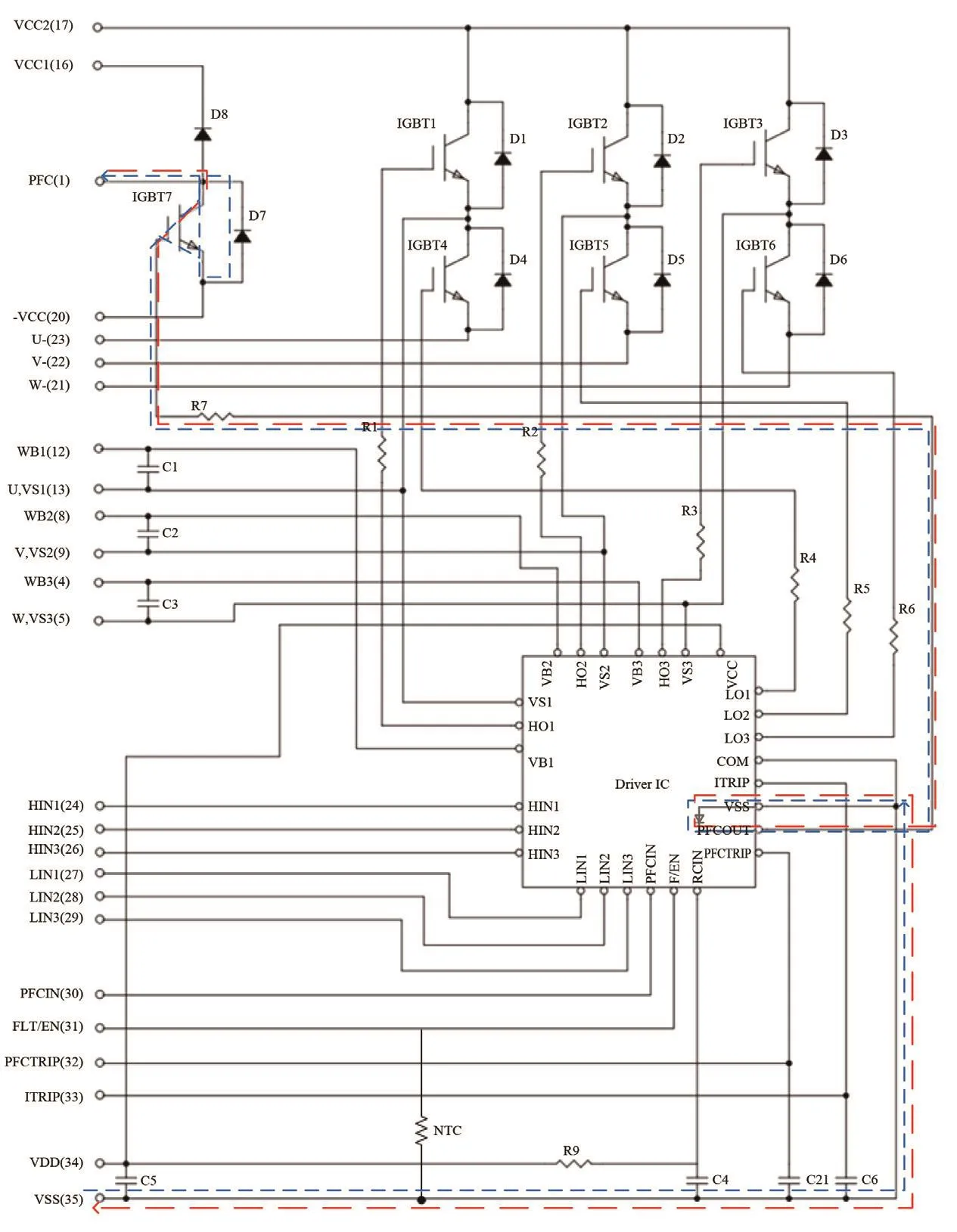

通过静电放电路径分析和静电实验两种方式分析IPM模块静电失效点。图1是本文分析的智能功率模块的原理图。静电放电测试设备采用手动ESD-606静电放电发生器。检查判定设备为TEKTRONIX370B晶体管图示仪。

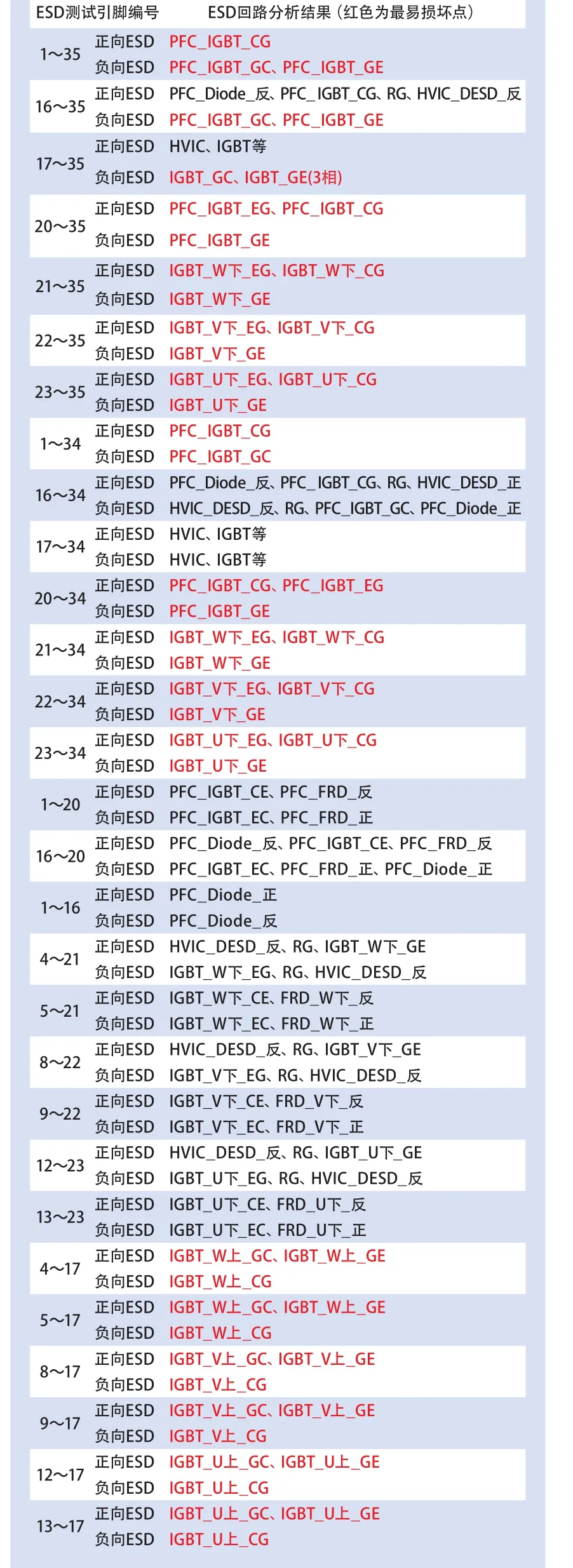

对两两管脚间的电路路径共220种情况进行回路分析的静电实验。图1中所示了管脚1-35间的静电回路。表1中红色字体为模块最易损坏点。

其中两两引脚静电回路全部集中在HVIC中的情况有:24~33,25~33,26~33,27~33,28~33,29~33,30~33,31~33,32~33,24~32,25~32,26~32,27~32,28~32,29~32,30~32,31~32,24~31,25~31,26~31,27~31,28~31,29~31,30~31,24~30,25~30,26~30,27~30,28~30,29~30,24~29,25~29,26~29,27~29,28~29,24~28,25~28,26~28,27~28,24~27,25~27,26~27,24~26,25~26,24~25,4~35,5~35,8~35,9~35,12~35,13~35,24~35,25~35,26~35,27~35,28~35,29~35,30~35,31~35,32~35,33~35,34~35,4~34,5~34,8~34,9~34,12~34,13~34,24~34,25~34,26~34,27~34,28~34,29~34,30~34,31~34,32~34,33~34,4~5,12~13,8~9。这些静电测试中全部未发生静电失效。

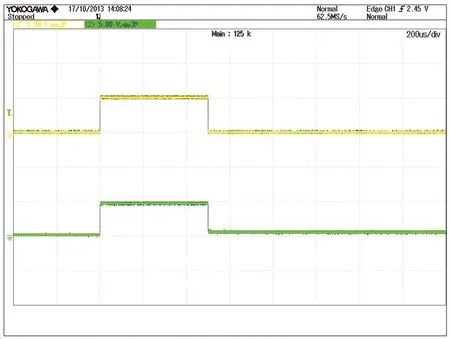

为了验证在IPM某两个引脚上打ESD时,是否会在IGBT的栅极产生ESD电压,在未封装的IPM引脚上打ESD,监测IGBT的栅极电压。实验结果发现理论分析与实验结果一致。如图2所示用信号发生器在IPM引脚输入5 V方波,可以在IGBT栅极产生4.6 V左右的方波。

3 结论

从理论分析和实际测试发现,IPM ESD测试过程中,静电会直接作用于IGBT的栅极,因此IPM ESD水平和内部IGBT ESD水平有直接关系[3]。对于高压引脚的ESD测试,实际是对内部IGBT的ESD测试。目前国际标准、行业标准和企业标准的规格书中都没有规定IGBT的抗ESD水平。另外,市场上的IPM产品的抗ESD水平2000 V也只是IPM中HVIC部分水平,因此对IPM的抗ESD水平大于2000 V的规定仅限于低压引脚部分,高压引脚部分抗ESD能力应重新制定合理的测试标准[4,5]。对于IPM的研发或选型应重点关注高压管脚的抗ESD水平。

图1 本实验所用智能功率模块原理图及管脚1-35间静电回路示意

表1 ESD测试中回路分析结果

图2 IPM引脚输入电压对IGBT栅压的影响,绿色线为IPM引脚上的输入电压,黄色线为监测到的IGBT的栅极位置的电压