基于Matlab的信号处理模块的FPGA快速开发

张佳琪 文腾飞 李凉海 张振华

摘要:介绍了基于Matlab的Simulink开发工具进行FPGA自动代码生成的过程。在信号处理领域,FPGA的开发存在开发周期长、开发成本大及灵活性差等问题,借助Simulink工具完成FPGA的快速开发,在完成Matlab仿真的基础上,搭建了合成孔径雷达后向投影算法模型,得出了模型结果,并将其与Matlab仿真结果进行对比,分析了自动生成FPGA代码的成本,验证了基于Matlab的FPGA开发的有效性。

关键词:信号处理;FPGA代码自动生成;后向投影算法

中图分类号:TP391文献标志码:A文章编号:1008-1739(2020)11-60-3

0引言

近年来,FPGA已经成为高性能数字信号处理系统的关键元件,具有实现高性能并行算法的能力,是构成高性能可定制数据通路处理器的理想器件。然而FPGA的开发受到以下限制[1-3]:①软件开发人员不熟悉硬件设计;②基于并行硬件系统的并行程序设计与基于Matlab仿真的串行程序设计有很大的不同。对此,MathWorks公司对Matlab进行高级开发,实现从Matlab到硬件描述语言的直接转换。开发人员利用Simulink模块进行算法模型搭建,将模型进行定点化设计后利用HDL Coder将模型转换为需要的硬件语言。

1传统FPGA开发的弊端

传统的基于硬件描述语言的FPGA硬件设计开发过程需要编写大量代码,工作量大,且需要系统设计师、硬件工程师和软件工程师协同工作,导致需要的设计人员多、开发周期长,且随着软件代码的更改,硬件语言需要重新进行时序调试与测试,开发的可靠性差。

近年来Xilinx开发的System Generator软件能够解决上述问题,实现由软件到硬件描述语言的完美转换,但其开发的局限性较大,且通过模块转换成的代码可读性较差,对于硬件设计人员来说可更改性较差,因此本文选用MathWorks公司自行开发的从Matlab仿真到Simulink建模,再到可自动生成Verilog或者VHDL代码。

2合成孔径雷达BP算法原理

文献[4-5]分析了后向投影(BP)算法的流程,算法主要分2个部分:①原始回波数据进行距离脉压的过程,采用文献[6]的方式生成;②寻址与投影过程,主要采用状态机的方式编写,2个过程需按照顺序执行,总体设计框图如图1所示。

图1中,,分别代表第个方位向网格点数和第个距离向网格点数,代表第个脉冲回波。本算法的成像网格共有256×70个像素点,因此和的范围是1~70,的范围是1~256。输出RES代表了成像点(,)的成像结果。根据BP算法的基本原理和步骤,基于Verilog HDL的总体思路如下:

State 0:初始状态下若,均为1,则跳到State 1。

State 1:在State 1中主要进行成像点与各脉冲之间延时的计算,并完成单个成像点在各脉冲的回波散射响应相干叠加。,不变,从1加到70,当=70时,表示得到了该成像點在所有通道回波中的响应幅值,跳到State 2;

State 2:根据程序网格点与各脉冲之间距离得到散射系数,并将散射回波响应与散射系数进行乘叠加,跳到State 3;

State 3:将成像点在所有通道的响应幅值全部叠加完成,将的值赋给,完成对(,)点的成像。此时判断和的值是否已遍历整个成像区域。若=70且=256,说明已经对最后一个成像点完成了成像,回到初始状态;否则,若=70且<256,说明己经完成整个成像区域第行的最后一个成像点,下一个需要成像的是+1行的第一个成像点,故令= +1,=1,跳回State 1对下一个成像点进行成像。否则,若<70,说明还没有对第行的所有成像点完成成像过程,令= +1并跳回State 1,继续对下一个成像点进行成像,循环可以完成对256×70像素成像区域的成像。

3利用Matlab完成BPA的FPGA模块设计

3.1数据源产生模块

原始回波数据使用经过下变频和8 bit量化后的信号完成,该回波数据可以从Matlab中得到。原始回波数据构成了一个256×70的矩阵,共17 920个数据,这些数据需要被调用进行距离脉压,由于矩阵是一个256×70的矩阵,在Simulink仿真中需要将它转换为一个1×(256×70)的一维向量,采用Matlab命令为:B=reshape(,1,256×70)。

3.2距离脉压模块

SAR发射信号为线性调频信号,基于线性调频信号的脉冲压缩可以通过匹配滤波处理来实现,其原理见文献[4],该文献指出Xilinx FPGA的FFT的IP核的流水线Streaming I/O结构有很好的数据吞吐能力。

comp_mult模块完成频域脉压的复乘功能,为了提高复乘精度首先通过提前运算得到参考函数值;采用将其存入ROM的方式,直接从ROM中提取参考函数值的方法确保匹配滤波的准确性,输入的参考函数为14位有符号小数,分别将实部与虚部相乘得到输出结果为32位有符号小数。

脉压结果为res_PC,在寻址模块会被反复调用,将其存储到一个双端口RAM中,深度为17920,写入地址为1~17920。

3.3延时计算与寻址模块设计

延时计算与寻址模块实现的功能是图1的遍历与查找脉压结果完成乘累加模块实现算法。

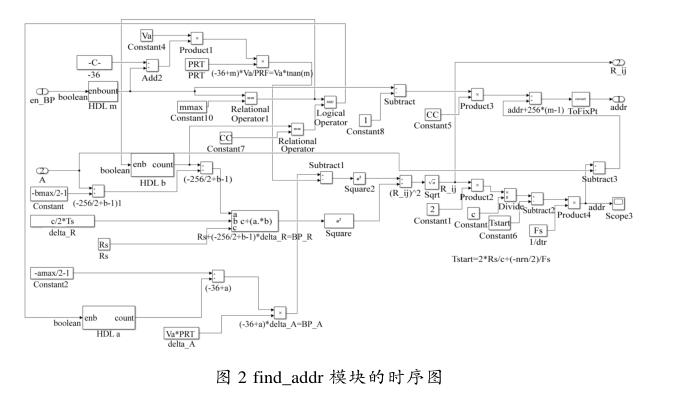

在一步一停假设下[7],计算网格点(,)到每一个雷达载机的延时,在Matlab中的具体实现方式为=sqrt((R( )).^2+(A( )-tnan( )×V ).^2),跟据addr =1 024×( -1)+p/Delta_R得到距离脉压后数据的地址,读取双端口RAM对应地址的脉压数据。该过程的时序为图2所示的find_addr模块,通过控制3个HDL counter的计数完成,,的遍历过程。

4仿真结果

为了清晰地看到模型结果,回波数据采用1个点目标回波。首先将结果显示在scope中,如图3所示,然后将其保存到Matlab的workspace中,结果如图4所示,Matlab仿真结果如图5所示。将Simulink仿真结果与Matlab结果相比较得到误差:实部相对误差在±4%以内,虚部相对误差在±3%以内精度相近,且速度满足要求。存在误差的原因是进行Simulink仿真时对小数部分进行了取整,且模型运算过程中为了节约资源会对一些模块位数进行转换,使数值有所近似。

利用HDL code工具首先进行各个模块的HDL code检查,将全部模块进行HDL Model Checker之后便可以将模型转换为所需要的硬件语言,生成Verilog代码。

5結束语

采用MathWorks公司提供的正版Matlab工具自带的Simulink可以很方便地完成所需的通用数字信号处理模块,该方法简单、有效,而且能够根据Matlab代码的更新灵活地对模型进行更改与测试,避免了传统FPGA设计开发中复杂的时序测试,降低开发周期,提高了系统工作的可靠性。这一技术在算法实现方面无需花费太多时间在硬件语言代码编写与调试,既节约了开发成本又能提高开发效率,具有很好的工程应用价值。

参考文献

[1]江霞.在Matlab中实现FPGA硬件设计[J].国外电子元器件,2005(4):4-6.

[2]花良发,万士保,魏祥生.基于Matlab设计信号处理FPGA模块[J].信息技术,2010,34(10):41-44.

[3]牛斌凯,雍少为,张建,等.基于System Generator开发数字信号处理系统[J].舰船电子工程,2010,30(1):129-132.

[4]张明昊.探地合成孔径雷达成像算法及实现[D].哈尔滨:哈尔滨工业大学,2016.

[5]李浩林.机载SAR快速后向投影成像算法研究[D].西安:西安电子科技大学,2015.

[6]李翱,于勇,褚超,等.基于FPGA的高效脉冲压缩技术工程应用研究[J].遥测遥控,2017,38(2):13-21.

[7]保铮,邢孟道,王彤.雷达成像技术[M].北京:电子工业出版社,2005.