电致发光屏的低损耗开关电源驱动技术研究

犹元彬,何志毅

(桂林电子科技大学信息与通信学院,广西 桂林 541004)

引言

在当前LED作为主流照明光源的技术背景下,电致发光(EL)器件为轻薄面光源、柔性可弯曲的特点,同时材料制备技术成熟,亮度高、寿命长和工作温度范围广[1],可制成面光源铺贴于弯曲表面,也可制作成连续的线状光源,适用于室内外装饰标识和广告等照明,显示出与LED光源不同的特色[2]。采用粉末电致发光材料易于制作成无机电致发光器件,可用于照明领域,具有与LED光源不同的电气特性,需要交流高压驱动。在设计时除考虑驱动电路和负载电致发光屏的电气参数之外,还应对这种新型照明光源的电学特性及其驱动电路之间的匹配予以重视。

无机粉末电致发光器件结构为发光粉薄层包夹在两侧的介质膜和电极层之间,在两侧电极层所加的电场作用下发光层内部电子被加速后碰撞发光中心发出可见光[3]。因此电致发光屏表现为容性负载,对它驱动的交流开关电源电路中,晶体管由截止到导通的开关切换期间对电致发光屏充/放电的瞬间电流就会很大,可达到几十到100 A的电流,造成晶体管开关损耗大温升高,也很容易烧毁开关晶体管,因而散热条件要求也很高,开关电路的可靠性因此难以保证。市场上一般驱动电源都需要采用风冷散热,造成了功耗较大、体积庞大和外壳设计复杂难以防水等弊端。本文提出在开关电源输出回路上加一个延迟导通电路,避免晶体管的异常发热问题,降低晶体管的开关损耗并提高开关电源电路的可靠性。

1 实验原理

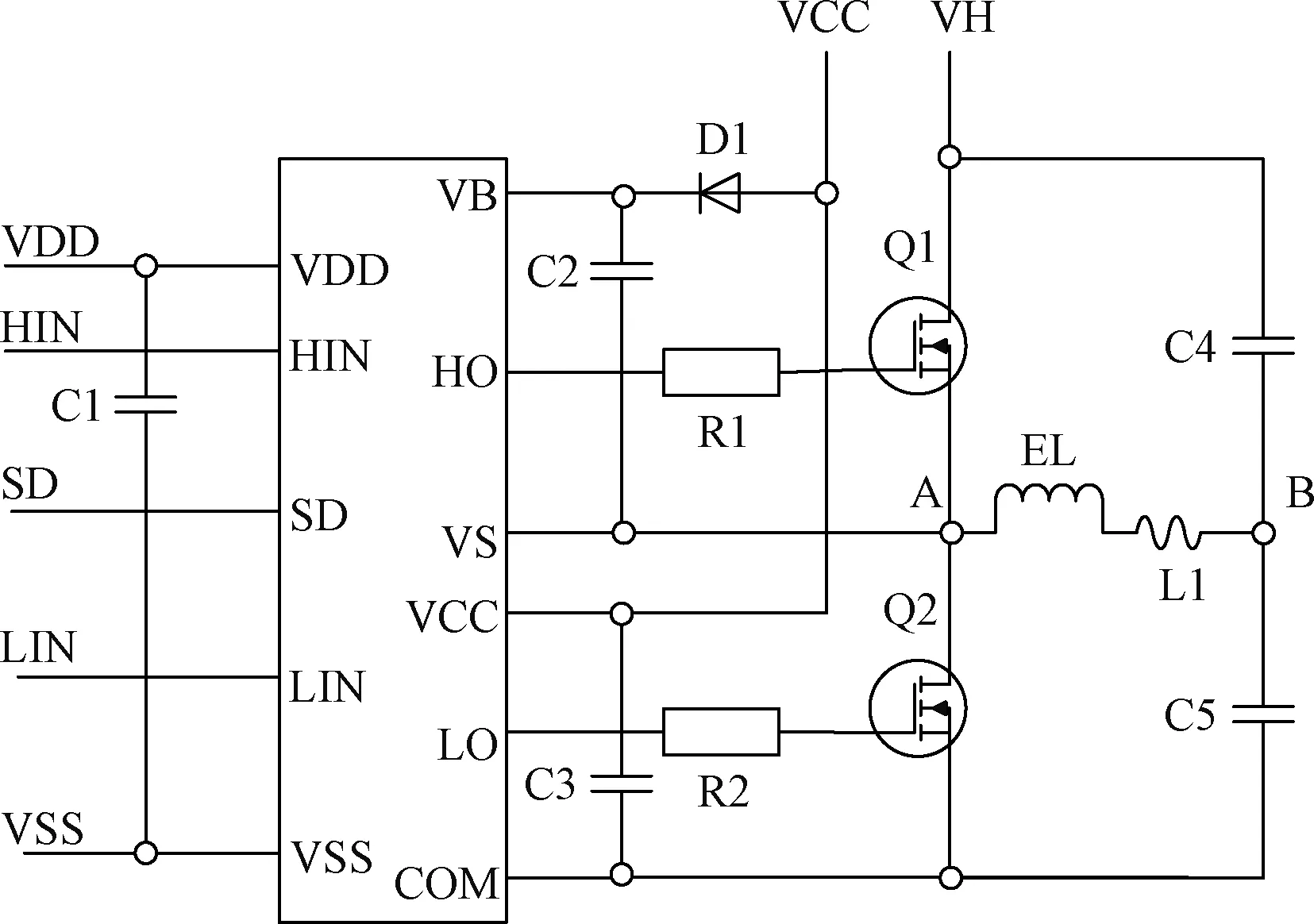

图1所示是半桥开关电路,其晶体管一般采用输入阻抗高便于控制的MOS管,在开关电路中晶体管功率损耗为其电流电压乘积,所以在关断(电流很小)与开通(压降很低)两种状态下晶体管的功率损耗都比较小。但在关断与开通的切换过程需要一定时间,在这切换期间晶体管同时承担一定的电压和电流,这个时候的功率损耗是比较大的,也称为开关损耗[4],包括开通损耗(turn-on loss)和关断损耗(turn-off loss)。尤其是开关电源电路的负载呈容性的情况下,对电容性负载快速充放电的电流很大,这样造成的晶体管的开关损耗就更大,表现为漏极电压还未下降到接近于0的低阻导通状态就有很大的一个电流尖峰通过,这样造成晶体管的开通损耗比纯电阻负载时明显增大。

图1 半桥开关电路Fig.1 Half-bridge switching circuit

因此设计在开关电源输出回路上加一个延迟导通电路,使输出电流在开关电源电路中的晶体管完全导通电压降低后再通过,可降低大电流通过晶体管的开关损耗。同时也适当控制延迟时间,不超过开关电源电路晶体管的当前导通时间,否则对负载就没有输出。延迟导通开关采用可控硅,其开关损耗比较小,即使开关损耗转移到了延迟导通开关上,整体上也降低了开关损耗并提高了开关电路的可靠性。

2 延迟导通电路

开关电路中晶体管开关损耗是由于晶体管开关过程中有限的电压变化率即压摆率,造成晶体管同时承受一定的电压和电流,两者乘积的积分为功率损耗,所以在开关切换期间通过大电流的损耗很大。如果能够控制在晶体管完全导通后承受接近于0的较低压降下电流通过,那么可大幅降低晶体管的功率损耗。

为了降低半桥驱动电路中晶体管的开关损耗,设计在开关电源输出与负载之间加入一个延迟导通电路,其作用是延迟电流滞后一个合理时间,使开关电源电路中的晶体管完全导通处于低阻状态时再允许对容性负载充放电的瞬间大电流通过,由此避免晶体管在关-开切换期间大电流通过造成开关损耗过大,也就是减小开通损耗。

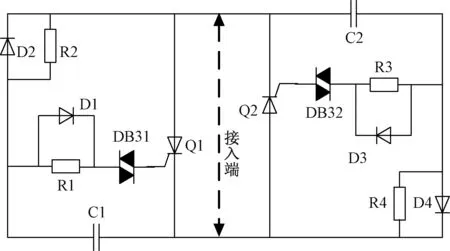

常用的开关控制元件为可控硅,借助参考了白炽灯调光控制双向可控硅导通角的延迟触发电路[5],双向可控硅的触发电流一般在毫安量级,但白炽灯调光电路工作在市电的50 Hz频率,允许RC积分电路延迟时间较长,驱动电致发光屏的开关电源工作在1 kHz左右,需要较快时间触发。采用触发电流较小的单向可控硅可允许较小的触发电容C,从而在小电流通过时达到较快的RC积分时间。双向可控硅的触发电流比单向可控硅大,如果采用双向可控硅则RC电路需要较大的触发电容C和较小的充电电阻R,结果会造成RC电路充电电流过大、电功率损耗严重。因此,采用两个RC延迟控制单向可控硅导通电路正反向并联,进行交流电流的双向控制,如图2所示。当开关电源在任一方向上有输出电压后,例如电压为上端为正下端为负,积分延迟电路为R2-C1,输出电压通过电阻R2对电容C1充电,经过一定积分时间后C1的电压逐渐上升超过触发管DB31的导通电压对可控硅D1的门极放电,触发可控硅D1延迟导通,经过负载的电流才能通过。将电阻R2并联一个二极管D2以导通反向电流减少电阻R2的功耗。同时R1在反向交流电压下起到限流作用,防止通过可控硅Q1门极-触发管DB31电流过大,电容C1电压达到触发管DB31的转折电压(一般在28~36 V)直接通过二极管D1放电触发可控硅Q1。对于Q2、R4、C2等构成的另一电路单元工作方式相同,控制方向相反,形成双向延迟控制。

图2 延迟导通电路Fig.2 Delay conduction circuit

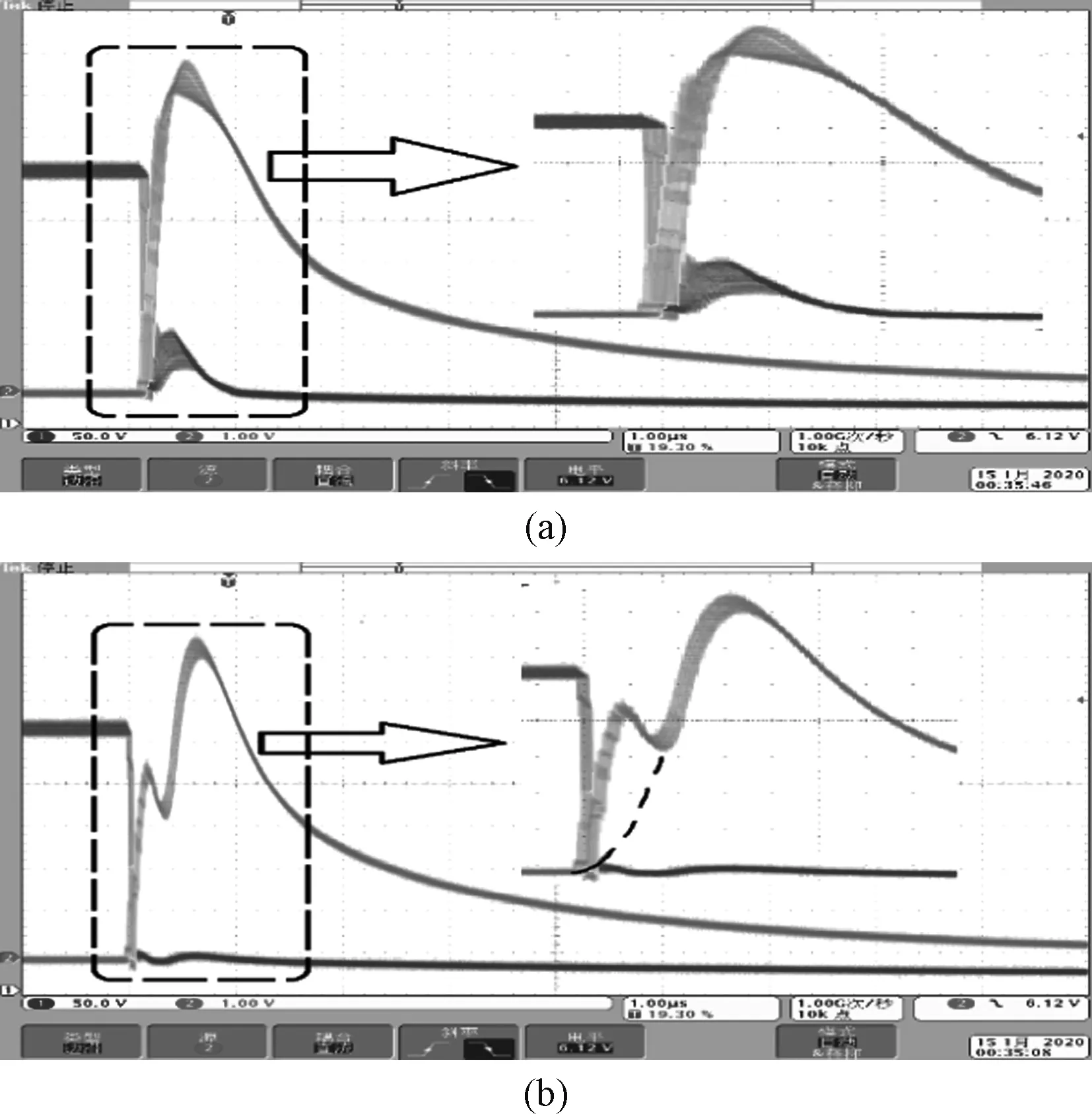

实验测试延迟导通电路的作用,负载为1 260 cm2的电致发光屏,电流波形测量中所用的电流取样电阻采用贴片式无感电阻[6],测量电流电压波形所用示波器为Tektroix-TDS1002,该示波器可以插入U盘存储波形数据。实验测得驱动电路中晶体管的漏极电压、电流波形如图3所示。图3(b)中电流波形左侧出现一个小尖峰脉冲,这是由于晶体管由截止迅速导通的瞬间电压变化激励起来的,通过MOS管的电流应为后面一个更高的尖峰脉冲,也就是实际电流发生从右上方横向拉宽后波形的虚线开始。对比两图,可明显发现将电流滞后一个合理时间,在晶体管完全导通呈低阻态时大电流通过,此时的压降接近于0,因此极大地降低了晶体管的开关损耗并提高了开关电路的可靠性。

图3 驱动电源开关电路在直接负载电致发光屏(a)和输出加入延迟导通电路后(b)的MOS管电压、电流波形比较Fig.3 Comparison of the voltage and current waveforms of the MOS tube of the driving power switch circuit after directly loading the electroluminescent screen(a) and the output after adding the delayed conduction circuit(b)

3 实验测试和结果分析

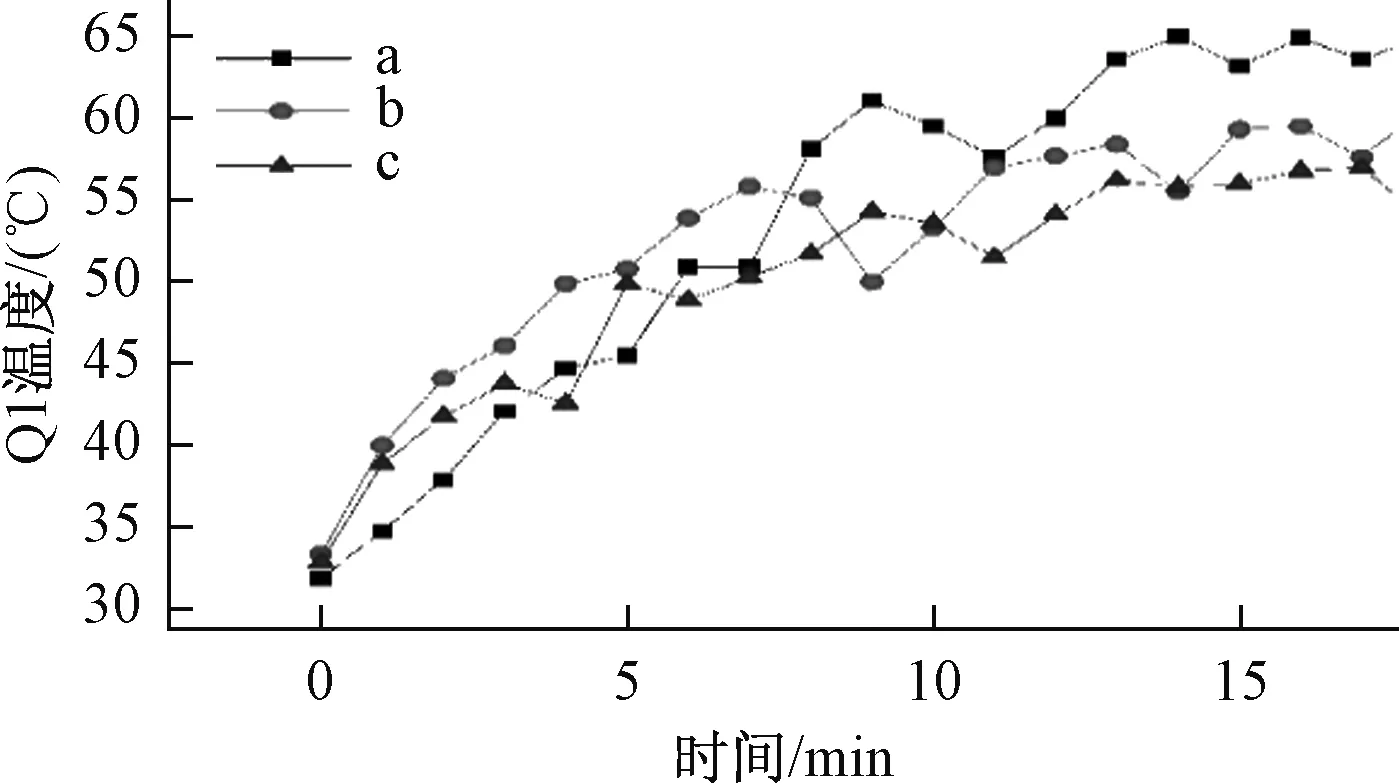

实验中,驱动电源采用半桥开关电路,如图1所示。由于电路中晶体管开关损耗体现在晶体管的温升特性上,因此比较延迟电路和电感对驱动电路中的MOS晶体管的温度影响,反映了晶体管的开关损耗。检测时将驱动电路中的MOS晶体管与非接触式测温枪固定,实时记录晶体管的温度值。采用测温枪每隔1 min就检测上桥晶体管Q1的温度,并记录。在同一实验环境下,测试了三种电路方案,分别是开关电源输出直接驱动、串联加入电感、加入延迟导通电路。实验测试结果如图4所示,从实验测试结果看出直接驱动的情况下温升较高,且在测试中负载功率稍大MOS光很容易被烧毁。加入电感后有所改善,不过在1 kHz工作频率下所使用的电感体积较大。而改加延迟导通电路后可以看到大体上温升还有所降低,稳定在54 ℃左右。表明输出延迟导通电路能够有效地降低MOS管的开关损耗。

图4 在开关电源输出直接连接负载(a)、串入电感(b)和加入延迟导通电路(c)时,MOS管Q1温度随时间变化曲线图Fig.4 When the output of the switching power supply is directly connected to the load(a), the inductance in series(b) and the delay conduction circuit(c) are added, the temperature change curve of the MOS tube Q1 with time

在以上三种输出与负载的连接方式下测量到的输入电功率基本相同,其中电感的作用是限制了电流的快速变化减缓了电流上升过程,从而使得对容性负载充放电的大电流部分错开了晶体管的开关切换时间,不过仍有部分电流与之重叠。而延迟导通电路则是将整个电流波形滞后错开,因此在晶体管开关切换期间几乎没有电流,从而更有效地降低开关损耗。

4 结论

电致发光屏激励起的尖峰电流致使晶体管开关损耗大,因此在开关电源输出回路串入一个电感,可减缓电流的上升,降低大电流与晶体管开关期间的重叠及其功率损耗,而在输出回路上加入延迟导通电路,使电流在晶体管完全导通之后再通过,可更好地避免晶体管的电压、电流重叠,从而有效地降低驱动开关电源的损耗,保证驱动电源的可靠性,同时也降低了驱动电源的散热设计难度,避免了风冷以及因此给外壳设计带来的麻烦。