基于砷化镓基IPD 技术的低通滤波器设计*

唐子舜,邢孟江,侯 明,李小珍

(1.昆明理工大学 信息工程与自动化学院,云南 昆明 650500;2.昆明学院 信息技术学院,云南 昆明 650500)

0 引言

随着当代半导体工艺与器件的日趋改善,得益于系统级封装的集成架构与设计思路,当代雷达、通信、电子战等微波系统朝着小型化、高密度集成、高可靠性依据低成本方向发展,因此对微波系统中器件与模块提出了更高要求[1]。

在微波系统中,微波滤波器具有极其重要的作用。特别是其在射频前端的应用,一个各项指标优良的滤波器能够直接影响整个微波系统的整体指标。而如今毫米波频段的实际工程应用中,印制电路板(Printed Circuit Board,PCB)、低温共烧陶瓷(Low Temperature Co-fired Ceramic,LTCC)、腔体的传统工艺制造的滤波器在其相对尺寸、加工精度和量产一致性上,相对IPD 工艺都不具有优势,而IPD工艺在系统集成问题上更具有优势。因此,在毫米波滤波器中引入IPD 结构,使得滤波器更加小型化,有利于优化滤波器的尺寸,得到较好的滤波器性能指标,是毫米波滤波器发展的一个重要方向。

砷化镓(GaAs)作为第二代半导体材料,凭借极低的介质损耗(为万分之一量级),在高功率传输领域具有优异的物理性能等优势,广泛应用于手机、无线局域网络、光纤通信、卫星通信、卫星定位等领域。本文使用第二代半导体GaAs 作为衬底,可以制造出高Q值的电感[2],实现高选择性滤波器。此外,GaAs IPD 技术可以与晶背穿孔技术兼容,实现射频接地和芯片三维叠层封装设计。

本文根据IPD 工艺,在砷化镓衬底的基础上,研制了一款低通滤波器。该低通滤波器截止频率为2.575 GHz,通带内的插入损耗低于1.5 dB,回波损耗低于-20 dB,在阻带对信号的衰减程度可以达到50 dB。对标美国mini-circuits 公司的一款陶瓷低通滤波器,在技术指标上能够满足相应的要求,同时大大缩小了尺寸。因此,该滤波器可以替代其在实际工程中应用。文献[3]基于IPD 设计了一款功分器,模型大小为3.1 mm×1.1 mm;文献[4]基于IPD 设计了一款定向耦合器,模型大小为3.60 mm×1.57 mm;文献[5]基于IPD 设计了一款带通滤波器,模型大小为1.04 mm×0.59 mm;文献[6]基于IPD 设计可控带通滤波器,模型大小为0.8 mm×0.988 mm;文献[7]基于IPD 设计了一款混合滤波器设计,大小为2.0 mm×1.8 mm。本文整体尺寸仅为0.65 mm×0.72 mm×0.085 mm,并通过HFSS 建模仿真验证了该设计的可行性。

1 滤波器理论与电路设计

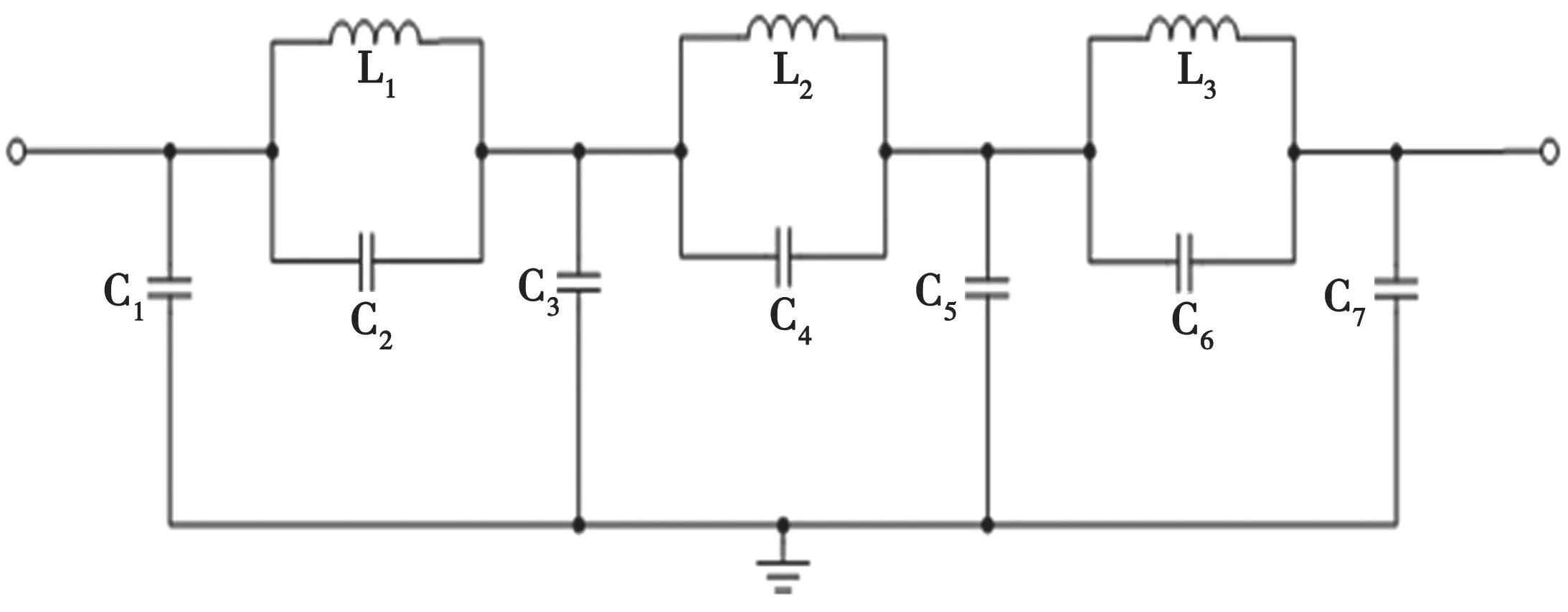

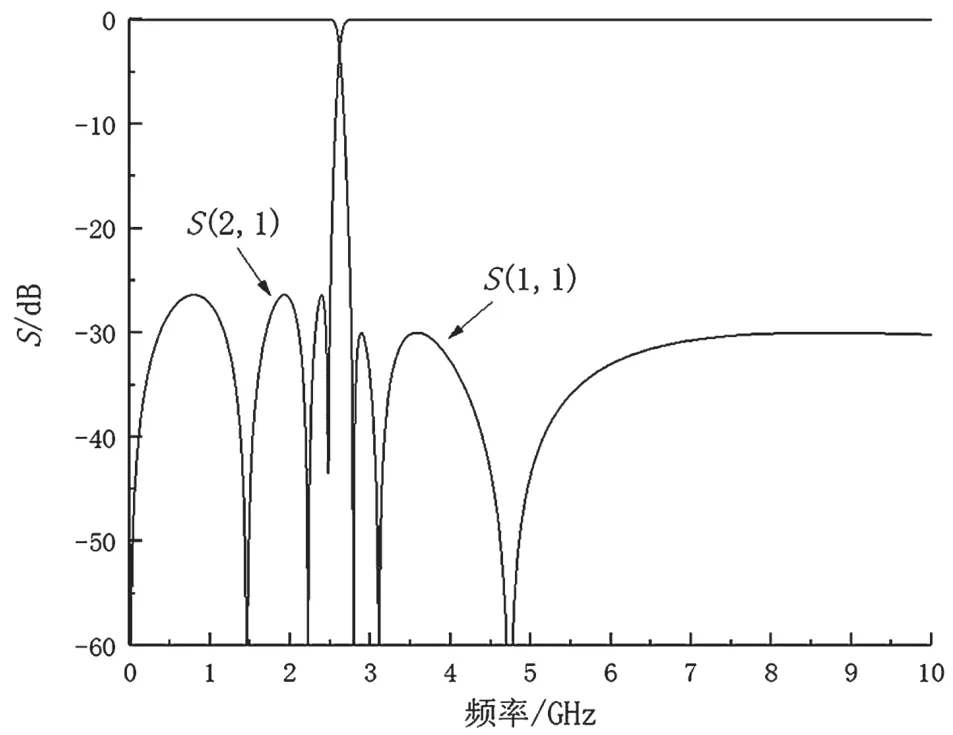

本文采用椭圆函数型滤波器(Elliptic Filter),相对于巴特沃斯型滤波器(Butterworth Filter)和切比雪夫型滤波器(Chebyshev Filter),在通带和阻带具有更好的滤波特性,使其在截止频率更为陡峭。根据设计要求,为了使其带内纹波尽可能小,使其截止效果更好,设计滤波器的阶数为7 阶。在理论计算上,设计带内纹波小于0.01 dB,带外纹波衰减至30 dB。最终设计结果如图1 所示,电路在先进设计系统(Advanced Design System,ADS)中的仿真结果如图2 所示。

图1 IPD 低通滤波器原理

图2 低通滤波器ADS 仿真结果

图1 中,电路元件值分别为:C1=0.77 pF、C2=0.32 pF、C3=1.31 pF、C4=1.86 pF、C5=1.12 pF、C6=1.50 pF、C7=0.20 pF、L1=3.55 nH、L2=1.75 nH、L3=1.75 nH。由图2 结果可知,该电路完全达到了上述指标要求,即具有下一步建模仿真的条件。

2 IPD 工艺

集成无源器件(Integrated Passive Device,IPD)技术是实现三维集成和“超越摩尔”的关键技术之一。根据无源器件制作工艺的不同,制作技术可以分为3 类,分别为薄膜技术、低温共烧陶瓷(LTCC)技术和基于高密度互连的电路板技术。将阻容的分离元件集成于多层介质板内,同时将滤波器、功分器、耦合器和天线等射频无源器件也集成于基板内,是SiP 技术小型化和高性能的有效路径之一[8-10]。

本文设计采用的是薄膜技术,使用的是砷化镓为基的IPD 技术。该IPD 总体上分为6 层薄膜,工艺叠层示意图如图3 所示。各层材料如表1 所示,N1、N2、N3层采用Si3N4材料,PV 层采用聚酰亚胺材料,衬底为砷化镓材料,M0层为金属接地层使用金或铜为材料。

图3 GaAs 衬底的IPD 工艺叠层示意

由图3 可知各个层薄膜之间位置与厚度的关系。电感在N3层,采用平面螺旋形式实现。通过改变线圈的长度和圈数,调节电感的大小值。电容采用金属平行板形式实现,跨越了N3、PV、N2这3 层。通过改变在各层的平面面积大小调节电容值的大小。其中,圆柱形为接地通孔连接N1层与M0层。

3 HFSS 建模与仿真

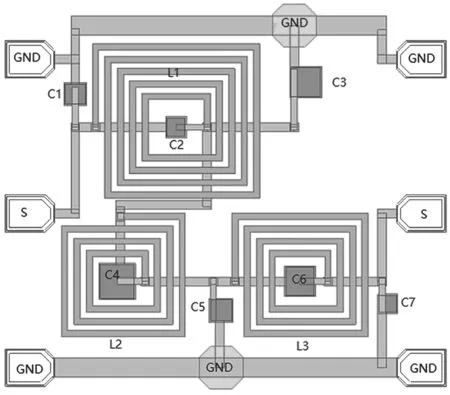

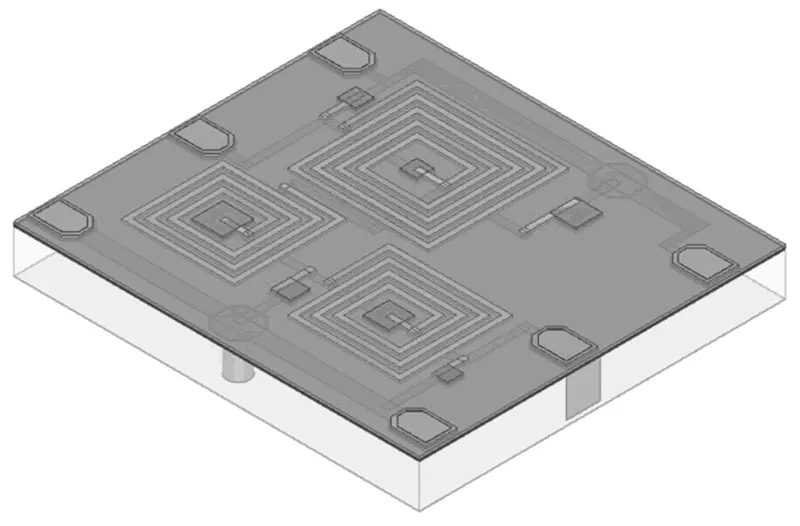

根据上述ADS 仿真结果分析可知,图1 的电路是可行的。将上述7 阶椭圆低通滤波器电路分为电容和电感,分别在上述IPD 工艺的基础上构建三维模型。得到相应的仿真数值后,按照图1 电路图对电路进行整体建模,得到如图4 所示的模型图。图4 中左右GND 为接地测试端,S 为源负载端。各个电路元件的布局也在其中标注。

按照ADS 中电路的设计要求可知:-3 dB 截止处频率为2.56 GHz,带内回波损耗大于26 dB,带外抑制大于30 dB。根据上述要求和图4 的整体布局建立三维模型,最终得到如图5 所示的三维模型。

图5模型的尺寸为650 μm×720 μm×85 μm,大大减小了滤波器的尺寸。经过调试仿真,最终得到如图6 所示的仿真结果。

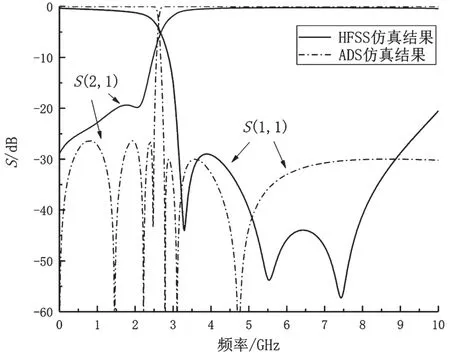

由图6 可知,该低通滤波器-3 dB 截止频率为2.575 GHz,通带内的插入损耗低于1.5 dB,回波损耗低于-20 dB,带外抑制达到了30 dB,在阻带4~8 GHz 范围内对信号的衰减程度可以达到50 dB。

图4 HFSS 电路建模整体平面布局

图5 IPD 低通滤波器的三维模型

图6 HFSS 仿真结果

如图7 所示,将ADS 仿真结果与HFSS 设计仿真进行对比可以发现,该方案的设计完全满足相关设计指标的要求,进一步证明了该方案的可行性,为以后基于GaAs 衬底的IPD 工艺设计提供了一个设计思路。

图7 HFSS 与ADS 仿真结果对比

4 结语

本文在GaAs 衬底的IPD 工艺基础上设计了一款低通滤波器,通过椭圆函数型滤波器的电路基础进行了ADS 仿真,得到了对标美国mini 公司的一款陶瓷型滤波器的设计指标。该低通滤波器截止频率为2.575 GHz,通带内的插入损耗低于1.5 dB,回波损耗低于-20 dB,在阻带对信号的衰减程度可以达到50 dB。在该基础上,在HFSS 软件中进行三维模型的建立和相关调试仿真,得到了很好的技术指标,满足实际设计的要求和使用,也为今后相关IPD 设计提供了相应帮助。