基于机械剥离b-Ga2O3的Ni/Au垂直结构肖特基器件的温度特性*

龙泽 夏晓川 石建军 刘俊 耿昕蕾 张赫之 梁红伟

(大连理工大学微电子学院,大连 116024)

本文制备了基于机械剥离b-Ga2O3的Ni/Au垂直结构肖特基器件,对该器件进行了温度特性I-V曲线测试.器件表现出了良好的二极管特性,随着温度从300 K升高至473 K,势垒高度从1.08 eV上升至1.35 eV,理想因子从1.32降低至1.19,二者表现出了较强的温度依赖特性,这表明器件的肖特基势垒存在势垒高度不均匀的问题.串联电阻随温度升高而降低,这主要是热激发载流子浓度升高导致的.本文利用势垒高度的高斯分布对器件的温度特性进行了修正,修正后的势垒高度为 1.54 eV,理查孙常数为 26.35 A·cm–2·K–2,更接近理论值,这表明利用高斯分布势垒高度的热电子发射模型能够很好地解释Au/Ni/b-Ga2O3肖特基二极管的I-V温度特性问题,这种方法更适合用来测量b-Ga2O3肖特基二极管的电学参数.

1 引 言

b-氧化镓(b-Ga2O3)材料是一种新兴的超宽禁带半导体材料,在最近几年受到了科学界的极大关注.b-Ga2O3单晶属于单斜晶系,晶格常数分别为:a=12.23 Å,b=3.04 Å,c=5.8 Å,a=b=90°,g=103.7°[1].因此 (100)与 (001)晶面为解理面,可以通过机械剥离的方法获得薄层结构的氧化镓材料[2,3].b-Ga2O3具有 4.9 eV的禁带宽度、8 MV/cm的理论击穿场强和较高的巴利伽优值[4,5],使得它相较于GaN,SiC等第三代半导体材料在高功率器件、日盲深紫外探测器、气体传感器等方面都有着独特的优势[5−7].除此之外,b-Ga2O3材料可以通过导模法、区熔法以及直拉法等方法制备质量较高的大尺寸单晶[8,9].这既为氧化镓基器件的研究提供了帮助,同时也为这种单晶材料的大规模生产及商业化奠定了基础.

在氧化镓材料以及器件领域,人们已经对b-Ga2O3薄膜生长[10,11]、光电器件[12,13]、大功率器件制备及表征(如MOSFET,SBD)等方面进行了大量的研究[14,15].其中,氧化镓的肖特基接触特性可以说是研究的重点之一.迄今为止,人们已经采用Ni,Pt,Cu,Au 等多种金属制作了不同的氧化镓肖特基二极管(Ga2O3-SBD),并且对器件的电学特性进行了测试与分析,其中绝大多数的测试均为室温条件下测试[16].然而,仅在单一工作温度下对器件进行电学测试只能获得势垒高度、理想因子等信息,难以全面分析肖特基势垒的特性.而电流-电压温度特性曲线测试能够进一步分析器件的电学性质,通过不同温度下的I-V曲线与Cheung和Norde的处理方法可以得到各项电学参数随温度的变化趋势,从而分析器件内部的电流传输机制[17,18].同时采用激活能与高斯分布拟合的方法可以对器件的势垒不均匀性进行评价,并且计算得到更精确的电学参数.

目前为止,有关氧化镓肖特基二极管温度特性的报道比较有限.2017 年,He 等[19]采用 (100) b-Ga2O3单晶衬底制备了 Pt/b-Ga2O3SBD,并对器件进行了温度特性测试,得到器件的势垒高度从294 K 时 的 1.39 eV 下 降 至 423 K 时 的 1.30 eV.Ahn等[20]制作了 Ni/Au和 Pt/Au的 b-Ga2O3SBD,发现二者具有相同的温度特性变化趋势,势垒高度和理想因子分别随温度升高而升高和降低.2018 年,Jian 等[21]制备了 Pt/b-Ga2O3SBD,并且利用高斯分布的非均匀势垒理论解释了理查孙常数偏离理论值的问题.Fares等[22]制备了Au/W/b-Ga2O3SBD,该肖特基接触具有更好的热稳定性,更适合于在高温下工作.2020 年,Reddy 等[23]在Si掺杂的b-Ga2O3外延层上制备了Au/Ni/b-Ga2O3SBD,并且在 100—400 K 的温度范围内进行了电学测试.利用多种方式提取了电学性质参数,采用高斯分布的势垒模型解释了势垒高度、理想因子与串联电阻的温度依赖特性.

人们对肖特基器件的研究普遍基于热电子发射模型(TE)来进行分析.然而这种理论模型的前提假设之一是肖特基势垒在横向上是均匀的,并且净电流的存在不会影响这种平衡[24].对于硅基器件来说,由于材料生长与器件制备工艺成熟,肖特基势垒相对均匀,可以采用TE模型来进行分析.但对于氧化镓材料来说,生长工艺不够成熟,单晶衬底存在界面质量差、界面层化学计量不均匀、电荷分布不均匀、界面层厚度不均匀以及掺杂原子的空间分布等原因,使得基于氧化镓的肖特基器件存在着势垒不均匀的现象,肖特基电极面积越大,不均匀程度也越高[23].因此采用TE模型来分析器件特性得到的结果不够准确,需要将势垒的不均匀考虑进来才能得到准确的电学参数.此外,在氧化镓SBD温度特性方面的工作几乎全部都是基于单晶衬底或外延材料,而基于机械剥离的薄层氧化镓肖特基二极管的温度特性研究十分稀少[19−23].本文通过机械剥离方式获得(001)晶向的氧化镓单晶薄层材料,并且制作了垂直结构的Au/Ni/b-Ga2O3肖特基器件.在300—473 K的温度范围内对器件进行了I-V温度特性测试,通过高斯分布模型对势垒不均匀性进行了分析,最终得到了更可靠的电学参数.

2 实验内容

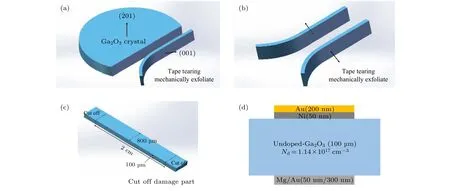

本文采用的材料为直径2英寸的非故意掺杂N型b-Ga2O3单晶晶圆,其载流子浓度为1.14 ×1017cm–3.原始单晶生长方法为 CZ 法 (Czochralski方法),氧化镓单晶的晶向为 (01) 方向.本文采用机械剥离的方式获得(001)晶向的条状薄层材料,机械剥离过程在晶圆截面进行.首先用胶带从晶圆截面撕下长约4 cm,厚度数百微米的条状单晶.然后采用胶带对撕的方法减薄材料厚度至100 µm以下,去除两端损伤及表面不连续部分,最终获得长度约为 2 cm,宽度约为 800 µm,厚度约为 100 µm的条状单晶材料.机械剥离过程示意如图1所示.在该材料上制作了垂直结构Au/Ni/b-Ga2O3肖特基二极管.欧姆接触的制作采用Mg/Au叠层工艺,利用真空热蒸发方式分别蒸镀Mg (50 nm)和Au(300 nm)作为电极,蒸镀后在 Ar环境下 400 ℃退火2 min[25].同样采用真空热蒸发的方法蒸镀Ni(50 nm)和 Au (200 nm)作为肖特基电极,其中Ni与b-Ga2O3形成肖特基接触,Au作为保护层覆盖在Ni表面.为了避免Au与Ni和Ni与b-Ga2O3之间的热扩散,蒸镀完成后不进行退火处理.以上蒸镀过程均在 5×10−4Pa 的真空中进行.采用物理掩膜的方法在氧化镓表面蒸镀直径为600 µm的圆形电极,欧姆电极与肖特基电极尺寸及形状相同,具体的器件结构示意图如图1所示.器件的电学及温度特性测试使用可控温度平台(300—473 K)、Keithley 2611A 单通道系统数字原表和Keithley 4200-SCS参数分析仪进行测试.

3 结果与讨论

3.1 电流-电压温度特性

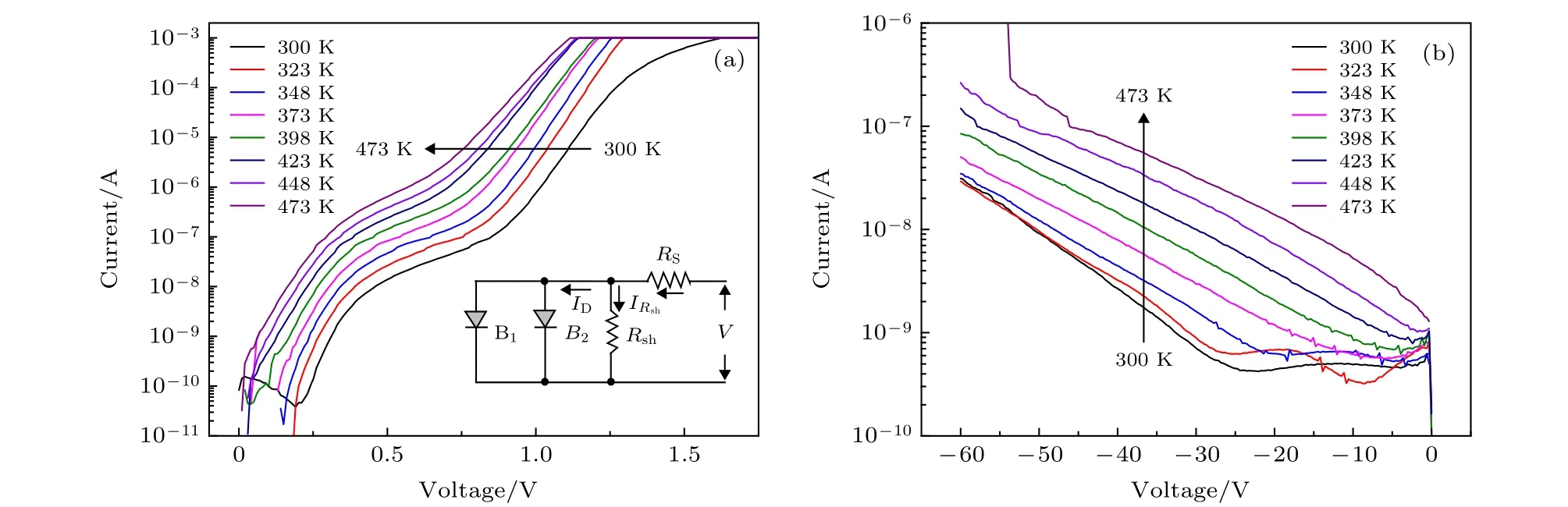

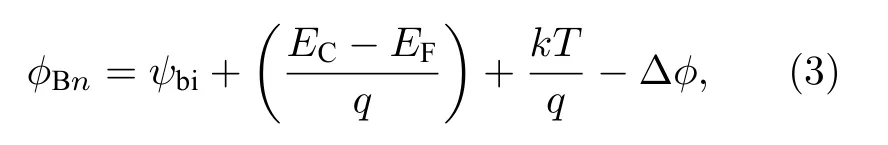

图2分别为Au/Ni/b-Ga2O3肖特基二极管在不同温度下的正向和反向I-V特性曲线,测试温度范围 300—473 K,温度步进 25 K.

由图2可以看出,在正向偏压条件下,器件的电流随电压的增大而指数增加,同时电流也随着温度的升高而增大.反向电流随电压变化程度很小,这是肖特基器件整流特性的良好体现.I-V曲线表现出了两段线性区域,这主要是由于势垒的不均匀导致的.出现双势垒表明整个势垒平面有一些区域与其他区域存在明显的势垒高度差,等效为一小块低势垒区域嵌入到整个势垒平面当中,所以体现出了双势垒的I-V曲线,这等效于两块肖特基势垒并联[26,27].低势垒区域往往面积很小,对于器件的电学性能影响不大.这种现象主要由晶体自身的缺陷与晶体表面的表面态导致,而机械剥离的氧化镓样品表面往往会含有一定密度的表面态,正是这些因素导致测试的正向I-V曲线呈现为两段线性区域[28,29].根据双指数形式的TE模型给出器件的I-V理论表达式为[30]

图1 (a),(b),(c) 机械剥离氧化镓单晶材料;(d) Au/Ni/b-Ga2O3 肖特基二极管结构示意图Fig.1.(a),(b),(c) Mechanically exfoliated beta-Ga2O3 single crystal;(d) schematic cross section of Au/Ni/b-Ga2O3 Schottky barrier diode.

图2 肖特基二极管的 I-V 温度特性曲线 (a) 正向;(b) 反向Fig.2.Temperature dependent I-V characteristic curves of Schottky barrier diode: (a) Forward curves;(b) reverse curves.

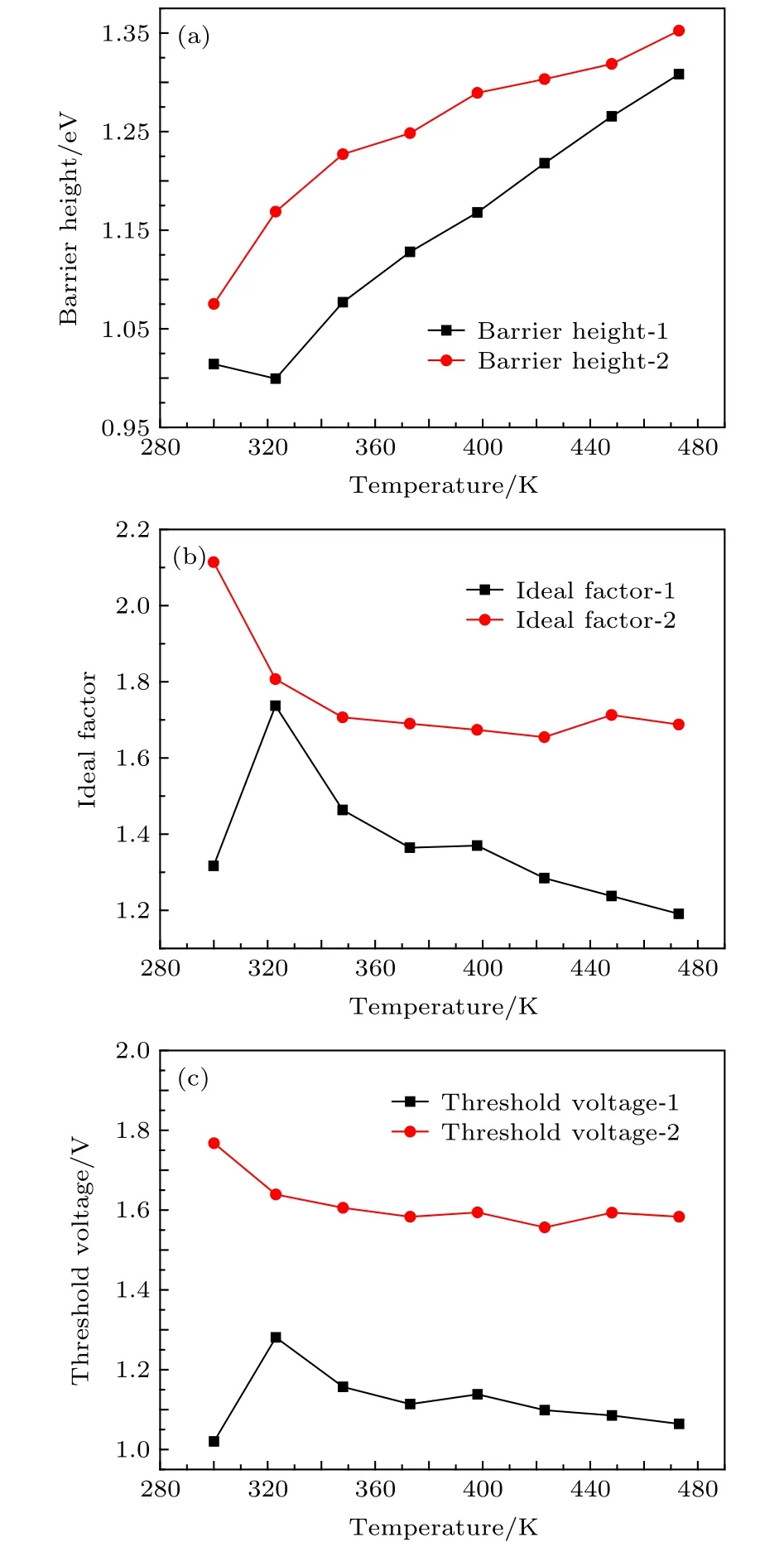

其中A∗为理查孙常数,φBn为势垒高度,n为理想因子,RS为串联电阻,Rsh为并联电阻.T为器件的工作温度,B1与B2分别为两个不同高度的势垒参数,等效电路如图2(a)插图所示.通过对正向IV曲线进行线性拟合可以提取器件的阈值电压Vth,势垒高度φBn和理想因子n等参数,得到图3所示的结果.

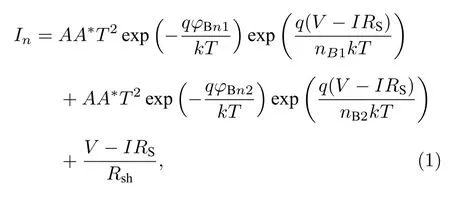

图3 I-V 温度特性曲线提取的 (a) 势垒高度;(b) 理想因子;(c) 阈值电压Fig.3.The parameters from temperature dependent I-V characteristic curves: (a)Barrier height;(b) ideal factor;(c) threshold voltage.

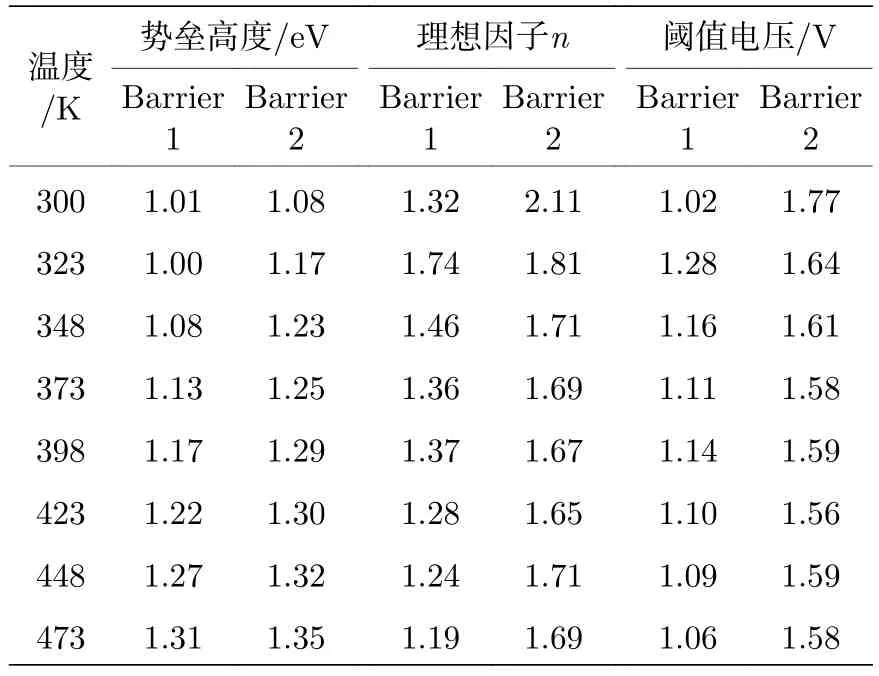

首先,器件的正向I-V特性曲线存在两段线性区域,这表明肖特基势垒存在着不均匀的情况.分别对两段区域进行数据处理,并且得到两个不同的势垒分布: Barrier 1 和 Barrier 2.两部分势垒的高度不同,但具有相似的随温度变化趋势.随着工作温度的升高,势垒高度分别从1.01和1.08 eV上升至 1.31和 1.35 eV,理想因子从1.32和 2.11降低至1.19和1.69,阈值电压同样随温度的升高而降低,具体的数据如表1所列.

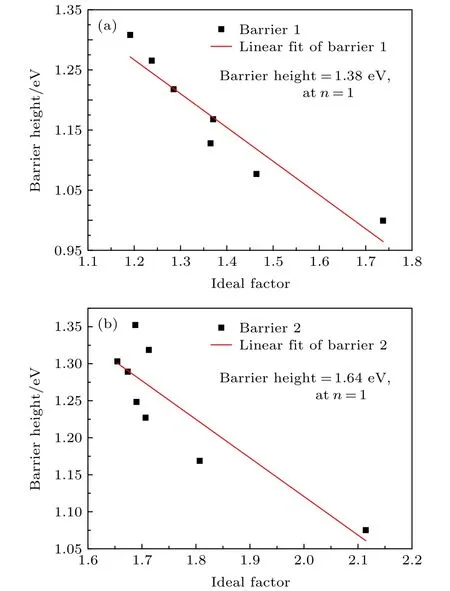

图4为势垒高度φBn与理想因子n的依赖关系,可以看出器件的I-V特性随温度变化明显且有规律,这表明器件具有较强的温度依赖特性.理想因子和势垒高度随温度的变化很可能是因为肖特基势垒不均匀导致的.计算中采用的TE模型认为肖特基势垒均匀,但通常情况下肖特基接触势垒高度是不均匀的.势垒的不均匀性可能是多种物理原因造成的,如表面和体缺陷导致的界面质量差、界面层化学计量不均匀、界面电荷分布不均匀、界面层厚度不均匀以及掺杂原子的空间分布等原因.对于本文而言,势垒的不均匀一方面是由氧化镓单晶材料存在缺陷导致,另一方面也与机械剥离过程有关.通过机械剥离获得的单晶材料表面存在大量悬挂键,这导致了表面态的存在.同时被束缚在表面的电荷会使能带弯曲,而能带的弯曲程度在横向上很可能是不均匀的.除此之外,机械剥离后的单晶表面并不是完全连续的,一些岛状、层状、裂纹状结构也会导致势垒的不均匀性.以上原因导致势垒存在高低不同的部分,在较低的温度下,电流会从较低的势垒部分通过,因此通过I-V曲线得到的参数为低势垒部分的平均值.而在较高的温度下,电流则能够流过势垒高度较高的部分,导致理想因子的降低和势垒高度的升高[31].但通过势垒高度随温度的变化趋势可以发现,肖特基接触面上仍有更高的势垒无法通过.而在较高温度的条件下,器件的理想因子更趋近于理论值1,这表明在高温时扩散电流可能在电流输运中占据主导地位[32,33].

表1 I-V 温度特性曲线提取数据表Table 1.The parameters from temperature dependent I-V characteristic curves.

I-V曲线提取的参数是基于正向小电压下的电流曲线来进行计算的,这样的处理方式对于势垒不均匀的肖特基器件来说往往会使势垒高度偏低.而电容-电压(C-V)曲线分析则是工作在反向较大偏压条件下,这样可以一定程度上避免正向小电压下电极未完全激活的问题.

图4 不同温度下势垒高度与理想因子依赖关系 (a) Barrier 1;(b) Barrier 2Fig.4.Plot of barrier height as a function of ideal factor obtained at various temperatures: (a) Barrier 1;(b) Barrier 2.

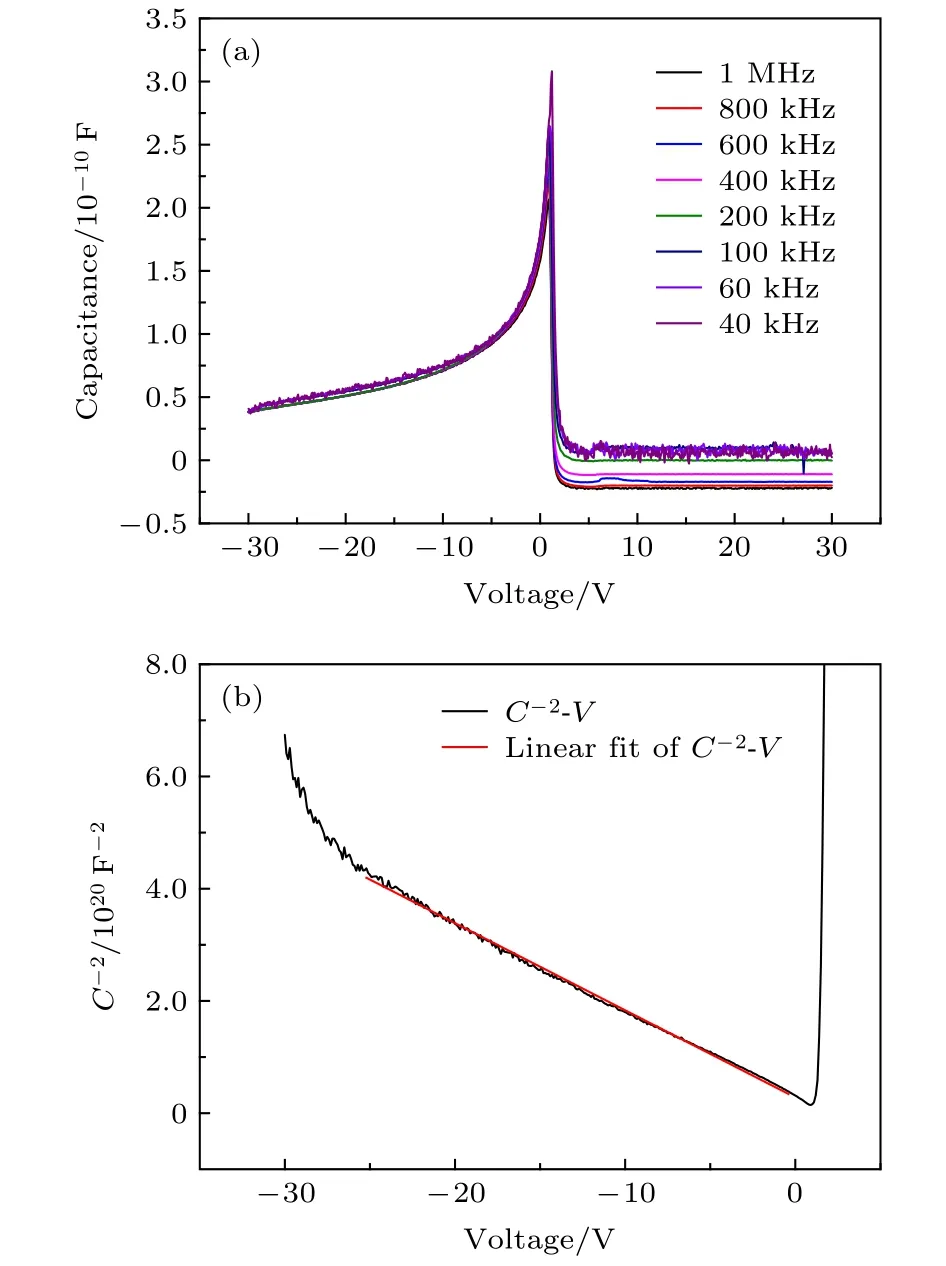

图5为器件在不同频率下的C-V曲线,测试频 率 范 围 为 40 kHz至 1 MHz,电 压 范 围 为–30 至+30 V.在不同的频率下,器件的C-V曲线基本一致,满足肖特基器件的电容电压关系式:

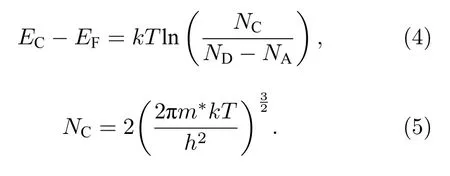

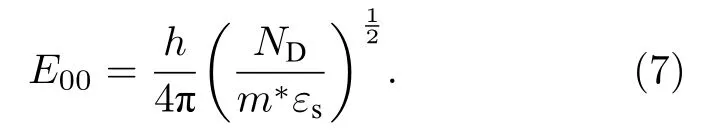

式中,ND为载流子浓度,ψbi为内建电势.可以通过对C-V曲线的处理得到以上参数.势垒高度与内建电势的关系为

其中EC−EF为导带与费米能级之间的距离,这里可以表示为

图5 (a) C-V 特性曲线;(b) 频率为 100 kHz 的 1/C 2-V 曲线Fig.5.(a) C-V characteristic curves;(b) 1/C 2-V characteristic curve of 100 kHz.

其中NC为导带上的有效态密度,h为普朗克常数,m∗为电子有效质量,这里取m∗=0.34m0,而∆ϕ为镜像力导致的势垒降低程度,可以表示为

采用100 kHz的C-V曲线进行计算,得到器件在300 K的温度下载流子浓度为 1.14×1017cm−3,势垒高度为1.88 eV.可以发现通过C-V曲线计算出的势垒高度要明显高于通过I-V曲线计算的到的值.主要原因是在室温下,电流更容易从势垒较低的部分流过,I-V测试小电压下电极的实际激活面积很小,得到的参数基本反映了势垒最低处的高度.而C-V测试得到的参数则可以看成是整个势垒的平均值,由于势垒的不均匀性导致了这种方法得出的势垒高度更高.但同时也不能排除1/C2-V曲线的线性度不够高带来的计算误差.从载流子浓度方面可以看出,非故意掺杂的氧化镓单晶具有较高的载流子浓度,通过计算肖特基势垒的特征能E00可以分析得到电流传输的主要机制,特征能E00的表示式为

特征能与kT的比值反映了器件满足的电流传输机制,若E00/kT≪1 则为热电子发射模型(TE),若E00/kT≈1 则为热场发射模型 (TFE),若E00/kT≫1则为场发射模型(FE)[34].通过计算得出300 K时器件的特征能E00=3.40meV ,远小于kT=25.85meV,表明器件的电流传输机制主要是TE模型,这与利用TE模型计算出的理想因子接近于1是相吻合的.

3.2 串联电阻RS

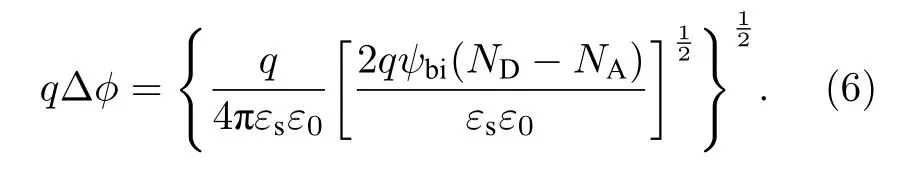

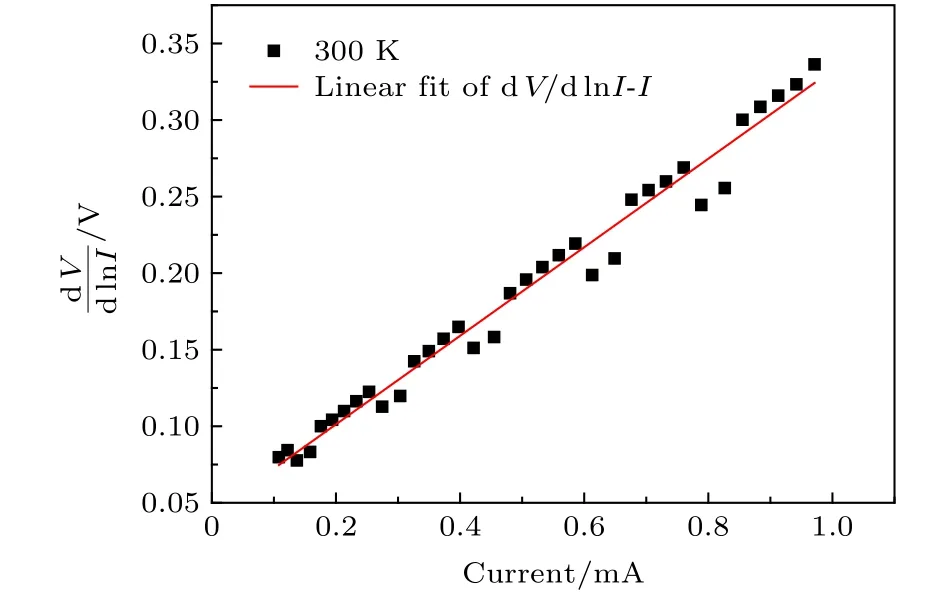

对于SBD来说,串联电阻RS是一个非常重要的性能参数.它直接影响了器件在较高的正向偏压下的电流特性,同时对于导通截至电流比也有着一定的影响[23].分别采用Cheung的dV/dlnI-I曲线与H(I)-I曲线方法和Norde的F(V)-V曲线方法来提取器件的串联电阻RS与势垒高度φB等参数[17,18].如图6所示,通过对300 K温度下dV/dlnI-I曲线进行线性拟合可以得到器件的理想因子n为1.76,这与I-V曲线得到的值相吻合,串联电阻为RS=285.76Ω.

图6 300 K 温度下的 dV/dlnI-V 曲线Fig.6.dV/dlnI-V curve at the temperature of 300 K.

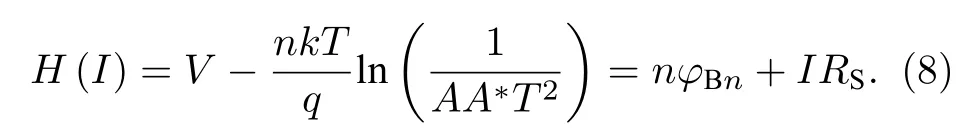

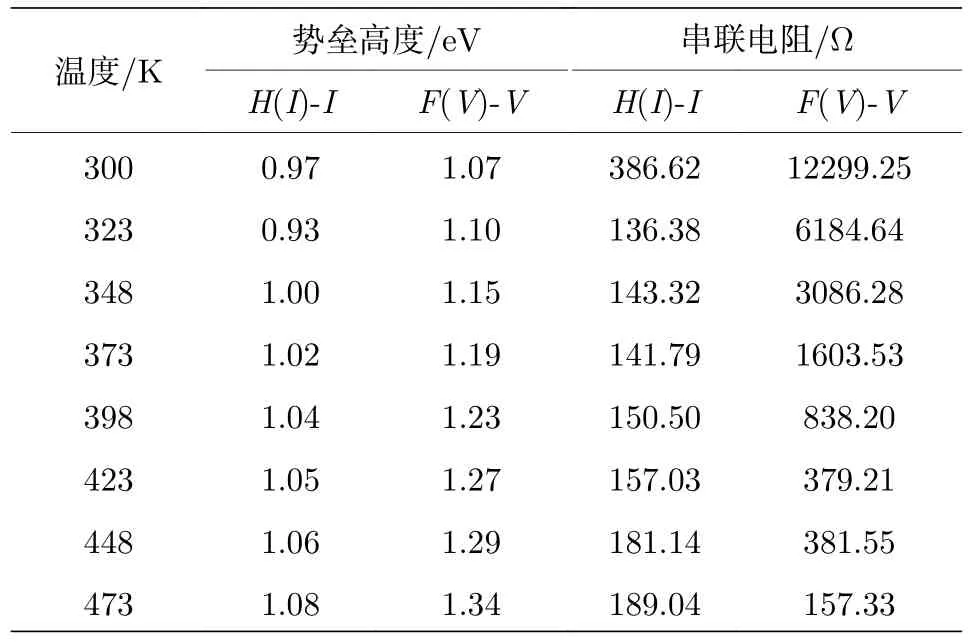

通过Cheung的方法,定义H(I)为[17]

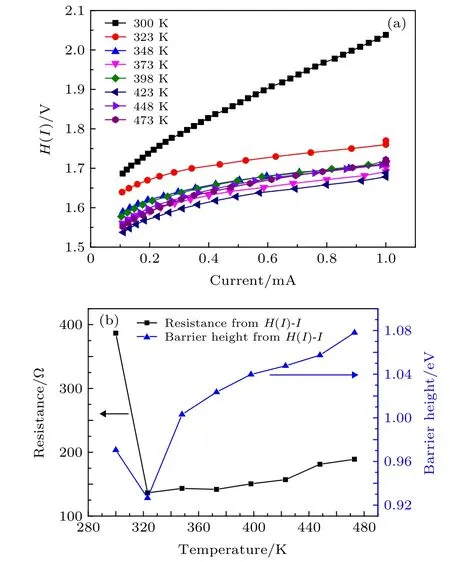

在已知理想因子n随温度的变化量时,可以通过对曲线线性拟合后得到的斜率和截距来计算得出势垒高度和串联电阻值.器件的H(I)-I温度特性曲线与对应的势垒高度和串联电阻变化如图7所示.通过数据可以发现,随着温度的不断增加,势垒高度和串联电阻发生了相应的变化,二者分别从 300 K 时的 0.97 eV 和 386.62 W 升高 和 降低至 473 K 时的 1.08 eV 和 189.04 W.在 300 K 时H(I)-I与dV/dlnI-I得到的串联电阻值有一定的差距,这可能与H(I)-I曲线线性度较差有关,并且在较大正向偏压下电流变化过快也会导致一定的拟合误差.也正是因为以上原因,使得串联电阻先随温度升高剧烈降低,然后缓慢升高,但总体表现为降低的趋势.这主要是由于温度升高使一些室温下未激活的缺陷激活,导致载流子浓度增加从而降低了电阻值[20,35].

图7 H(I)-I (a) 温度特性曲线;(b) 不同温度时的串联电阻和势垒高度Fig.7.H(I)-I (a) Temperature dependent curves;(b) the resistance and barrier height at various temperatures.

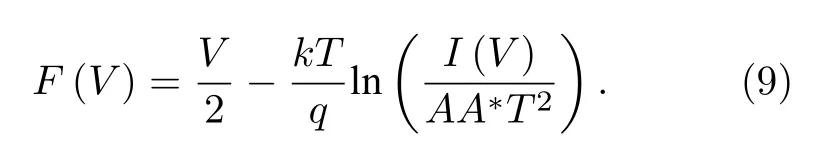

Norde提出可以通过偏置电压V的经验函数F(V),利用正向I-V曲线得到F(V)-V曲线,从而提取器件的势垒高度和串联电阻.其中经验函数F(V)的表达式为[18]

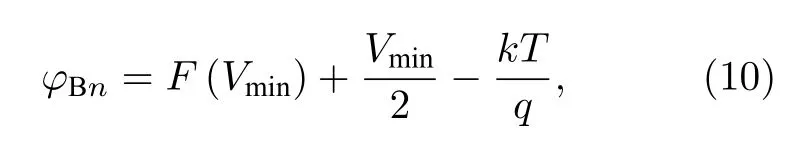

则势垒高度与串联电阻可以表示为

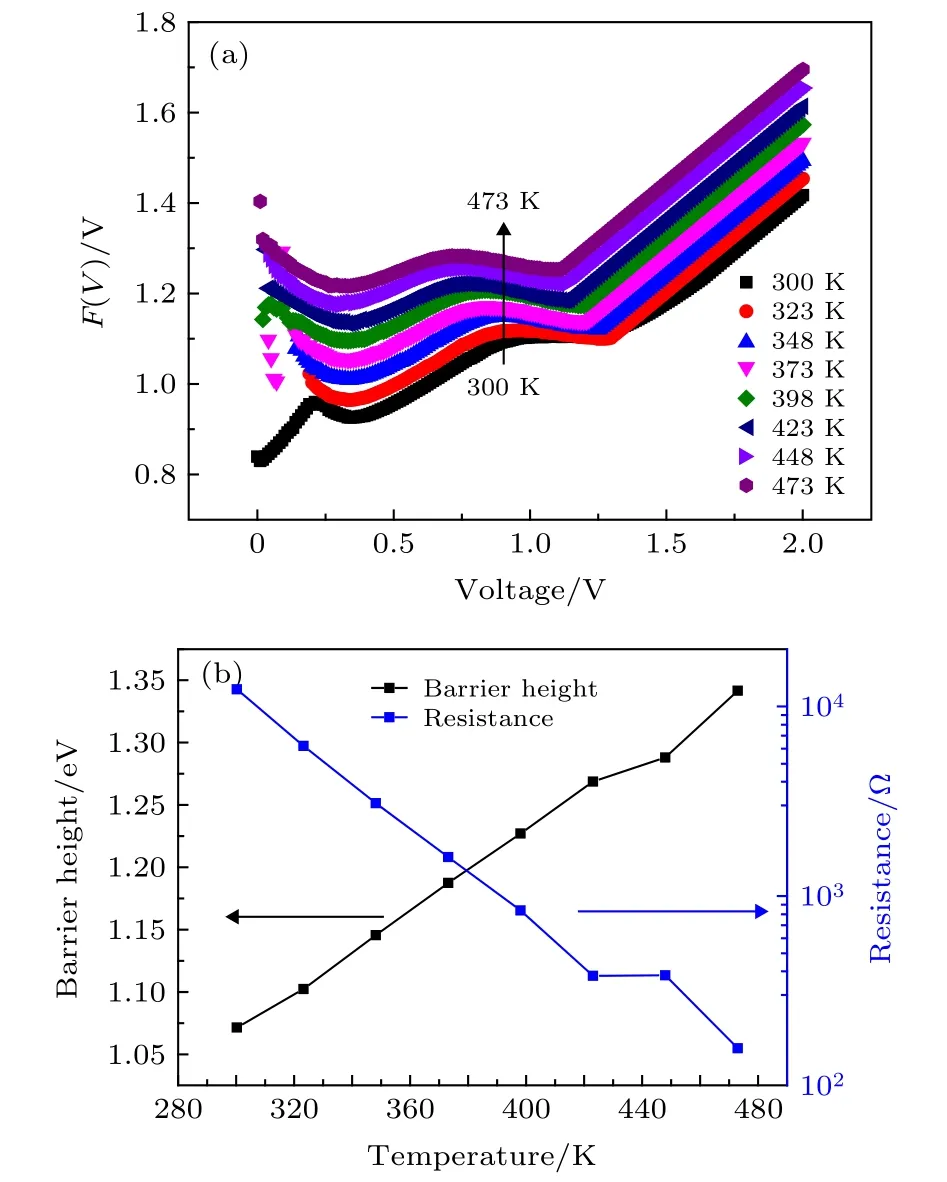

其中Vmin为曲线最低点对应的正向偏压,而F(Vmin)和I(Vmin) 则为相应的函数值.F(V)-V的温度特性曲线与势垒高度和串联电阻的温度变化如图8所示,F(V)-V和H(I)-I的具体数据如表2所列.

图8 (a) F(V)-V 温度特性曲线;(b) 不同温度时的串联电阻和势垒高度Fig.8.(a) F(V)-V temperature dependent curves;(b) the resistance and barrier height at various temperatures.

表2 H(I)-I与 F(V)-V 曲线提取数据表Table 2.The parameters from H(I)-I curves and F(V)-V curves.

Norde方法与Cheung方法之间的区别主要在于,Cheung方法更趋向于分析正向偏压较高、电流趋于饱和阶段的I-V曲线,而Norde更趋向于分析小电压下的I-V曲线变化.对于本文而言,由于在较大正向偏压下电流变化迅速,所以更适合采用Norde方法来对数据进行处理,得到的参数更接近于真实情况.Norde方法得到的势垒高度随温度的升高从 1.07 eV 上升至 1.34 eV,这与I-V曲线Barrier 2得到的1.08至1.35 eV符合的非常好,侧面印证了Norde方法的准确性.串联电阻随温度的升高从 300 K时的 12.3 kW降低至 473 K时的 157.33 W,并且随温度的升高呈指数下降,下降原因与之前的分析相同.

3.3 势垒的不均匀性

同样,可以通过固定偏压下激活能的温度特性曲线来判断在器件开启时的面电极激活状态.理想条件下,将(1)式进行一定处理得到如下关系:

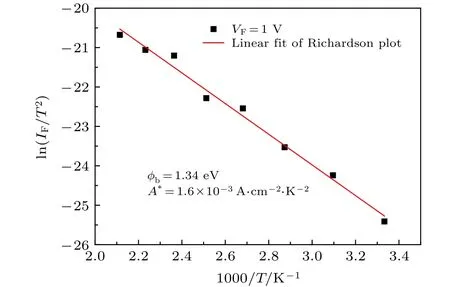

式中,VF为开启状态下的正向偏置电压,IF为对应的电流,q(φBn−VF) 则为激活能.通过构建图像可以得到器件的势垒高度φBn,同时也可以计算理论的理查孙常数A∗的值,所以该图像也称为理查孙图[36].在VF=1V时的理查孙图如图9所示.通过对图像进行线性拟合可以得到器件势垒高度为1.34 eV,这略高于300 K时I-V曲线得到的1.08 eV,但也明显低于通过C-V曲线确定的1.88 eV.这表明肖特基势垒的确存在不均匀的问题,正向偏压为1 V时只有低势垒部分被激活.而通过拟合直线的截距计算出的理查孙常数为1.6×10−3A·cm−2·K−2,远远低于理论值,如果按照理论值为 4 1.11A·cm−2·K−2来计算[37],则电极的电激活面积仅为 1.1×10−7cm2,不足实际电极面积的1%.

图9 肖特基二极管的理查孙图Fig.9.Richardson's plot of Schottky barrier diode.

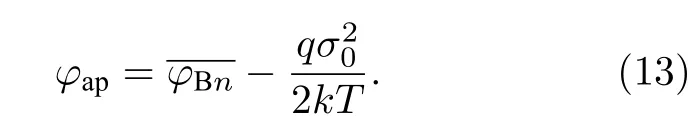

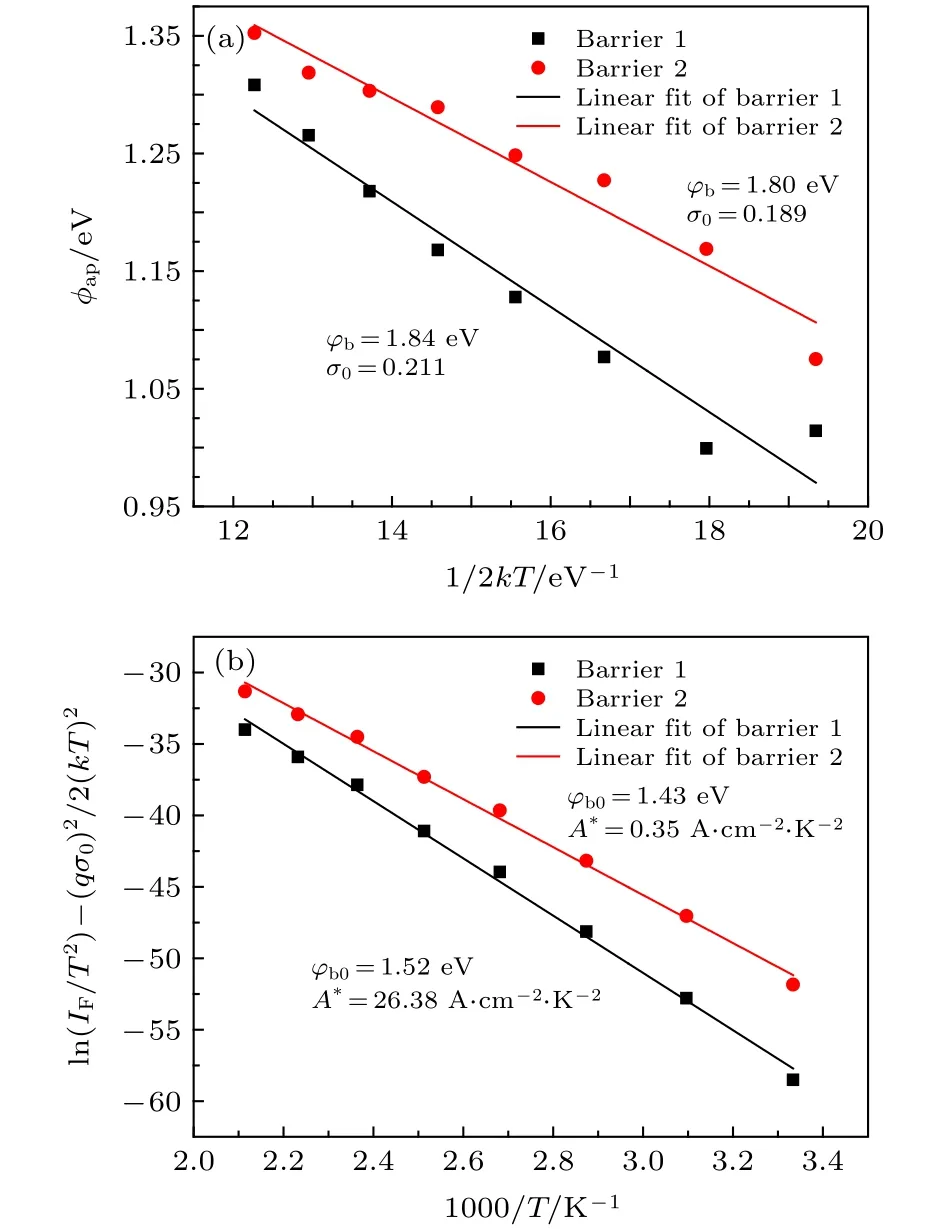

由以上分析可知,肖特基势垒在横向上存在随机的不均匀分布,而这种分布应满足高斯分布的模型,所以本文利用高斯分布模型来对势垒高度进行一定的修正[38].测试得到的势垒高度应满足如下公式:

其中φap为实际测试得到的势垒高度,为平均势垒高度,σ0为高斯分布的标准差.这里使用I-V曲线数据进行处理,绘制图像如图10(a)所示,可以得到标准差σ0的值分别为 0.211和0.189.再绘制图像如图10(b)所示,这样就可以计算得到修正后的平均势垒高度与理查孙常数值.

图10 (a) 图像;(b) 高斯分布修正后的理查孙图Fig.10.(a) The plot of ;(b) Richardson's plot after Gaussian distribution processing.

通过对高斯分布模型修正后的理查孙图进行线性拟合可以得到Barrier 1和Barrier 2势垒高度分别为 1.52 eV 与 1.43 eV,理查孙常数也从1.6×10−3A·cm−2·K−2变为 2 6.38A·cm−2·K−2和0.35A·cm−2·K−2,相对来说更接近理论值41.11A·cm−2·K−2,这证明高斯型的势垒分布模型能够很好的解释器件的肖特基势垒不均匀问题.

4 结 论

本文制备了基于机械剥离薄层材料的Au/Ni/b-Ga2O3肖特基二极管,研究了器件的I-V温度特性曲线.发现器件随着工作温度的升高,串联电阻降低,这是由于额外的热能激发浅能级缺陷形成新的载流子导致的.同时势垒高度升高,理想因子降低,二者存在着较强的温度依赖关系,这证明器件的肖特基势垒存在不均匀的现象.利用高斯分布模型对势垒的不均匀进行修正,得到实际的势垒高度为 1.54 eV,理查孙常数为 2 6.38A·cm−2·K−2,较修正前更接近理论值.以上结论共同表明,利用高斯分布势垒高度的热电子发射模型能够很好的解释Au/Ni/b-Ga2O3肖特基二极管的I-V温度特性问题.