基于DSP Builder的快速哈达玛变换实现

赵杰

(商洛学院 电子信息与电气工程学院,陕西商洛 726000)

哈达玛变换是一种常用的数学变换,由于其具有实数变换,变换只涉及加、减法等特点,已在诸多领域得到广泛的应用,如重建成像、通信系统、数字水印、图像压缩等[1-6]。实际中,往往需要硬件实现数字信号处理算法。EDA(电子设计自动化)技术的迅速发展,使得通过硬件描述语言在FPGA上实现常见信号处理变换成为可能。但是程序的代码编写、调试、仿真复杂,开发周期较长、工作量大,要求开发者有很高的设计能力[7-8]。若使用调试好的IP核可显著减小工作量,但很多IP核需要单独购买[9]。本文利用DSPBuilder,在Simulink工作环境下使用图形模型构建快速哈达玛变换的运算模型,并进行仿真,将多个工具联合起来,避开复杂的代码设计,降低了开发难度。

1 快速哈达玛变换

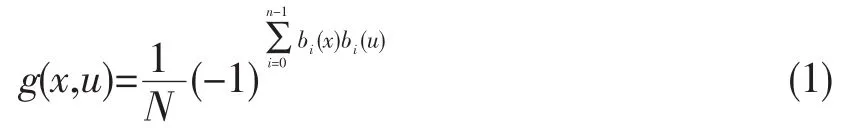

传统哈达玛变换及其逆变换的基本形式为[10]:

一维哈达玛变换核:

式中,x,u=0,1,…,N-1。一维哈达玛正变换为:

反变换也具有类似的形式:

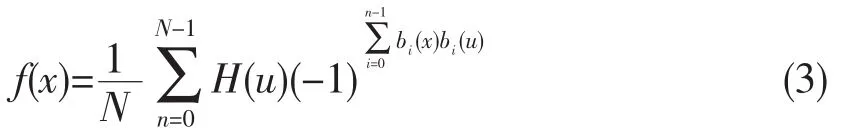

若直接使用式(2)或式(3),运算复杂度会很高。尤其随着变换点数的增加,计算量增长非常迅速,实际应用实现起来比较困难。为此,学者提出了相应的快速算法[10]。本文以8阶为例:

令[f1(x)]=[G2][f3(x)],[f2(x)]=[G1][f1(x)],[f3(x)]=[G0][f2(x)],则有:

由式(6)、式(7)和式(8)可得到哈达玛变换的一种快速算法,可以运用蝶形运算的方式来实现,但若用代码编写,硬件实现起来仍然比较麻烦[8]。

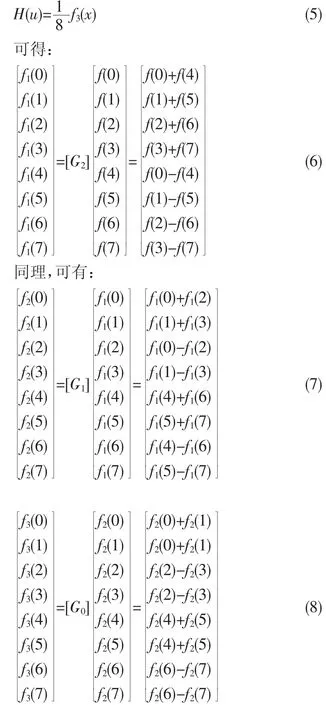

2 模型设计

利用DSP Builder和Simulink出色的模型化设计能力,可以将变换的硬件实现难度降低。设计的基本步骤如图1所示。

图1 模型化设计主要流程

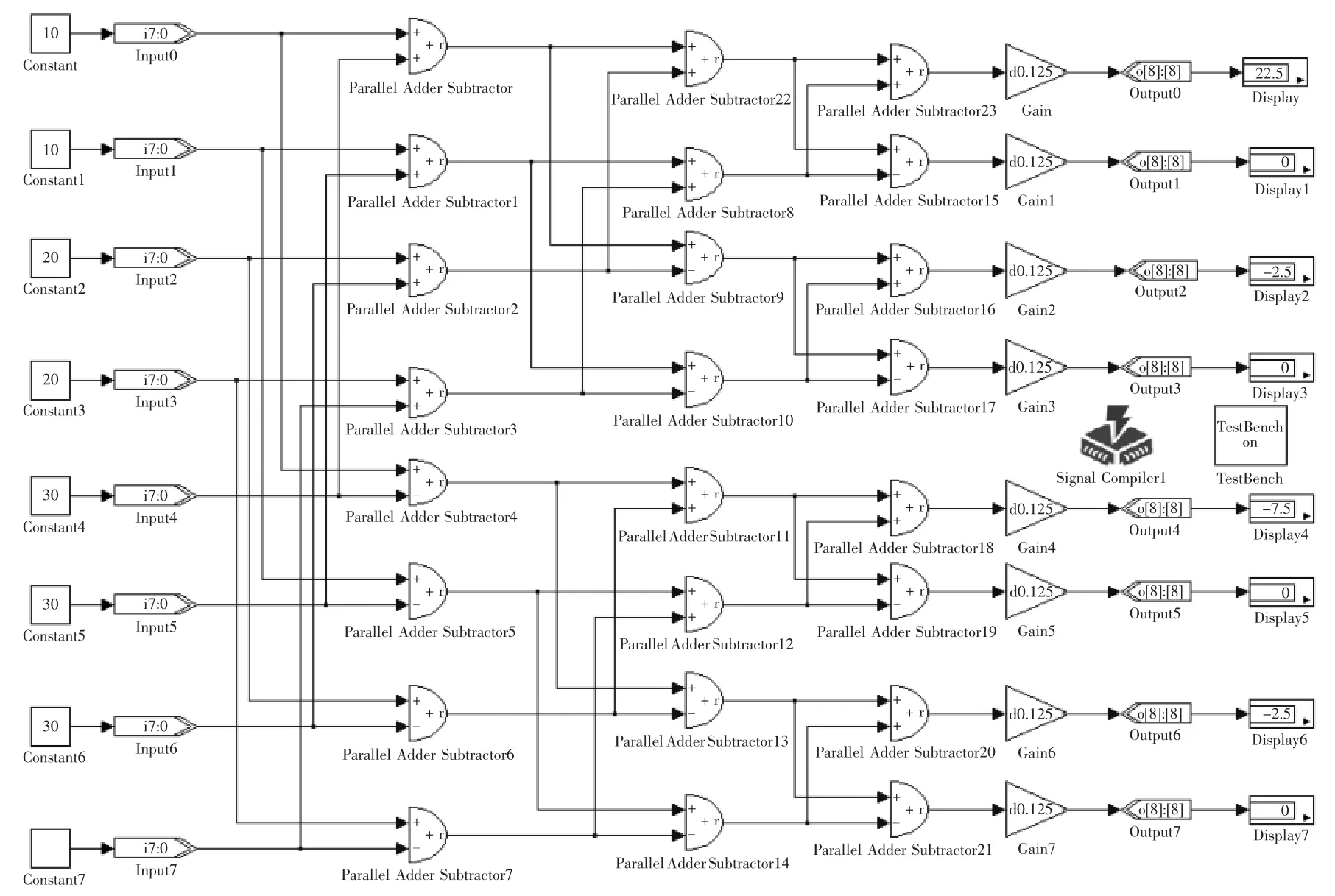

首先利用DSP Builder设计快速哈达玛变换的图形化模型,主要结构如图2所示。

令输入序列input0~input7的值分别为10、10、20、20、30、30、30、30,运行测试,输出结果为:Output0:22.5;Output1:0;Output2:-2.5;Output3:0;Output4:-7.5;Output5:0;Output6:-2.5;Output7:0。

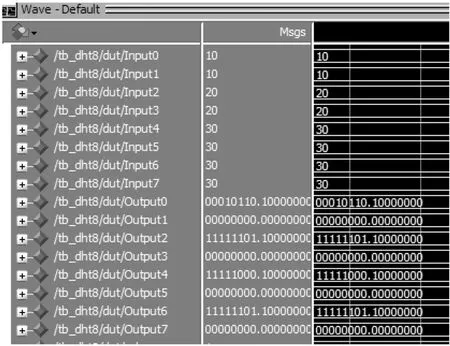

模型经 Simulink仿真后,运行“Signal Complier”之后可以转换为硬件描述语言,并产生测试向量文件。利用Modelsim对测试向量文件进行RTL级仿真,仿真输出数据如图3所示。

通过对比可知,Simuink、Modelsim和Matlab三处仿真结果一致,说明该模型能够完成快速哈达玛变换的运算。

3 结论

本文利用DSP Builder、Simulink和Modelsim等平台,对常见的哈达玛变换的快速算法进行了模型设计与仿真。模型与仿真以8点哈达玛变换的运算为例实现,实际中可以很容易地推广至多点或二维变换的情形。整体设计是基于图形模型的方式,减少了代码编写的工作量。而且目前很多型号的FPGA支持浮点运算,可以方便的物理实现。

图2 快速哈达玛变换的DSP Builder模型

图3 Modelsim仿真结果