一种雷达信号处理机程序切换方法

周威威, 陶 翠, 金垭梅, 李宇翔, 李梦妍

(上海无线电设备研究所,上海201109)

0 引言

近年来,得益于性能的快速提升,雷达在国防[1]、交通[2]、测绘、汽车、无人机[3]等领域的应用越来越广泛。雷达信号处理机作为雷达系统的重要组成部分,是雷达算法的运行平台和硬件基础,主要负责采样数据的处理与分析。FPGA+DSP是现代雷达信号处理机的主流架构,FPGA和DSP程序的调试和烧写主要通过延伸到单板外的JTAG总线。

日益恶劣的工作环境和更高的性能要求,使得雷达信号处理机的数据处理、搜索、识别、跟踪算法越来越复杂[4]。与人工智能等新型算法的融合,进一步增加了处理机算法架构的复杂性和多样性[5]。雷达系统测试时通常需要对比多种算法,从中筛选出综合性能最优的方案。为实现高可靠性,雷达系统需要在整机状态下充分测试[6]。一方面,现有雷达信号处理机JTAG总线烧写速度慢、误码率高、抗干扰能力差,通常只延伸到单板外,因此整机状态下不能通过重烧程序来切换算法,只能通过远程通信更改部分参数;另一方面,高拟真度仿真环境和极端测试环境搭建困难,可供测试的时间有限。另外,可定制化要求雷达整机能够根据部署环境和部署策略快速切换算法程序。综上所述,雷达整机测试、验证和部署都需要处理机能够进行多程序远程快速切换,以便在尽可能短的时间内充分验证多种程序方案和进行定制化部署。

1 处理机硬件设计

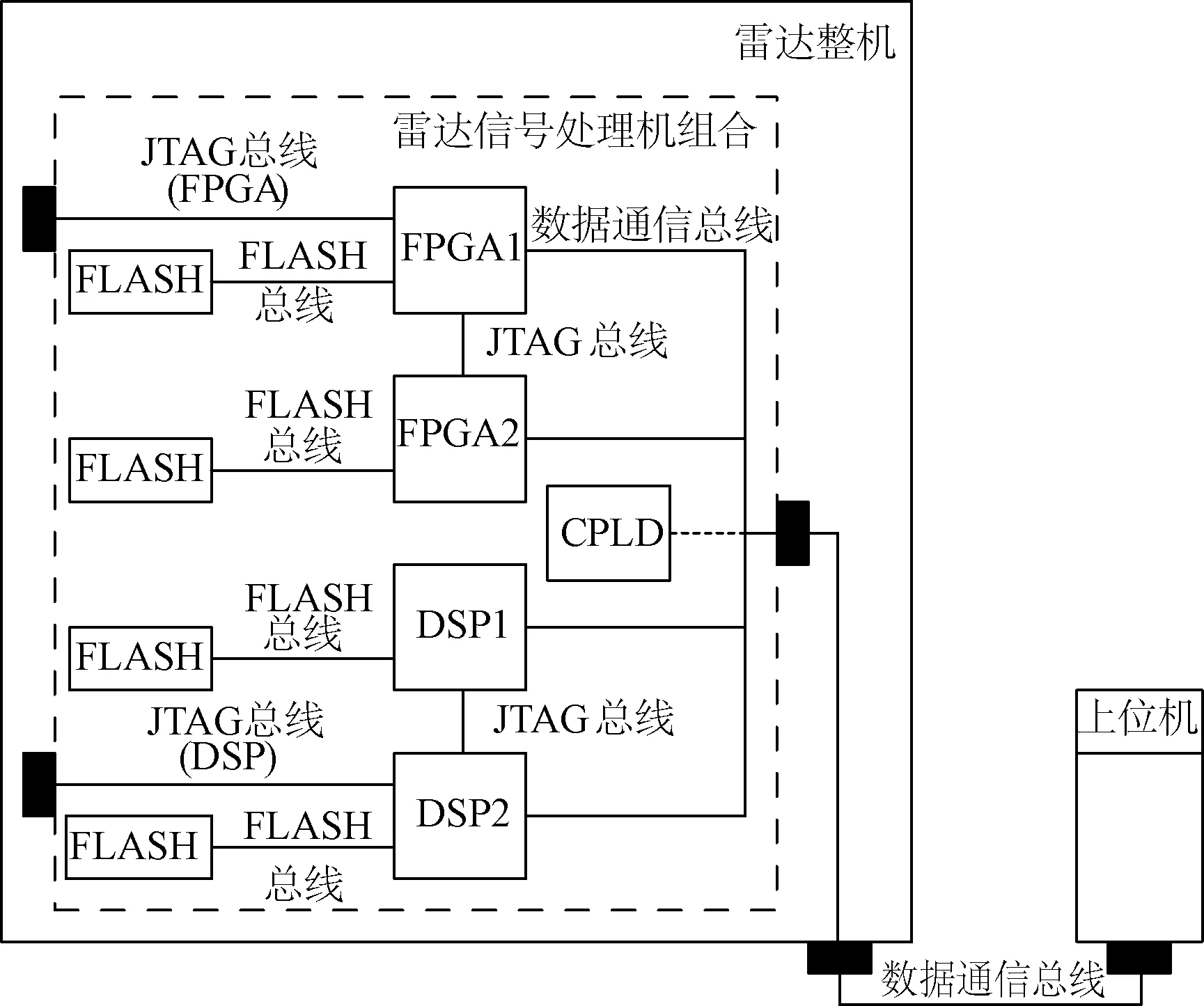

常见的雷达信号处理机组成框图如图1所示。其中:两片FPGA芯片用于模数转换芯片、时钟芯片和交换芯片等外围器件的驱动控制,数字信号预处理,算法加速和接口控制等;两片DSP芯片用于大规模数据运算和复杂算法顺序执行等;一片CPLD控制板上电源芯片,在上电时满足各FPGA和DSP芯片的启动时序要求。每片FPGA或DSP芯片分别通过FLASH总线与一片FLASH芯片相连。上电后,FPGA和DSP芯片自动读取加载保存在各自FLASH芯片中的程序,完成处理机启动。

图1 雷达信号处理机框图

两片FPGA芯片通过JTAG总线串联后连接至单板外部接插件,用于单板状态下的FPGA程序在线调试和烧写。两片DSP芯片也采取同样的连接方式。所有FPGA与DSP芯片均接入数据通信总线,总线连接外部测试设备上位机(CPLD芯片不接入总线)。数据通信总线用于雷达整机状态下各单板芯片间数据交互,也用于上位机传输测试命令与测试数据、监控测试状态。常用的数据通信总线包括1553B、SRIO、CAN、RS422等。

目前,雷达信号处理机中的DSP和FPGA芯片对应的配置FLASH中只烧写一个程序,与其他单板一起装入雷达整机进行测试。测试中处理机各芯片加载程序不能修改更换,若要更换只能拆开整机,取出处理机单板,用仿真器通过JTAG接口烧写新程序后重新装回整机。随着技术的发展,在雷达整机状态下快速进行处理机程序远程切换的需求越来越迫切。虽然FPGA部分可重构和DSP参数远程更新技术可以在一定程度上缓解需求,但也会带来新的问题:片上资源浪费,实现难度大,不能整个程序切换等。

为实现雷达信号处理机多程序远程快速切换,对处理机硬件进行设计改进。如图1虚线所示,将CPLD芯片接入数据通信总线,使得CPLD能够接收上位机发出的控制信号,通过CPLD配合上位机复位重启FPGA与DSP芯片,实现程序切换功能。

2 多程序切换策略

由于FPGA芯片和DSP芯片具有不同的程序加载方式,因此需要对其采用不同的程序切换策略。

2.1 FPGA多程序切换

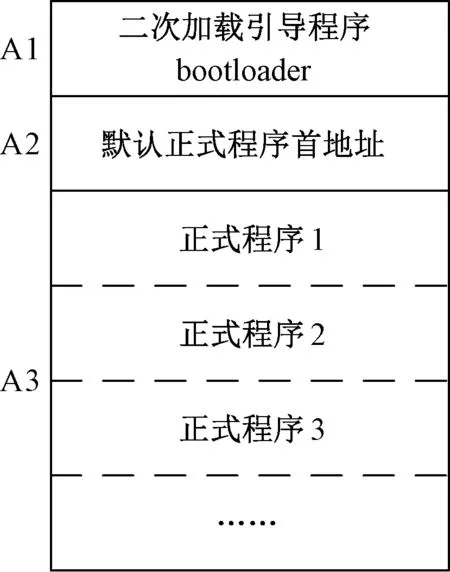

图2 FPGA的FLASH芯片存储区域划分

FLASH存储空间共分为三个区域:A1跳转程序存储区,A2默认正式程序首地址存储区,A3正式程序存储区。A1区域从地址0x0开始,存储FPGA跳转程序,FPGA上电或复位重启后自动加载此程序与上位机通信,确定要加载的正式程序首地址后进行跳转。A2区域中存储默认正式程序的首地址,用作跳转程序在没有从上位机接收到有效的跳转地址时加载默认正式程序。A3区域中保存有多个完整的FPGA正式程序,跳转程序执行后会从此存储区中选择一个正式程序进行跳转。在ISE i MPACT工具或Vivado中将多个FPGA工程文件(.bit)和数据文件合成为FLASH烧写文件(.mcs),通过FPGA的JTAG接口烧入FLASH中。

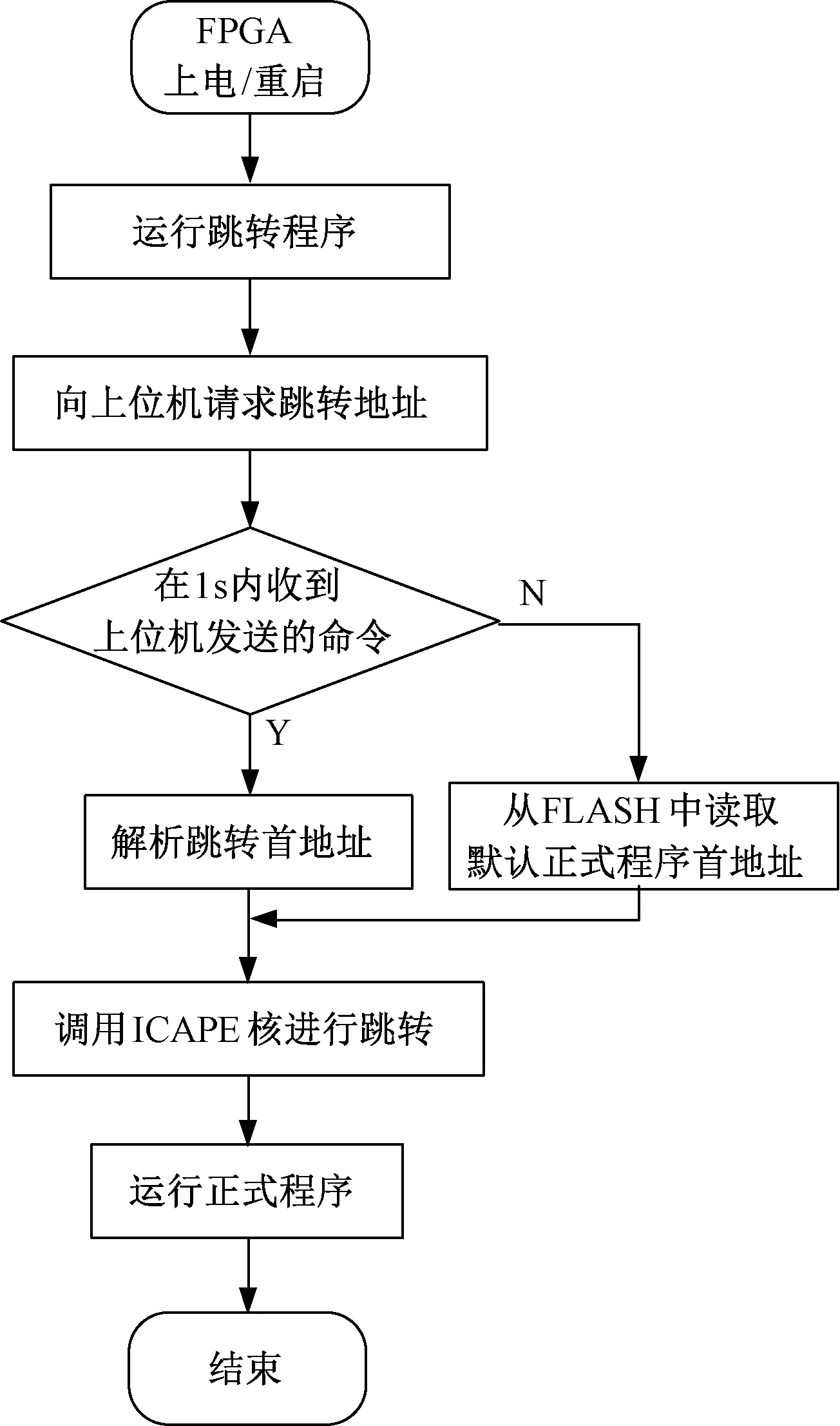

雷达信号处理机FPGA芯片多程序远程快速切换流程如图3所示。在FPGA上电或被CPLD重启后,首先加载运行跳转程序,通过RS422等数据通信总线向上位机请求跳转地址。如果在1 s内收到有效的跳转命令,则解析出跳转地址,否则从FLASH中读取默认正式程序首地址作为跳转地址。确定跳转地址后,FPGA将调用ICAPE核进行指定首地址的程序跳转,并自动重启,从该地址加载运行正式程序,完成程序切换。

图3 FPGA多程序远程快速切换流程图

2.2 DSP多程序切换

DSP的FLASH芯片存储空间分为三个存储区域,如图4所示。A1区域中存储DSP芯片的二次加载引导程序bootloader,用于DSP启动后C语言运行环境搭建,通信接口初始化,与上位机通信选择要加载正式程序的首地址,从FLASH中读取正式程序加载进内核等。A2区域中存储DSP默认正式程序首地址。A3区域中保存多个正式程序,其中所有正式程序都不包含二次加载引导程序bootloader。采用CCS软件编译得到DSP正式程序的.out文件,通过TI公司官方格式转换软件hex6x转换为.hex文件,通过JTAG接口烧入DSP的FLASH中。

图4 DSP的FLASH芯片存储区域划分

DSP芯片多程序远程快速切换流程与FPGA芯片类似,如图5所示。区别只在于DSP可以直接在二次加载引导程序bootloader中与上位机通信,获取要加载正式程序首地址后,直接从FLASH中将该地址对应的正式程序加载进DSP内核并运行。

图5 DSP多程序远程快速切换流程图

3 方案实施

本文选用的FPGA芯片为XILINX公司的XC7K325T,DSP芯片为TI公司的TMS320C6678,FLASH芯片为SPANSION公司的S29GL01GS,CPLD芯片为INTEL公司的EPM1270G,数据通信总线为RS422总线,上位机为Lab VIEW程序。根据不同的工作场景,对雷达信号处理机采用不同的程序加载模式,同时采取多种措施确保安全和方便使用。

3.1 程序加载模式

FPGA和DSP芯片在上电或重启后1 s内根据上位机指令选择要加载的正式程序,上位机通过CPLD芯片控制指定芯片的重启。因此,雷达信号处理机有上电运行、上电切换、重启切换三种程序加载模式。

(1)上电运行默认程序

正常上电,1 s内无上位机命令或FPGA与DSP芯片收到“启动默认程序”命令时,各芯片从A2区域读取默认正式程序首地址,执行程序跳转或加载。

“去你的!”柳红推了一把苏秋琴,刚巧推到她敏感的部位。苏秋琴就故意哎唷唷地呻吟起来,还狠狠地拍了一下柳红的屁股。柳红倒不觉得痛,感觉麻酥酥的。她也在苏秋琴的屁股上回敬了一巴掌。苏秋琴又趁机抓了一把柳红的胸膛。俩人在井边打打闹闹的,气氛就有些暧昧了。

(2)上电切换正式程序

正常上电,1 s内FPGA与DSP芯片收到上位机“切换程序”命令,从中解析出要执行程序切换的器件编号和各自的切换程序首地址,相关器件从解析出的地址加载正式程序,其他器件加载默认程序。

(3)重启切换正式程序

雷达信号处理机正常运行时,CPLD接收到上位机“重启芯片”命令,从中解析出器件编号并重启对应芯片。上位机在FPGA或DSP芯片重启1 s内发送“切换程序”命令,重启芯片解析出各自要切换的正式程序首地址后完成跳转。

3.2 改进措施

为提高稳定性和安全性,并扩展系统功能,本文方案采取了多项改进措施。

(1)可更换默认正式程序

为方便在工程中应用,增加默认程序更换功能。更换时,处理机正常运行,上位机向CPLD发送“重启芯片”命令,完成对应芯片重启。上位机在芯片重启1 s内发送“更换默认程序”命令,重启芯片解析出各自要更换的默认正式程序首地址,擦除各自FLASH中A2区域并将解析出的地址写入,完成默认正式程序首地址的更换。

需要注意的是,FLASH芯片在写操作之前需要先进行擦除操作,擦除以硬件分区(sector)为最小操作单元进行。如表1所示,试验中采用的S29GL01GS芯片存储空间大小为128 Mbytes,从地址0x0开始分为1 024个128 kbytes的硬件分区。更换默认正式程序操作需要对A2默认正式程序首地址存储区域进行擦除与写入,因此需要将A2区域边界与FLASH硬件分区对齐,即只能使用1 024个硬件分区中的一个或者连续数个。

表1 FLASH段划分和硬件分区示意图

(2)严格的校验机制

采用多种方式确保通信内容完整准确:通信帧中均包含循环冗余校验(CRC),连续多个特殊帧指代单条命令,指令帧回传二次校验,FLASH修改内容回传校验。RS422通信总线中上位机为主,其余各芯片为从,采取应答式通信方式。上位机单条指令包含控制内容和数据内容,控制内容由事先约定的连续多个特殊帧指代。各芯片解析出控制命令与数据后,需要回传上位机确认后才会执行此指令,修改A2区域FLASH存储内容后需要读取修改后内容并回传上位机进行校验。

(3)全面的状态监测

各FPGA和DSP芯片进入烧写程序或二次加载程序、执行命令、开始跳转,以及CPLD芯片执行重启指令时,都有状态信息回传上位机,可以实时监测通信情况和各芯片工作状态,有助于故障排查。

4 结果与讨论

确定雷达信号处理机多程序远程快速切换方案后,在验证系统中实现并进行测试。测试结果表明:该方案能够在雷达整机状态下实现信号处理机中FPGA与DSP芯片多程序远程快速切换功能;单芯片程序切换时间,即从上位机发出切换命令到切换到正式程序运行的时间,在5 s以内。切换功能由FPGA跳转程序和DSP二次加载程序实现,既能最小化对正式程序的改动,又能不占用正式程序芯片资源。指令传递稳定可靠,状态监测实时全面。

5 结束语

本文对整机状态下雷达信号处理机多程序远程快速切换方法进行了研究。针对常见处理机架构,提出了一种切实可行的方案,实现了FPGA和DSP芯片多程序的快速切换。通过提高雷达信号处理机程序加载的灵活性,有助于实现雷达系统多方案快速测试验证和定制化灵活部署。