基于PXI的LVDS高速通信板卡设计

白宏义,李锦明,郭 淳

(中北大学电子测试国家重点实验室,山西太原 030051)

0 引言

随着电子技术发展,在基于计算机控制的采集系统中,建立采集设备和计算机高速有效的数据传输通道成为至关重要的一环。在采集大容量、高带宽的数据时,PXI接口速度可以达到132 MB/s,数据位能够扩展到64位,有着较大的优点[1-2]。当前,开发PXI总线接口主要使用专用PCI接口芯片PCI9054和PCI9052[3-4],成本较高,开发周期较长。

因此,提出单独采用FPGA实现PXI协议,能够降低成本,加快开发周期,具有一定的工程应用价值。

1 系统总体设计

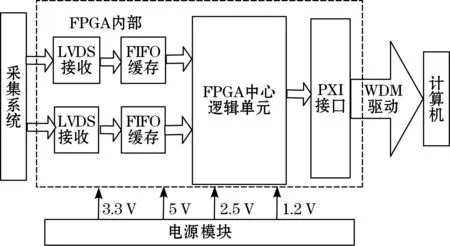

板卡主要作用是接收采集设备发来的2路高速LVDS接口,通过FIFO对数据进行缓存,然后将数据通过PXI接口发送给计算机,上位机对数据进行实时监测。实现PXI接口包括3部分,PXI协议VHDL实现模块,WDM驱动,PXI接口电路。系统的总体设计如图1所示。

图1 总体设计框图

2 系统硬件电路设计

2.1 LVDS接口电路

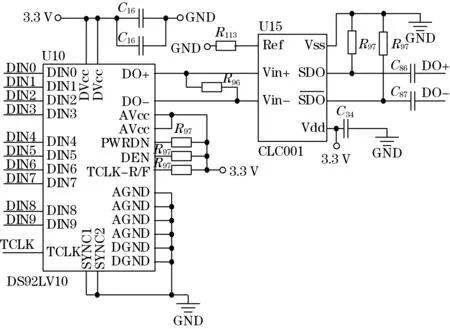

LVDS电路采用的是DS92LV1023和DS92LV1224芯片,能够产生低压差分信号,DS92LV1023内部有10位并行总线,能够实时将10位并行数据转成内部包含时钟的高速串行数据,DS92LV1224可以将内部包含时钟的高速串行数据转成并行数据,将内部的时钟信号剥离出来,进行时钟重建。同时,FPGA作为主控芯片,可以实时完成TCLK和RCLK的同步,从而保证了大容量数据高速稳定传输[5-6]。如图2和图3所示是两组芯片硬件电路设计。

图2 LVDS发送端电路设计图

2.2 PXI接口电路

主控芯片FPGA采用EP2C35F484C8,速度为-8,编译后系统速度可以达到133 MHz[7]。PXI接口涉及到诸多信号,信号根据不同功能可以分为几种类型。PXI接口作为一个功能模块,通过FPGA芯片的I/O管脚与PXI接口信号组相连[8],如图4所示。

3 系统软件设计

板卡以quartus软件为开发环境进行搭建和实现,总体逻辑设计图如图5所示,接收控制模块用来控制LVDS的时序,接收采集系统发来的数据。数据处理模块用来对数据进行编帧,串并转换等操作。PXI协议VHDL实现模块用来实现PXI协议和接口逻辑,并控制PXI接口时序进行PXI总线与FPGA进行数据交互。测试台发来数据,接收控制模块接收数据并将其放入4K的FIFO模块中;数据处理模块对收到数据加上帧头帧尾等标志。随后数据进入16K的FIFO模块,根据full2信号判断FIFO模块的数据量,如果达到标定的数据量,控制PXI总线对数据进行读写操作。

图3 LVDS接受端电路设计图

图4 PXI接口电路

图5 软件设计总体框图

3.1 PXI协议VHDL实现

板卡设计的PXI接口包含4个模块,如图6所示。

图6 PXI接口

3.1.1 配置空间设置

该模块用来定义PCI配置空间。配置空间共有16个寄存器,即16个双字空间,AD(5∶2)就对应这16个地址。第1个地址的高16位是板卡的设备ID号:4258;第1个地址的低16位是板卡的供应商ID号:1100。PCI配置空间有6个基址寄存器Base 0-5,板卡主要用到两个基址寄存器。

Base0寄存器:分配一段地址空间给FPGA的内存寄存器,用内存映射的形式访问FPGA的内存寄存器。

Base1寄存器:分配一段地址空间给FPGA的IO寄存器,用I/O的形式访问FPGA的IO寄存器。

3.1.2 接口逻辑

接口逻辑包含两部分:地址译码,命令译码。地址译码是对总线发来的地址进行锁存,用来判断设备是否应该响应当前总线操作;命令译码是对总线锁存的命令类型进行锁存:对总线发来的不同命令做出相应的操作。在地址和命令传输结束后,总线在过程中成为数据总线,用于传输数据。

3.1.3 奇偶校验

在地址段和数据段中,奇偶校验对地址数据总线和命令操作位的正确性进行保护。既对AD(31∶0)与CBE(3∶0)进行校验。PXI数据总线校验保证0数据误码。

3.1.4 状态机

PXI总线传输主要通过帧开始标志信号FRAME;初始化设备选择信号IRTY;目标设备准备就绪信号TRDY;设备选择命中信号DEVSEL;总线命令和字节允许信号CBE;地址数据复用信号AD进行控制。图7为PXI读写操作状态机,共分为5个状态,S1是空闲状态,S2是地址或过渡状态,S3是忙状态,S4是传输状态,S5是停止状态。

S1状态是PXI设备的初始状态,如果FRAME=1或者IRDY=0,一直保持该空闲状态。当FRAME=0和IRDY=1,S1进入S2状态 即是地址过渡状态,开始进行地址周期,主要是对地址,命令和FRAME进行判断。主设备IRDY低电平表明准备接收发来的第1个数据项。当主设备IRDY和FRAME同时低电平且DEVSEL=1时,表明它已经完成交易的第一个数据段并且进入S4状态。如果IRDY和FRAME没有同时为低,一直维持S2状态。如果信号DEVSEL=0进入S3状态,表示主设备不进行采样操作,同时目标还没有声明交易,即总线访问的地址没有命中,处于总线忙状态。IRDY和TRDY同时低电平,表明数据是完整,成功地读取了第一个(且唯一的)数据项。在状态S4的时候 如果FRAME变低,开始进入停止状态,在S3状态时,如果FRAME变低,开始进入停止状态。

图7 读写状态机

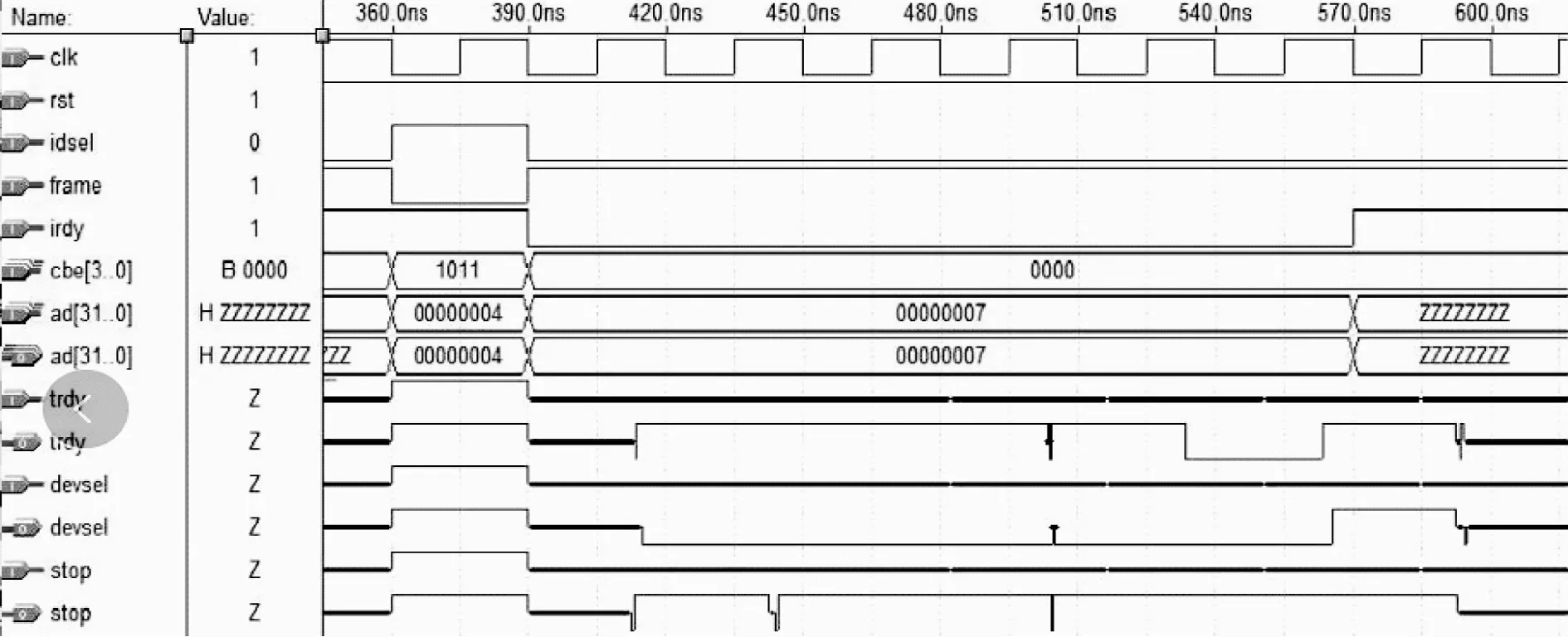

3.2 PXI读写时序仿真结果

用QuartusⅡ 12.0下的SignalTap工具对PXI信号进行捕捉,得到PXI读写操作时序如图8和图9所示。图6中AD(31∶0)输出值为42581100,表示设备的ID号是4258,供应商ID号是1100;CBE(3∶0)输出值为1010表示进行配置空间读操作。图7中CBE(3∶0)输出值为1010表示对配置寄存器进行写操作,AD(31∶0)输出0X4是地址,0X7是数据,表示向配置寄存器地址0X4写入数据0X7。

图8 PXI读操作时序

图9 PXI写操作时序

读写时序说明:

第1个周期:主机把FRAME信号拉低,IRDY拉高说明一个新的PXI操作开始;主机把CBE(3:0)置对应操作位;主机把AD(31:0)置地址操作位;设备卡检测到主机发起新的PXI操作;设备卡锁存CBE命令信息;设备卡锁存AD(31:0)的地址信息。

第2个周期:主机把FRAME信号拉高,IRDY拉低;设备卡检测CBE命令操作,确认是哪种操作类型:IO操作,内存操作,配置操作;设备卡检测地址信息,确认是否本卡。

第4个周期:设备卡将TRDY信号拉低,当前PXI交易完成。

第5个周期:主机将IRDY和FRAME拉高,确认交易完成;设备卡将DEVSEL,TRDY,STOP拉高,确认交易完成。

第6个周期:主机将IRDY和FRAME释放三态,当前交易结束;设备卡将DEVSEL,TRDY,STOP释放三态,当前交易结束。

3.3 WDM驱动

WDM驱动程序是PXI总线连接到计算机的软件接口。在计算机上安装DRIVERWORKS 2.7和2000DDK驱动等工具,自动生成驱动框架,用户只需要在它的框架之下,添加用户自己的代码用来实现PXI读写功能[9-10]。

用户代码的操作句柄为NTSTATUSPcitioDevice::PCITIO_IOCTL_INTCSR_Handler(KIrp I),用来实现PXI读写操作。

4 测试

控制LVDS采集发来的一路数据,并通过PXI接口发送给计算机的上位机。以收到的一路数据为例,如图10所示,上位机收到的部分数据。“14 6F”作为数据帧头,“EB 90”作为数据帧尾,中间为数据,从01到FF一共255个字节。

With the effective mass approximation, the time-independent one-dimensional Schrödinger equation of an electron in MQWs in the z direction can be written as

图10 数据帧格式

上位机接收完毕后,点击软件上的“读取数据”按钮,设备开始读出的数据同时将数据保存到计算机中。上位机软件上传数据界面如图11所示。

图11 上位机上传数据界面

数据完全保存之后,点击软件上的“数据分析”按钮对数据中的丢帧和错误帧进行分析等。分析结果如图12所示。

图12 数据分析结果

一共收到2 048 MByte数据,总帧数为7C97D9。经软件分析没有出误码或数据丢失情况,数据传输稳定可靠。

板卡的测速界面,如图13所示。上位机对从PXI接口收到的数据执行1 500次读取操作,一次读取512 KB,通过测试得知,一共用了7 s完成1 500次采集,根据速度公式:1 500×0.5 MB/7s=107 MB/s,速度较快。

图13 上位机界面

5 结束语

该设计单独使用FPGA实现了PXI接口,节约了PCI9054、PCI9052等专用PCI芯片,可以降低成本,加快PXI接口的开发周期。同时,速度可以到达107 MB/s,误码率和数据丢失情况基本为0。再结合LVDS、PXI和FPGA优点可以有效解决采集设备与计算机的高速数据传输问题。