码率兼容空间耦合LDPC码编码器与译码器设计

张恒皞,丛惠平,赵旦峰

1.哈尔滨工程大学信息与通信工程学院,黑龙江哈尔滨150001

2.中国人民解放军91033部队,山东青岛266071

移动通信系统具有可靠和高效的特点,对于具有时变特性的无线信道,需要能在不同信道条件下进行可靠数据传输的传输方案。低密度奇偶校验(low density parity check,LDPC)码是一种能够逼近香农信道容量极限的信道编码[1],已经被广泛应用于卫星电视通信[2]、移动无线通信[3]、无线局域网[4]等领域中。空间耦合LDPC(SC-LDPC)码是一种源于LDPC卷积码的新型信道编码[5],理论上被证明可以达到一般二元无记忆对称信道的信道容量[6]。相比于LDPC码,空间耦合LDPC码在特殊的耦合结构下具有优异的性能,在B5G/6G 移动通信系统中具有广阔的应用前景。码率兼容LDPC码是指一组信息位长度相同、码率不同的LDPC码,该组LDPC码在不同的码率下都有较好的性能,并能够使用同一套编译码器实现[7]。文献[8]通过对特殊的三边型LDPC校验矩阵进行扩展和组合,实现码率兼容空间耦合LDPC 码,理论上可以实现任意码率,但对校验矩阵要求较高,在给定的短耦合长度下性能并不理想。文献[9]通过修改LDPC码的校验矩阵结构,在耦合边缘处对矩阵的连接进行不同的组合来现码率兼容,可以实现递归编码。文献[10]采用打孔方式,将随机打孔的码率兼容LDPC码进行耦合,耦合长度大时译码性能较好,但由于打孔操作是随机的,具有不确定性,并且长耦合长度对资源的占用较大。文献[11]提出了一种基于重复累加扩展构造LDPC码的方案,并对其进行耦合,通过对校验矩阵的变量节点进行扩展和耦合实现码率兼容,复杂度较高。

针对以上情况,本文设计并实现了一种码率兼容的空间耦合LDPC码方案,并基于FPGA 进行验证。通过构造码率兼容的基矩阵进行耦合,实现码率兼容的空间耦合LDPC码。编码器直接使用校验矩阵进行系统编码,译码器采用分层最小和译码算法,在保证性能的同时可以减少FPGA中资源的占用。

1 码率兼容SC-LDPC码校验矩阵构造

1.1 空间耦合LDPC码的结构与编码算法

1.2 类Raptor 型LDPC码校验矩阵构造

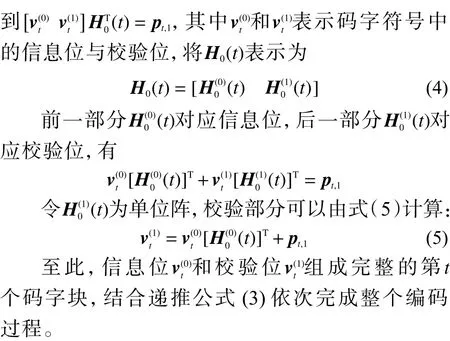

5G标准中增强移动宽带(enhanced mobile broadband,eMBB)场景下使用的LDPC码,采用类Raptor 的扩展型码率兼容矩阵结构,在可以使用校验矩阵进行系统编码的同时实现码率兼容[14],类Raptor 型LDPC码校验矩阵结构如图1所示。

图1 类Raptor 型LDPC码矩阵结构

图中,子矩阵A与子矩阵E是由循环移位矩阵组成的矩阵阵列,子矩阵O为全零矩阵,子矩阵I为单位矩阵。矩阵A对应信息位;矩阵D对应校验位,具有双对角线结构,用于递归编码;核矩阵[A D]对 应高码率部分;矩阵[E I]对应扩展型码率兼容的扩展位;单位阵I对应度为1的校验位。通过高码率码与单校验码串行级联,实现从高码率到低码率的码率兼容。由于子矩阵D与子矩阵I分别为双对角线和单对角线结构,可以利用校验矩阵进行递归编码,无需生成矩阵,编码过程描述如下:

式中上标代表矩阵的循环移位系数,无上标表示矩阵的循环移位系数为0。由于二元LDPC码的加法为模二加,将式(6)右侧方程等号两边相加,有

通过式(7)可以求出v0,将其代入式(6),即可求出v1、v2、v3。由于子矩阵I是单对角线矩阵,利用信息位u和计算出的v,计算其余校验比特为

1.3 码率兼容SC-LDPC码校验矩阵构造

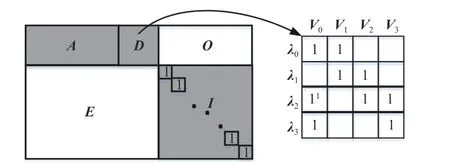

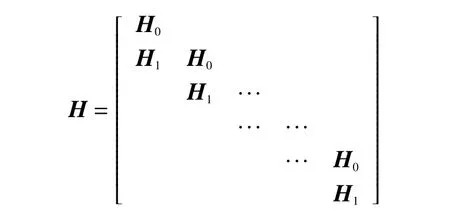

在部分校验子前项编码算法中,式(4)说明了如何利用耦合基矩阵H0计算部分校验子前项,因此,耦合基矩阵的设计对空间耦合LDPC码的部分校验子编码算法实现快速递归编码具有重要意义。基矩阵H0若能利用信息位对应部分和校验位对应部分进行递归编码,则可快速计算出部分校验子前项,实现SC-LDPC码的递归编码。因此,本设计参考类Raptor 校验矩阵结构,构造可递归编码的码率兼容SC-LDPC码的基矩阵H0,如图2所示。

图2 码率兼容基矩阵结构

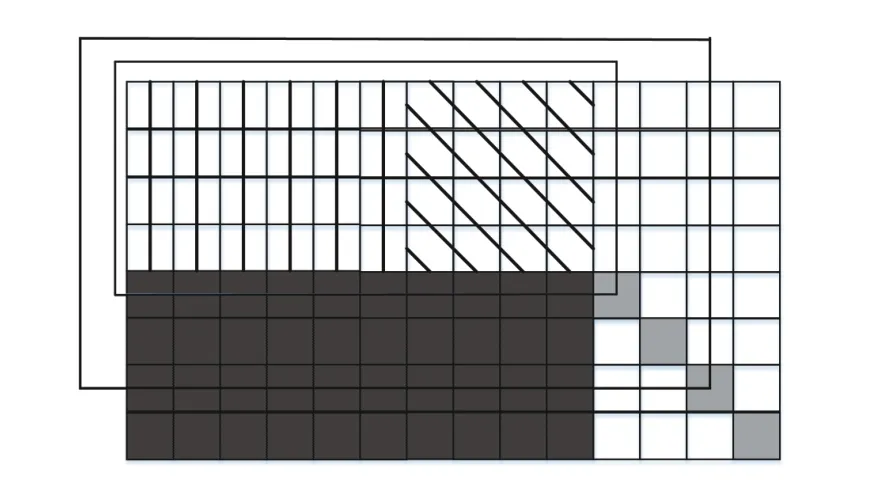

基矩阵H0结构图中,每一个正方形代表大小为32 bit×32 bit 的循环移位单位矩阵,信息位长为192 bit。图中竖线阴影部分对应类Raptor 矩阵中子矩阵A的信息位;斜线阴影部分对应子矩阵D的校验位;黑色阴影部分对应子矩阵E;灰色阴影部分对应子矩阵I的校验位;空白部分对应全零矩阵。图中小矩形部分代表高码率矩阵,大小为128 bit×320 bit,码率为3/5;通过对此高码率矩阵扩展到大矩形部分,构成大小为192 bit×384 bit、码率为1/2的矩阵;再继续扩展,形成最终大小为256 bit×448 bit、码率为3/7的矩阵,至此整个基矩阵H0构造完毕。基矩阵能够使用校验矩阵进行系统编码,适用于SC-LDPC码的部分校验子编码方案;同时无需生成矩阵,有效减少了硬件资源占用。在本设计中,为了使校验矩阵更加稀疏,SCLDPC码校验矩阵的耦合长度设为最小,即约束长度m=1,校验矩阵结构如下:

式中H1为耦合约束关系矩阵,大小与基矩阵H0相同,通过H0与H1进行耦合,构造出SC-LDPC码的校验矩阵。

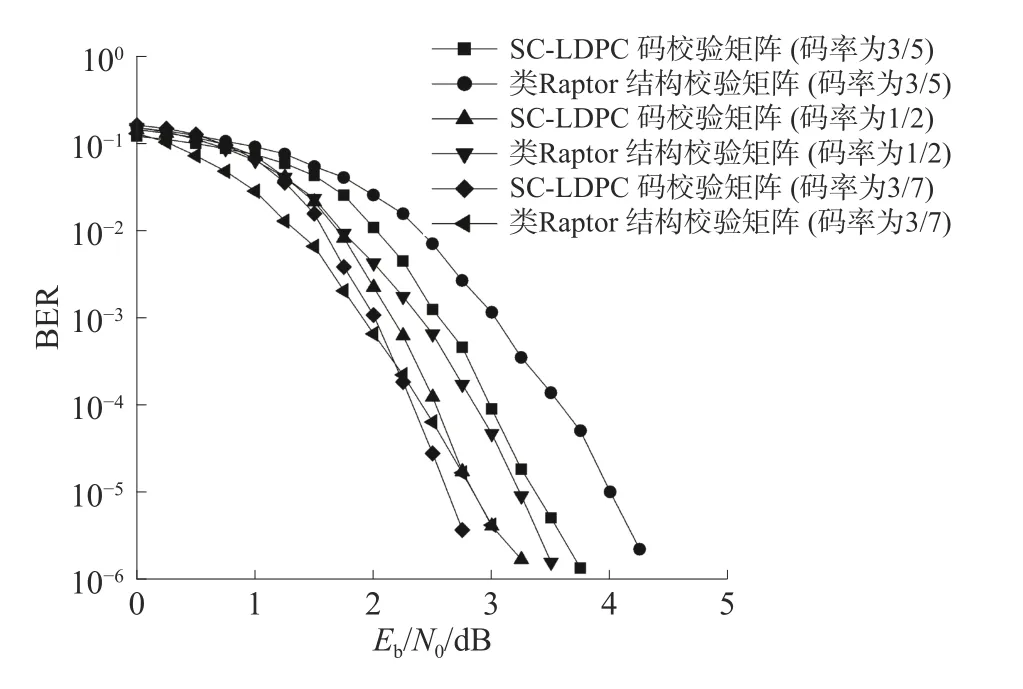

利用5G 标准中的参数构造对应码率的类Raptor 结构校验矩阵,使用BP 译码算法与本文设计的SC-LDPC码校验矩阵进行性能仿真对比,在相同信息位长、最大译码迭代次数为20次、不同码率的情况下,误码率性能如图3所示。图中Eb/N0代表归一化信噪比,BER(bit error rate)代表误码率。可以看出本文所构造的码率兼容SCLDPC 码校验矩阵具有更好的译码性能,并且在BER=10-6时没有出现明显的错误平层。

图3 误码率性能比较

2 码率兼容SC-LDPC码编码器设计

2.1 编码器设计

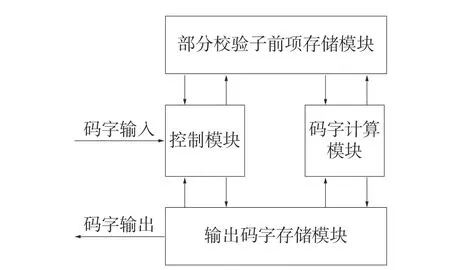

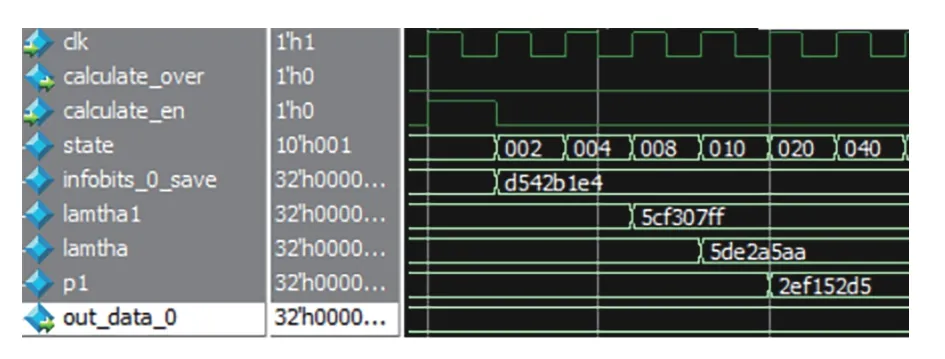

根据部分校验子前项编码算法,编码器主要由控制模块、部分校验子前项存储模块、码字计算模块、输出码字存储模块组成。编码器结构如图4所示。

图4 码率兼容空间耦合LDPC 码编码器结构

当需要编码的码字信息位输入到编码器时,编码器将输入的信息位存储至寄存器中。当信息位接收完毕,编码器开始进行编码。编码器的核心模块为控制模块和码字计算模块。

控制模块对编码过程进行控制。当码字信息位和码率指示信号输入时,控制模块负责对这些信息进行接收;当信息接收完毕后,控制模块根据码率指示信号,对不同的码率情况进行编码运算。校验矩阵为准循环移位矩阵,输入的信息位与校验矩阵相乘等价于对信息位进行循环移位,因此编码器根据输入的码率控制信号来确定不同循环移位单元的计算使能,实现SC-LDPC码在不同码率下的编码。

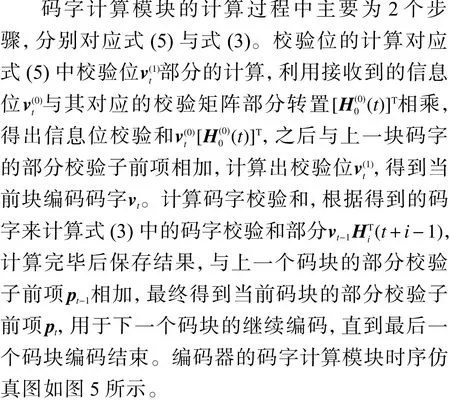

图5 编码器码字计算模块时序仿真

2.2 编码器结果分析

将编码器通过Verilog 硬件描述语言实现,使用Modelsim 10.7软件进行时序仿真,如图6所示。在Xilinx xc7k325tff900-2芯片上进行实现,编码器资源占用如表1所示。

图6 编码器输出结果时序仿真

表1 编码器资源占用表

由于编码器主要采用循环移位和异或运算进行编码计算,计算产生的中间数据存储在循环移位寄存器中,只有部分校验子前项需要在运算前进行读取、在编码完毕后需要进行存储,因此需要少量的RAM 资源来存储部分校验子前项,编码器整体资源占用较低。

3 码率兼容SC-LDPC码译码器设计

3.1 分层译码算法

由于本文构造的SC-LDPC 码校验矩阵属于准循环校验矩阵,从硬件实现的角度考虑,分层译码算法是一种十分适用于准循环结构校验矩阵的译码算法。一方面,分层译码将整个校验矩阵分成多个层,优化了层间的消息传递,使迭代译码收敛速度更快;另一方面,分层译码只需要存储校验节点信息,无需存储变量节点信息,减少了资源占用[15]。假设校验矩阵的大小为M×N,将校验矩阵的M个校验方程分为T组,每组包括M/T行,分层译码算法的具体步骤描述如下:

1)初始化。

3)若伴随式cˆHT=0,则停止迭代,进行译码输出;否则m=m+1,然后转至步骤4)。

4)若m>T,则l=l+1,m=m+1。如果l小于最大迭代次数,则调至步骤2)继续进行迭代译码;否则终止迭代。

在SC-LDPC码的其他译码方案中,文献[16]提出了一种针对SC-LDPC码的特殊结构——修改优化变量节点信息传递规则的译码方式,充分利用变量节点信息进行更新运算;文献[17]提出了一种利用译码后验概率信息进行节点更新的译码方式,增加了可靠性。在信息位长192 bit,码率为1/2,译码迭代次数为20次的情况下,文献[16]、[17]以及本文提出的分层译码与BP译码算法性能如图7所示。

可以看出,本文采用的分层译码方式与文献[16]及[17]提出的译码算法相比,在短信息位长时译码性能较好,没有明显的错误平层,并且与BP译码算法的性能接近;在硬件实现中,可以将变量节点更新单元和校验节点更新单元合并,不需要存储变量节点更新信息,节省硬件存储资源占用。因此,选择分层译码算法作为本文设计的SC-LDPC码的译码算法方案。

图7 本文译码方法与其他文献译码方法性能仿真对比

3.2 译码器设计

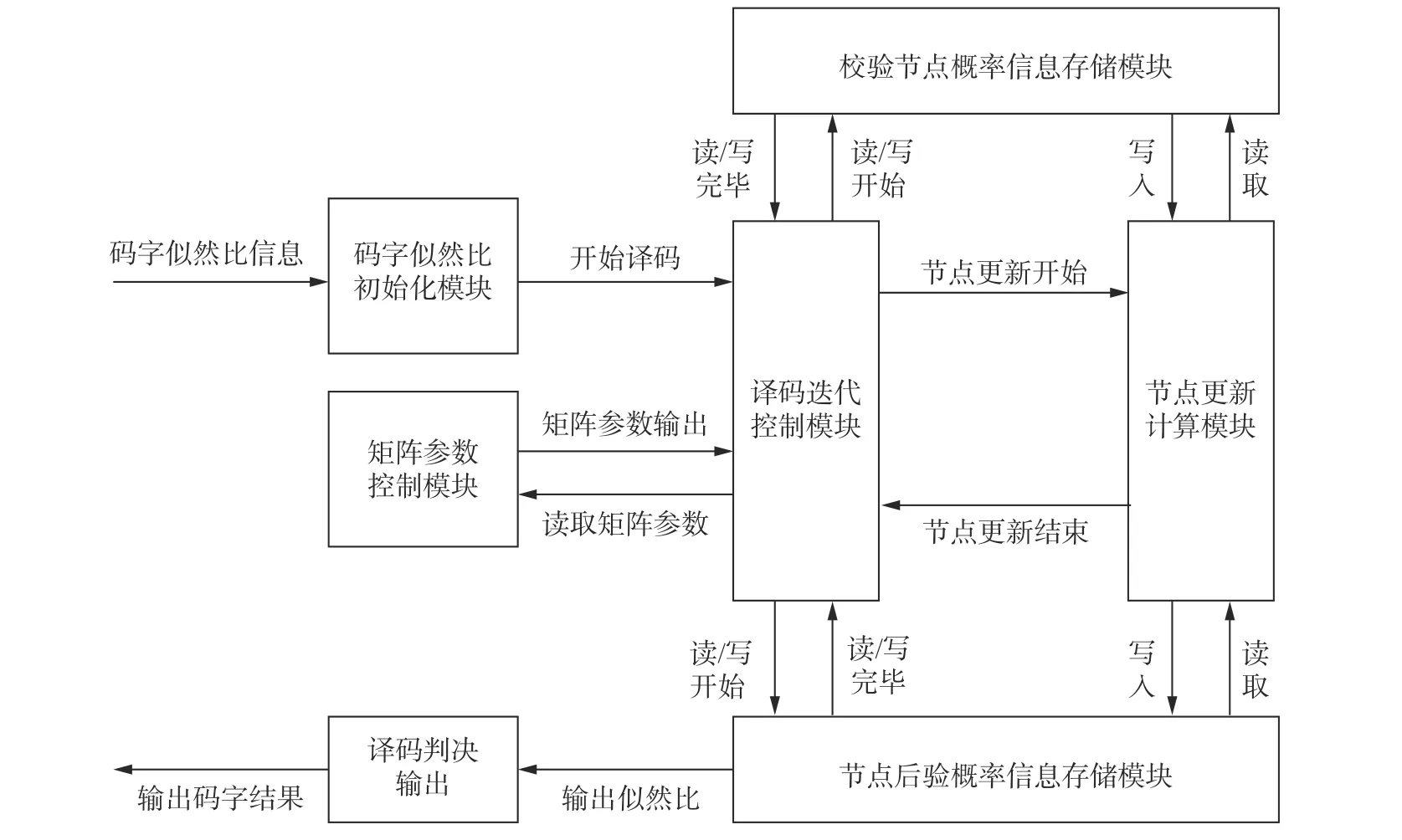

根据分层最小和译码算法方案,结合SCLDPC 校验矩阵,采用分层译码方式,译码器输入数据采用6 bit 量化,最高位为符号位,中间3 位是整数位,最后2位为小数位。译码器结构如图8所示。

图8 码率兼容空间耦合LDPC码译码器结构

译码器主要由矩阵参数控制模块、码字似然比初始化模块、译码迭代控制模块、节点更新计算模块、校验节点概率信息存储模块、后验概率信息存储模块组成。其中,码字似然比初始化模块、校验节点概率信息存储模块与节点后验概率信息存储模块是译码器中的信息存储模块,主要由RAM 组成,用于数据的写入和读取;矩阵参数控制模块由存储着矩阵信息的ROM 组成,存储着矩阵的行列地址索引以及循环移位系数等参数。

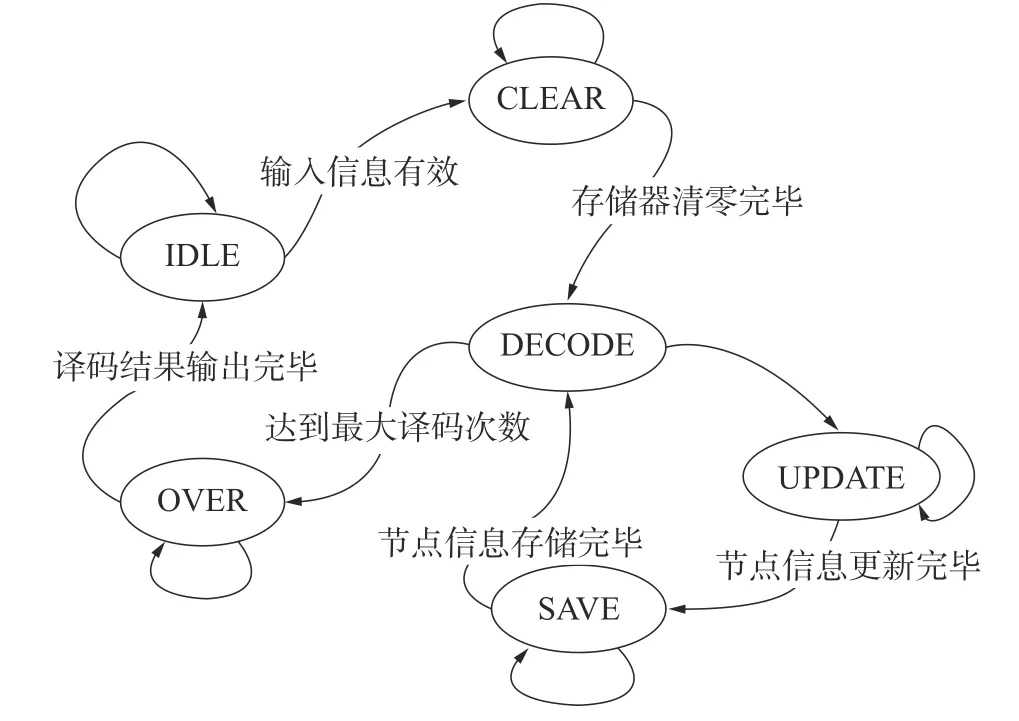

译码迭代控制模块采用状态机实现,共有6 个状态,状态转移图如图9所示。CLEAR 状态负责将节点信息RAM 进行初始化;DECODE 状态读取矩阵相关参数,初始化译码器的控制信号;UPDATE 状态进行节点的信息更新;SAVE 状态对更新后的节点信息进行保存;OVER 状态将译码结果输出,输出完毕后返回IDLE状态。

图9 译码器状态转移

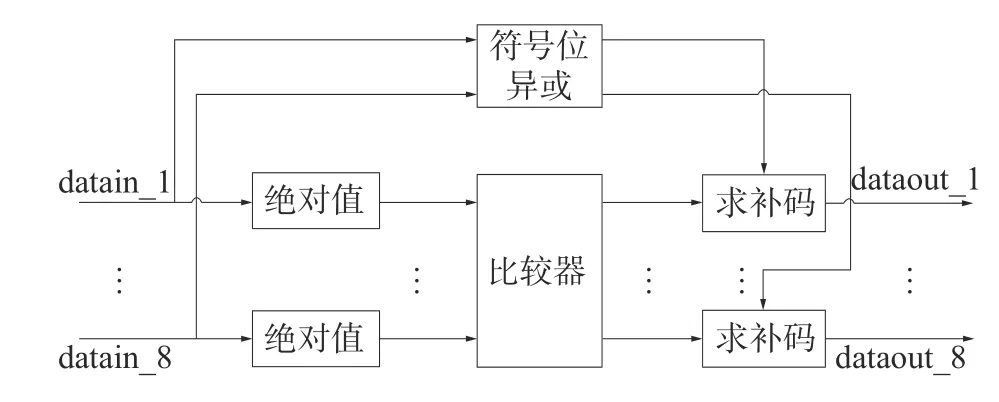

节点更新计算模块的主要功能是进行变量节点的更新和校验节点的信息更新。此模块主要步骤分为有符号加减法运算、符号整理运算、取绝对值最小值运算和乘法运算。首先,读取层存储模块中的上一层校验节点信息以及上一次迭代产生的变量节点后验概率信息,进行相减后得到更新的变量节点信息。之后,进行校验节点信息的更新,主要分为符号位相乘(异或)、求绝对值的最小值和次小值、比较并取补码值3个状态。符号相乘和取模运算是同时进行的,输入数据的最高位为符号位,将其进行异或运算,即符号相乘。求绝对值时,当数据符号为正,截掉符号位,保留其他位;当符号为负,将其他位取反后加一。因为校验矩阵的最大行重为8,所以求最小值和次小值运算需要花费3个时钟,首先将8个输入数据两两比较,分为绝对值大的一组和小的一组;再将绝对值小的一组中的4个数据两两比较,分为绝对值大的一组和绝对值小的一组;绝对值小的一组中比较出最小值,剩下的数据比较出次小值,然后将比较得出的值取补码,校验节点信息更新完毕。最后将更新后的变量节点信息与校验节点信息相加,得到更新后的变量节点后验概率信息,分层译码中的一层译码结束,继续进行下一层译码。节点更新计算模块时序仿真如图10所示,结构图如图11所示。

图10 节点更新计算模块时序仿真

3.3 译码器结果分析

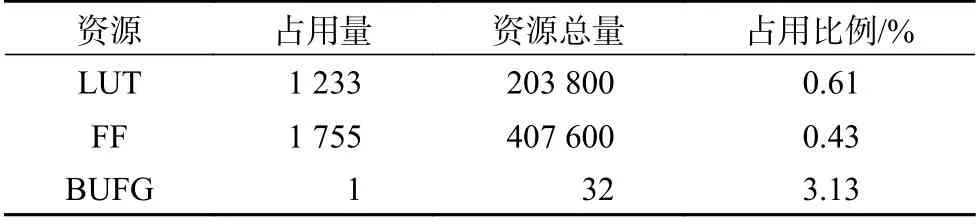

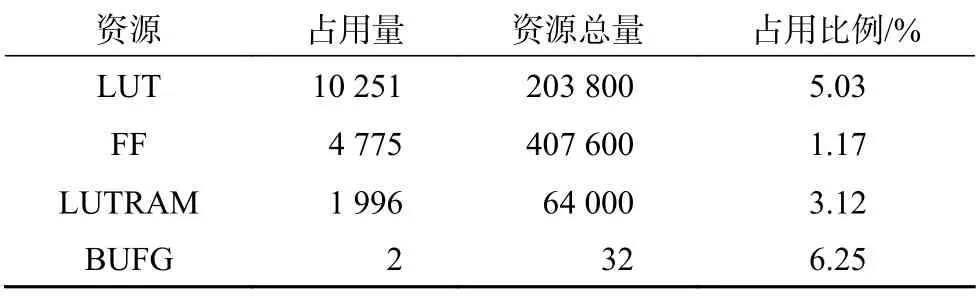

将译码器通过Verilog 硬件描述语言实现,使用Modelsim 10.7软件进行时序仿真,时序波形如图12所示。在Xilinx xc7k325tff900-2芯片上进行实现,译码器资源占用如表2所示。

图11 节点更新计算模块结构

图12 译码器输出波形时序

表2 译码器资源占用表

可以看出,译码器中的节点更新计算单元主要消耗LUT 资源,而后验概率信息与校验节点信息存储模块消耗了一部分RAM资源来进行信息的存储,译码器整体资源占用较低。对译码器进行性能仿真,并与软件仿真结果进行对比,结果如图13所示。可以看出FPGA 中的结果与软件仿真的结果具有0.5 dB左右的差异,一方面是由于输入的信噪比经过量化输入到译码器中,存在量化误差;另一方面是由于最小和译码在迭代更新计算过程中并没有进行和积运算,而是用取最小值作为近似导致的。本文所设计的3种码率在归一化信噪比为3.5 dB时FPGA 仿真的误比特率都可以达到10-5量级,具有较好的译码性能。

图13 BP 译码仿真与FPGA 测试性能对比

4 结论

1)针对无线信道的时变特性,本文设计了一种码率兼容的空间耦合LDPC码,通过对高码率的校验矩阵进行扩展,能够实现3种不同码率的码率兼容,可以适应不同信道条件下的需求。

2)本文基于FPGA 完成了码率兼容空间耦合LDPC码的编码器和译码器的设计。编码器和译码器根据特殊的校验矩阵结构实现码率兼容,在保证编译码性能的同时,具有较低的资源占用和较好的性能,在实际工程应用中具有一定参考价值,可以为B5G/6G移动通信系统提供可借鉴的传输编码方案。