基于FPGA 的计轴信号处理系统

张忠民,李扬,周文生

1. 哈尔滨工程大学 信息与通信工程学院,黑龙江 哈尔滨 150001

2. 黑龙江瑞兴科技股份有限公司,黑龙江 哈尔滨 150030

随着中国经济的高速发展,铁路运输无论在人们的日常出行还是货物运输中都占据着主导地位。中国高速铁路的开通和运行,使人们的出行更加高效、便捷。为确保铁路运输的高效性、安全性,铁路运行中使用很多辅助设备来监管列车的运行状态,计轴设备[1-2]就是其中的一种。计轴设备可以判断轨道区间的空闲或是占用状态,其工作原理是在轨道区段的两侧各安装一套计轴设备,通过对比2 套计轴设备统计的轴数是否相同给出区间的状态,若相同,表明该区间空闲;若不同,表明该区间被占用。

计轴设备的发展经历了机械式、光电式、永磁式、电子式和微电子式的更新换代,目前使用的计轴设备都是微电子式计轴设备。计轴设备根据结构组成,一般分为室内部分和室外部分。室外部分包括计轴传感器和电子连接箱,计轴传感器用来采集车轴信号,电子连接箱用来处理传感器采集到的信号,统计轴数;室内部分包括运算器和接口电路,运算器用来对比各计轴点的数据,接口电路用来实现数据的交换[3]。根据计轴传感器的类型不同,计轴设备大概分为4 种:调相式计轴设备、调幅式计轴设备、电磁振荡式计轴设备和光纤光栅式计轴设备[4]。调相式计轴设备的典型代表有瑞兴JWJ-C 型计轴设备[5]、泰雷兹AzLM-Zp30型计轴设备;调幅式计轴设备的典型代表有西门子AzS(M)350U 型计轴设备[6];电磁振荡式计轴设备的典型代表有富豪舍尔ACS2000型计轴设备[7];光纤光栅式计轴设备的典型代表为武汉理工大学研究的光纤式计轴设备[8-9]。

以上提及的这些典型计轴设备,在电子连接箱处理计轴信号时,大多使用单片机或是单核DSP芯片进行设计,这是由于这些芯片的成本较低。但这些芯片设计的计轴设备在监测高速列车时容易出现丢轴的情况,这是由芯片的内部运行方式所局限的。随着集成电路的发展,FPGA 芯片以处理速度快、精度高、内部并行运行的优点逐步在各个行业中被广泛使用。

本文使用FPGA 芯片完成对计轴信号处理系统的设计,下面通过4部分内容对该系统进行介绍。

1 系统整体设计框架和原理

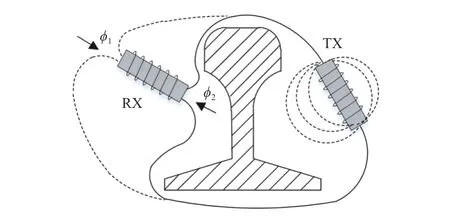

系统设计使用双侧计轴传感器,图1所示为双侧计轴传感器安装在铁轨上的示意图,图中同时给出计轴设备整体的框架。

图1 双侧计轴传感器安装位置示意

由图1可知双侧计轴传感器共包括2对磁头,图中的RX1和TX1组成一对磁头,RX2和TX2组成一对磁头,RX 代表接收线圈,TX 代表发送线圈,RX 安装在钢轨内侧,TX 安装在钢轨外侧,2对磁头的设计和工作原理完全相同,不同点是线圈中信号的频率有所不同。本系统中分别使用24和28 kHz 频率信号作为2对磁头的工作频率。使用这2个频率的信号作为计轴系统的工作频率,是因为经过实测,2个频率信号传输效率高、相互干扰小。

为了形象地说明计轴传感器磁头的工作原理,图2给出计轴传感器磁头安装在铁轨上的截面图。

图2 磁头传感器安装在铁轨上的截面

图中简单地画出了磁头发送线圈的磁感线分布,用以说明磁头线圈的工作原理。发送线圈TX中通以固定频率的交流信号,受铁轨的影响,在接收线圈RX 两端形成固定变化规律的磁场分布。图 中 φ1和 φ2分 别 表 示 穿 过 接 收 线 圈RX 两 端方向不同的磁通量。在无车通过传感器的状态下, φ1的值大于 φ2的值;有车通过传感器时,会改变传感器周围磁场的分布,使 φ2的值大于 φ1的值。因此在有车通过传感器时,感应线圈中产生的感应信号的相位发生翻转。正是利用这一特性,计轴处理系统监测到相位的变化,进行轴计数。

系统传感器使用2对磁头的目的是根据2 对传感器磁头相位发生变化的先后顺序判断列车的行驶方向。

在了解了计轴传感器的安装和工作原理后,对FPGA 计轴信号处理系统进行介绍。计轴信号处理系统为计轴传感器提供工作信号,并接收传感器反馈回来的信号,通过发送信号和接收信号的相位差来判断是否有车轮通过传感器,有则进行计数,最后将轴数信号上传。为了保证系统安全的工作,系统设计时考虑到多方面的安全可靠性因素,对其进行设计。首先,系统设计使用“1+1”冗余的设计方案,当其中一套计轴信号处理系统出现故障时,可以启用另外一套计轴处理系统工作;其次,一套计轴信号处理系统使用2块信号处理板,对2对磁头分别进行信号处理、计数;最后,每一块板上都有监测各部分是否正常工作的监测模块。

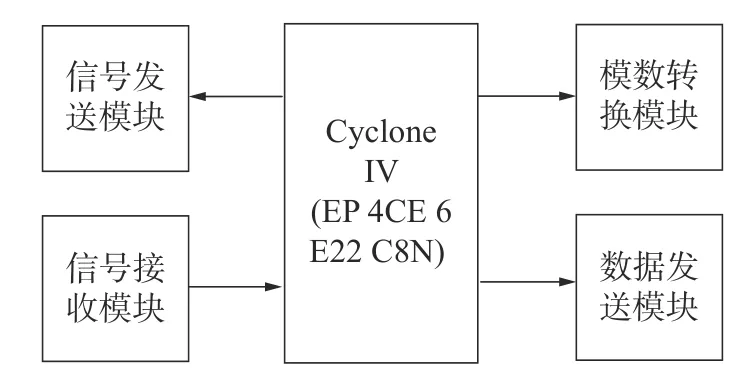

图3所示是一套计轴信号处理系统的结构框图,包括24 kHz 信号处理板、28 kHz 信号处理板、电源板。24 kHz 信号处理板和28 kHz 信号处理板的设计结构和工作原理完全类似,只是工作的频率不同,因此在下面介绍计轴信号处理系统硬件电路设计和软件设计时,主要以24 kHz 信号处理板为例进行说明。

图3 计轴信号处理系统结构

2 系统硬件电路设计和测试结果

以24 kHz 信号处理板为例,说明系统信号处理板的硬件电路设计,具体如图4 所示,包括信号发送模块、信号接收模块、模数转换模块、数据传输模块。

图4 信号处理板硬件模块关系框图

2.1 信号发送模块

以24 kHz 信号处理板为例,信号发送模块是通过FPGA 芯片内部产生24 kHz 的方波信号,然后经过信号发送模块处理要发送的信号,图5所示是信号发送模块电路图。

图5 信号发送模块电路

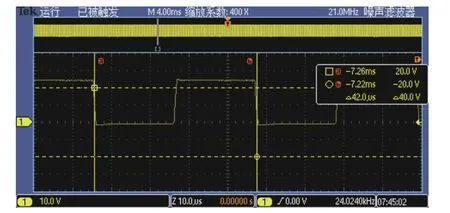

由图5可知信号发送模块最左端连接FPGA信号发送引脚。图6表示FPGA 引脚发送出信号的波形图。FPGA 引脚端发送的信号为方波信号,高电平为3.3 V,低电平为0 V。

图6 FPGA 信号发送引脚波形

信号发送出来后经过电容C1隔直后,再经过R4和R5分压,将分压后的信号经过三极管Q3(S8050)放大,放大后的波形图如图7所示。由图可知信号经过三极管单管放大后方波的高电平值达到了24 V,低电平为0 V,信号依然保持方波形状。

图7 信号经过三极管S8050后信号波形

此后,信号经由二极管D1(1N4148)、三极管Q1(C2383)、Q2(A1013)组成的OTL甲乙类互补对称电路进行功率放大,放大后的信号波形如图8所示。这是在变压器线圈FS的主线圈测得的波形图,由图可知信号波形有一定失真,高电平值为12 V,低电平值为-12 V。

图8 信号经过OTL 甲乙类互补对称电路后的波形

最后,信号经过变压器线圈FS耦合到变压器的副级线圈。在副级线圈一端,变压器的副级线圈、磁头发送线圈、电容(2个并联的电容C4和C5)组成串联谐振回路,谐振的中心频率点为24 kHz。组成串联谐振回路的目的是为了在磁头发送线圈的2端获得类正弦波,同时获得较高的电压幅值。已知谐振的中心频率,同时可以测出变压器副级线圈的电感和磁头发送线圈的电感值,由串联谐振回路谐振频率的计算公式可知,需要的电容的容值约为90 pF左右,故电路设计中电容C4和C5的值分别为30 pF和56 pF。图9所示为磁头发送线圈两端的波形图,由图可知磁头发送线圈信号波形接近于正弦波,信号最大值为48 V。

图9 磁头发送线圈两端信号波形

图5中FS1、FS2和FS3这3个点是发送回路测试点,通过测试这3个点的电压值来判断发送回路是否正常。将这3个监测点的信号进行处理,然后在模数转化模块下采样,监测分析在3.2节中给出。

2.2 信号接收模块

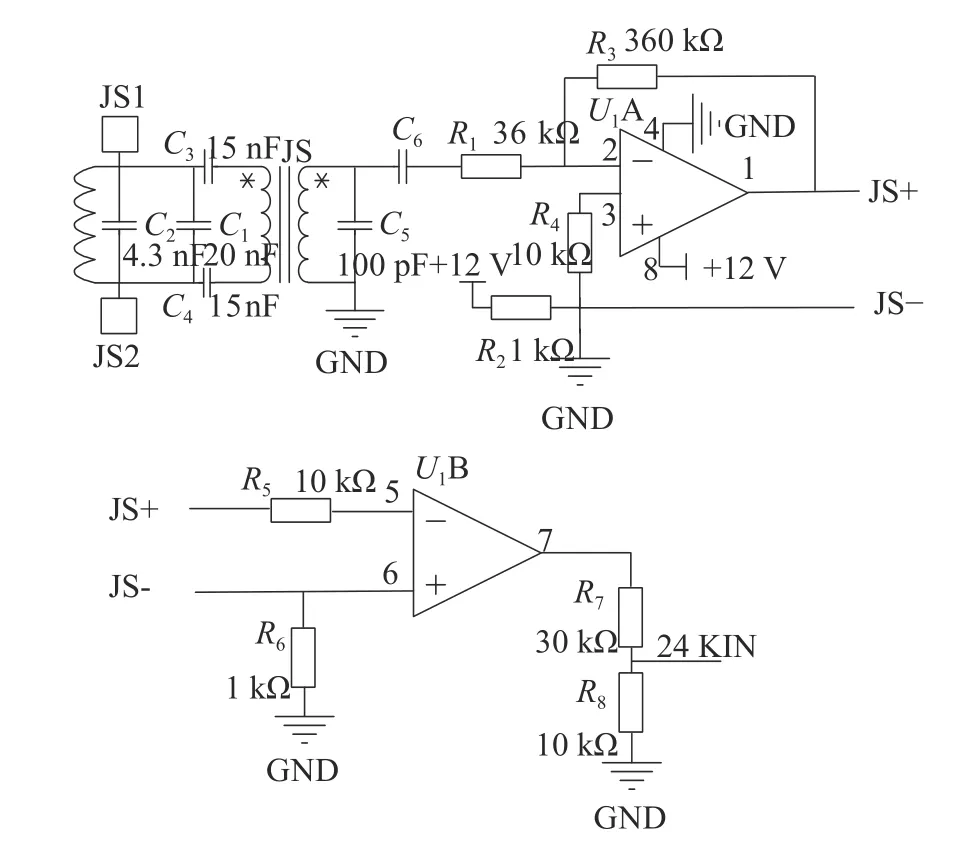

信号接收模块接收磁头接收线圈的信号进行处理,图10是信号接收模块电路图。

图10 信号接收模块电路

由图可知,信号接收模块接收来自磁头接收线圈的信号,然后经过变压器JS 耦合,最后经过U1(TL072MJG)进行放大。

信号磁头发送线圈和接收线圈通过电磁感应实现信号的传递,图11是磁头接收线圈收到信号的波形图。由图可知,磁头发送信号经过电磁感应耦合到接收线圈两端,信号波形依然保持正弦波状态,但是信号的幅度衰减较大,最大值由原来的48 V 衰减到了现在的30 mV 左右。

图11 磁头接收线圈信号波形

接收到的信号经过U1进行放大,放大后的波形经过电阻R7和R8进行分压,FPGA 输入端24KIN(图10中接收信号输入FPFA 的接口)的波形图如图12所示。由图可知,信号波形接近于方波,方波的高电平值为2.2 V,低电平值为0 V,将该信号输入到FPGA 中能够有效识别出信号波形。

图12 接收信号输入FPGA 端信号波形

2.3 模数转换模块

模数转换模块实现对外部电源模块,发送、接收模块的电压监测,模数转换模块使用芯片AD7265实现,图13是模数转换模块电路图。

图13 模数转换模块电路

由图可知,AD7265芯片引脚22(SGL/DIFF)连接高电平,输入配置为单端模式,共12路;引脚21(RANGE)决定了12路通道输入模拟量的范围,该引脚接高电平,输入模拟量的范围在0~2VREF(VREF为芯片内部参考电平),即为5 V;引脚2(REFSELECT)接低电平,参考电压为2.5 V;根据SGL/DIFF和引脚RANGE的配置可知,输出的12位二进制编码方式为二进制补码形式,该模式下1个最低有效位的大小为2VREF/4 096。AD7265共有3种工作模式,分别是正常模式、部分断电模式和完全断电模式,软件配置使该芯片一直工作在正常模式下。

由于受输入范围的限制,模拟值的输入范围是0~5 V。在12 V 电源监测时,使用阻值为47 kΩ和10 kΩ 的2个电阻分压,监测模拟量的理论值为2.105 V;24 V 电源经过10 kΩ和75 kΩ电阻分压,监测模拟量的理论值为2.824 V;3.3 V 电源经过10 kΩ和20 kΩ电阻分压,监测模拟量的理论值为2.2 V。220 V 电源经过一个整流电桥进行整形,然后通过电容进行滤波,最后再经过一个光电耦合原件,进行监测。线圈断线检测JSAIN量,是将外部传感器线圈上的电压值通过一个集成放大电路原件AD8226ARMZ进行放大后输入到AD7265中,如图14所示。

图14 耦合线圈断路监测电路

2.4 数据发送模块

数据发送模块将轴数信息和监测信息打包为帧发送出去,图15是数据发送模块电路图。

图15 数据发送模块电路

由图15可知,MCP2515[10-11]中引脚1(TXCAN)和引脚2(RXCAN)实现CAN 接口数据传输;引脚7(OSC2)和引脚8(OSC1)是时钟输入引脚,该芯片外接16 MHz 的外部时钟;引脚17(RESET)是低电平有效的器件复位输入引脚;引脚12(INT)是中断输出。

MCP2515每个发送缓存器占用内部14 byte 的资源,根据CAN 数据帧的格式可知,CAN 数据帧有标准数据帧和扩展数据帧,标准数据帧和扩展数据帧最大的区别在于标志位位数的不同,因此在存储数据时以扩展数据帧为依据。扩展数据帧共有29位标志位,因此需要4 byte 的存储空间存储,此外还需要1 byte 存储要发送数据的大小,最多可以发送8 byte 的数据,需要8个数据字节。最重要的是发送缓存控制寄存器TXBnCTRL,它控制着报文的发送[12]。

3 系统软件设计

图16是系统软件设计的整体框图,由图可知,要使系统可靠的工作,首先要保证系统信号产生和接收的完整性和正确性,它是轴数信号统计的前提;然后根据发送信号和接收信号进行轴数的统计,将统计好的轴数信息发送;最后监测是否发送完成,若轴数信息发送完成,将轴数信息清空,进行下一次计数。

图16 系统软件整体流程

软件设计的说明和硬件电路的设计相对应,从信号的产生、模数转换模块的实现、数据的产生和组合、数据发送4部分进行详细介绍。

3.1 信号的产生

系统中FPGA 外接16 MHz 的晶振,即系统时钟为16 MHz。使用计数器分频的方式产生要发送的24、28 kHz 的信号。对于24 kHz 信号使用计数器计数333个系统周期信号进行翻转,对于28 kHz 信号使用计数器计数286个系统周期信号进行翻转。

图17所示是24 kHz/28 kHz 信号仿真图,图中上面波形为28 kHz 波形时序图,下面波形为24 kHz 波形时序图。由图可知28 kHz 信号一个周期时间为35 750 000 ps,频率为27.972 kHz,频率偏差为0.1%;24 kHz 信号一个周期时间为41 625 000 ps,频率为24.024 kHz,频率偏差为0.1%,均在误差允许范围内。

图17 信号仿真波形

3.2 模数转换模块的实现

AD7265每14个时钟周期数据转换一次,时钟为1 MHz,故转换速率为14μs/次。当CS拉低时,模块的时钟开始计数,产生时钟adclk。片选计数器cnt_adcs使用时钟adclk 进行计数,计数到cnt_adcs=14结束,完成一次单端端口的模数转换。当cnt_adcs=1时,将上次转换完成的数据和相对应的门限值进行对比,检查所对应的模拟量是否出现异常。当cnt_adcs=2时开始芯片输出12位数据,直到cnt_adcs=13的时候将12 位数据全部输出。当cnt_adcs=14时,将片选CS拉高,同时将地址ad_addr 加1,准备对下一个数据进行采样,同时将cnt_adcs清零。

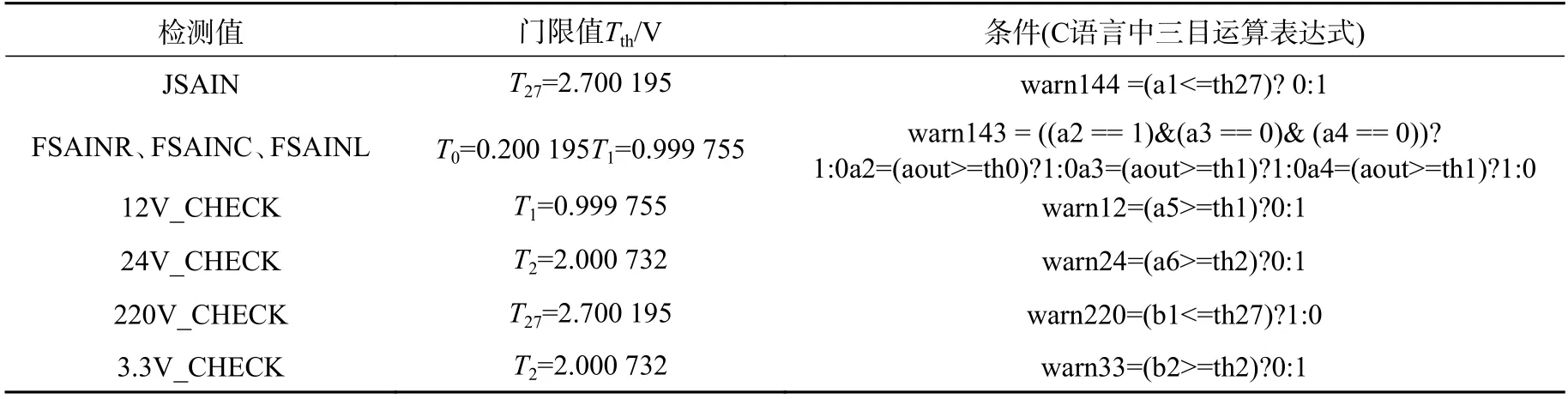

表1列出了各个监测量对应的门限值和其对应的判断条件,门限值对应的模拟量的计算方法是二进制编码原码数值与5/212相乘,再加上2.5。将实际采样值与门限值结果进行对比,比较后判断所检测的值是否超过所设定的门限值。这里规定若未超过门限值,上传数据为0;超过门限值出现异常时,上传的数据为1。根据上传数据对应的位即可检测哪里出现问题并及时进行维护。

表1 检测数值和检测判决条件

JSAIN在断线的情况下检测值为4.11 V,在连接状态下检测值为2.39 V。故在接收电路不断线的情况下,warn144为0。分别对FSAINR、FSAINL和FSAINC进行断线和不断线情况的测量。在断线情况下3个信号的测量值分别为0.684、0.111和0.691 V,与表1中对应相关门限值对比得a2=1、a3=0、a4=0,故warn143为1,表明在断线情况下会发出报警;在不断线的情况下,3个信号测量的测量值分别为0.496、3.846 和2.672 V,此时与表1 中对应相关门限值对比得a2=1、a3=1、a4=1,故warn143为0,表明在不断线的情况下不会报警。12V_CHECK 的实测值为1.929 V,故warn12为0;24 V_CHECK 的实测值为2.928 V,故warn24 为0;220 V_CHECK 的实测值为4.168 V,故warn220为0;3.3 V_CHECK 的实测值为2.650 V,故warn33为0。

3.3 数据的产生和组合

轴计数时根据发送信号经过调相后的信号sqrt_out 和接收信号sqrt_in 两者的相位差进行判别是否有列车车轮通过传感器磁头。规定在无车的情况下要保证两者的相位差在40°以内,有车时由于输入信号sqrt_in 相位的翻转,使两者的相位差相差较大(≥140°),在检测时设置门限值为70°,当超过70°时表示有车轮通过传感器。

由3.1节可知24 kHz 信号周期为41 625 000 ps,而系统时钟一个周期为62 500 ps,24 kHz 信号是通过对主时钟计数分频得到的,即对系统时钟计数666次就可以得到。同理28 kHz 信号周期为35 750 000 ps,需要对系统时钟计数572次。将24 kHz 或是28 kHz 信号的一个周期看作是360°,那么在对sqrt_out 和sqrt_in 两者的相位差进行计数时,相位差计数器检测到sqrt_and(sqrt_and<=sqrt_out&(!sqrt_in))的高电平时开始以系统时钟计数。对于24 kHz 信号,计数74个系统时钟周期表示40°,计数129个系统时钟周期表示70°;对于28 kHz 信号,计数63个系统时钟周期表示40°,计数111个系统时钟周期表示70°。

图18表示当有车轮经过传感器时相位标志信号的状态,使用phasea 表示24 kHz 信号处理板的相位标志信号,使用phaseb表示28 kHz 信号处理板的相位标志信号。图18(a)表示车轮先经过24 kHz 磁头,后经过28 kHz 时的相位信息。图18(b)图表示车轮先经过28 kHz 磁头后经过24 kHz 磁头时的相位信息。由两者低电平相位出现的先后进行计数,以24 kHz信号板为例,规定当检测到phasea 超前于phaseb时进行累计计数,当phaseb超前于phasea 时进行递减计数。

图18 不同方向行驶列车相位标志信号

数据使用CAN 总线扩展数据帧进行发送,扩展数据帧标志位一共29位,共占用MCP2515的4 byte;发送数据字节数占用MCP2515内部1个寄存器,发送一帧数据包含8 byte的数据,其中轴数占用2 byte,其他信息占用2 byte;保留2 byte;CRC_16效验码占2 byte。

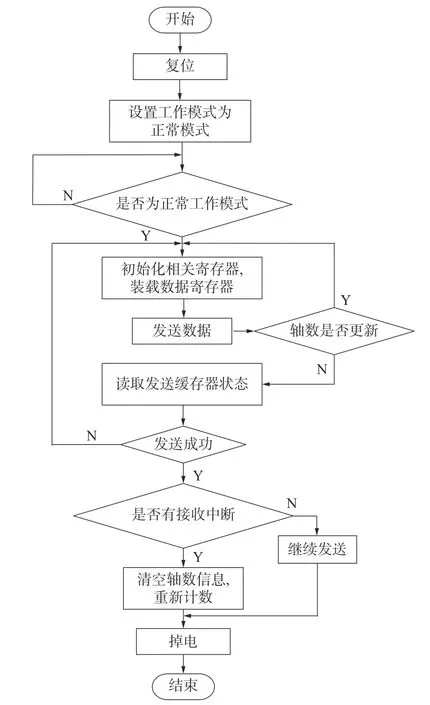

3.4 数据发送

数据的发送即通过MCP2515将组合好的数据进行发送,图19为发送数据流程图。由图可知:首先上电将MCP2515寄存器复位,设置工作模式为正常模式并检测,直到芯片工作在正常模式下;然后初始化相关发送和接收寄存器,将要发送的数据装载到发送寄存器中,启动发送,在发送时要时时监测轴数信息是否更新,若更新及时将更新的数据装载到发送缓存器中;最后判断接收缓存器是否接收到轴数不变的相关数据帧,若接收产生接收中断,将轴数信息清零,重新计数。

图19 数据发送流程

根据MCP2515的外部连接16 MHz 的晶振可知,FSOC=16 MHz,那么Tsoc=62.5 ns。由寄存器配置可知波特率预分频比RBRP为63,1位数据可分解为更小的时间份额TQ,TQ的计算表达式为TQ=2×(RBRP+1)×Tsoc=8 000 ns。CAN 数据帧每1位数据的时间长度NBT(标称位时间)由4部分组成,分别是同步段、传播段、相位缓冲段1和相位缓冲段2。其中同步段的时间长度固定为1TQ,不可编程改变,其他位段的长度可以通过编程设置。根据寄存器配置可知传播段时长、相位缓冲段1和相位缓冲段2的时长都为8TQ,故整个标称位时间为25TQ,MCP2515的CAN接口波特率为5 kb/s。

4 系统软件测试

将设计好的软件程序下载到系统硬件电路中,在有车和无车的状况下分别使用使用Altera公司的Quartus II软件提供的片上逻辑分析仪SignalTap对要分析的信号进行抓取,同时通过仿真来说明计轴原理。

4.1 无车时数据分析

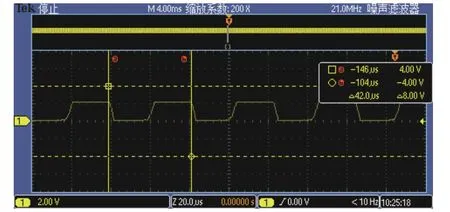

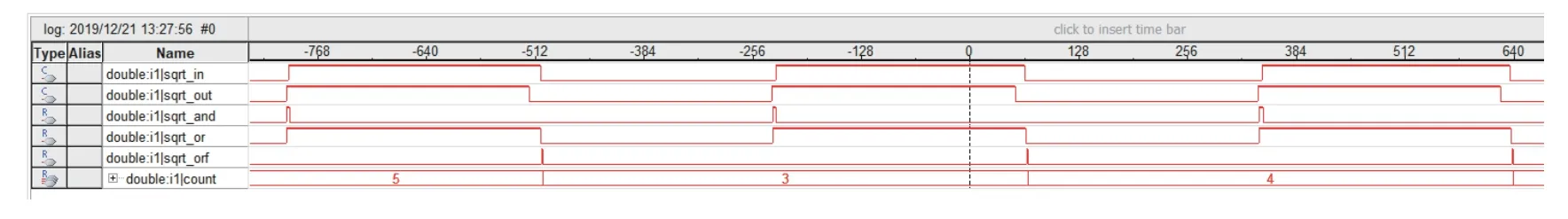

图20所示是无车状态下24 kHz 信号处理板,使用SignalTap抓取到关键信号的波形图。图中sqrt_in 表示磁头接收线圈接收的信号,sqrt_out 表示发送信号经过调相后的信号,sqrt_and 是sqrt_in和sqrt_out 相与得到的信号,sqrt_or 是sqrt_in 和sqrt_out 相 或 得 到 的 信 号,sqrt_orf 是sqrt_or 延时1 个周期后得到的信号和sqrt_or 相与得到的信号,count 表示相位差计数值。由图可知,无车状态下相位差计数值保持在3附近,与设定的40°的相位差的计数值73相比相差较大,说明在无车状态下相位差远远小于40°,符合设计要求。

图20 无车时SignalTap抓取信号波形

4.2 有车时数据分析

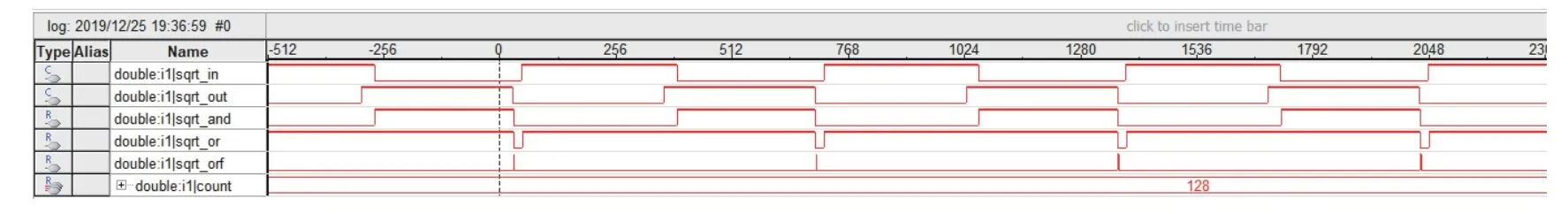

图21所示是有车状态下24 kHz 信号处理板,使用SignalTap抓取到的关键信号的波形图,图中信号的意义和图20中信号的意义完全一样。由图可知有车状态下相位差计数值为128保持不变,即相位差保持在70°以上,能够有效识别列车车轮信号。

图21 有车时SignalTap抓取信号波形

图22为软件计数原理波形图。由图可知,当有车轮通过传感器时,车轮先经过24 kHz磁头,后经过28 kHz 磁头,通过相位信息phasea 和phaseb来判别方向并计数。由于phasea 超前于phaseb,故进行累加计数。

由图还可以知道在进行数据时,轴数信息以3种不同的方式进行存储,zhouy <= zhou;zhouf = ~zhou;zhoub= ~zhou+16'd1。以3种方式存储轴数信息是为了在将轴数信息装载到发送寄存器中时进行对比,保证存储数据的准确性。

5 结论

图22 计轴原理波形

本文通过对计轴系统的硬件部分和软件部分的介绍,详细阐述了该系统所使用的硬件电路结构和系统的工作原理。与使用传统单片机和单核DSP芯片相比,使用FPGA 的优点如下:

1)本设计使用FPGA 软件编程设定阈值与使用硬件电路设计阈值相比较具有可更改、灵活和方便的优势;

2)本设计采用FPGA 作为信号处理芯片,信号处理速度快,更加适合于现如今高速铁路的发展,对高速铁路适应性更强,可监测。

3)本设计采用FPGA 作为信号处理芯片,在移相时可以软件编程,与现在的硬件相移相比较,采用软件相移设计更加精确具体。

4)本设计采用FPGA 作为信号处理芯片,与以往使用单片机做的系统相比,功能更加丰富,集成度更高,安全可靠性更好。