基于ZYNQ的行人检测系统的设计与实现

嵇达龙,张尤赛,王亚军

(江苏科技大学 电子信息学院,江苏 镇江 212003)

0 引 言

行人检测在自动驾驶、智能监控等领域得到了许多的应用[1]。但由于行人检测算法复杂度高、计算量大,现有的行人检测算法多数采用PC机来完成,其灵活性、便携性等限制了在户外场景及汽车等可移动设备中的应用。

常见的行人检测方法分为基于运动检测和基于特征学习的方法[2]。基于特征学习的行人检测方法,由于其检测效果较好,得到了广泛的关注。其中,基于HOG特征的AdaBoost算法是此类方法中的典型算法之一,该算法具有较高的检测率和鲁棒性[3,4]。

目前行人检测片上系统主要采用ARM、FPGA等单一平台的设计方案。ARM易于搭建操作系统,但是处理速度较慢;FPGA计算能力强,资源丰富,结构灵活,但是不易于搭建操作系统[5]。XILINX公司新提供了一种集成ARM和FPGA的ZYNQ-7000片上系统,芯片分为处理系统(processing system,PS)和可编程逻辑(programmable logic,PL)两部分。该系统弥补了上述单一平台的不足,充分结合了FPGA的并行特性以及ARM在操作系统上的优势[6,7]。

据此,本文提出了一种基于ZYNQ的行人检测系统的设计方案。为了提高HOG特征提取算法的效率,利用FPGA的并行特性,采用流水线结构替代传统串行结构,可以在一个时钟周期下同时完成多个步骤,从而大大提高算法的速度。在AdaBoost级联分类器算法的设计中,采用并行结构的设计方式将其保存在FPGA的BRAM中,通过查找表的方式在单个时钟周期内即可完成判断。此外,采用软硬件协同的设计方式,利用ARM编程的灵活性,由PS部分完成显示控制、图片读取等操作[8]。

1 行人检测相关算法

1.1 HOG特征

HOG是一种表征行人轮廓信息的特征描述子,采用局部方向梯度直方图来构建特征集。HOG算法的核心思想是采用滑动窗口的机制,将图像中的局部目标的形状描述为梯度方向的密度分布。

图1以80×60像素的图像为例给出了HOG特征提取原理。图1为80×60像素的图像。首先将其分割成无重叠的cell单元,每个cell单元的大小为8×8像素,然后分别计算每个像素的梯度。依据像素梯度的方向划分成8段,统计各cell单元的方向梯度直方图。最后将cell单元以 3×3 大小拼接为相互重叠的block块,组合在一起构成该图像的HOG特征。

图1 HOG特征提取原理

HOG特征提取过程可分为以下5步:

步骤1 计算RGB图像的亮度值L

(1)

其中,R、G、B分别表示3个颜色通道对应的值。L的取值范围为[0,255],可以用8bit无符号整型表示。

步骤2 根据亮度值,计算高度方向和宽度方向的梯度

Gh(h,w)=L(h+1,w)-L(h-1,w)

(2)

Gw(h,w)=L(h,w+1)-L(h,w-1)

(3)

其中,Gh(h,w)、Gw(h,w) 分别表示坐标 (h,w) 处对应高度方向和宽度方向的梯度,L(h,w) 表示坐标 (h,w) 处对应的亮度值。Gh(h,w)、Gw(h,w) 的范围为[-255,255],需要用9bit有符号的整型表示。

步骤3 计算像素点 (h,w) 的梯度幅值G(h,w) 和角度θ(h,w)

(4)

(5)

为了统计cell单元的梯度方向直方图,在本文中将梯度角度划分成8段,如图2所示。经计算易知,梯度幅值G(h,w) 需要9bit表示。

图2 梯度方向分段

步骤4 依据步骤3划分的区间,构建梯度方向直方图h,如式(6)、式(7)所示

h=(h0,h1,h2,h3,h4,h5,h6,h7)

(6)

(7)

其中,hk的最大值为2885,因此hk需要12bit表示,h需要8×12bit来表示。

步骤5 由于局部光照的变化,使得梯度强度的变化范围较大[9],因此将cell单元以3×3大小划分成一个block块,并对局部进行归一化处理,进一步提高检测效果。组合的block块的特征向量Hv为

Hv=(h(i,j),h(i,j+1),h(i,j+2),

h(i+1,j),h(i+1,j+1),h(i+1,j+2),

h(i+2,j),h(i+2,j+1),h(i+2,j+2))

(8)

其中,h(i,j) 表示第i行、第j列cell单元统计直方图的特征向量。

采用L1-norm对block块进行归一化,得到归一化后的统计直方图Hvnorm

(9)

1.2 AdaBoost级联分类器

AdaBoost是一种迭代算法,核心思想是通过对同一个训练集用多个弱分类器去学习,每个弱分类器只返回0和1两种结果,然后将这些弱分类器组合起来,构成一个强分类器。

假定训练样本集S包含Np正样本和Nn负样本 (N=Np+Nn),经过I次迭代得到K个弱分类器Cw={B,H},其中B={x,y} 表示block块坐标,H为对应坐标的HOG值。

AdaBoost级联分类器的具体训练过程如下:

步骤1 初始化样本权重

(10)

步骤2 针对正负样本,分别统计block块中各个cell单元HOG特征值的累加权重分布

(11)

(12)

其中,hcell和wcell分别表示block块坐标中cell单元的行和列索引,i表示当前迭代的次数。根据式(13)计算差值,取差值最大时对应的block块坐标B和HOG值H构成当前迭代输出的弱分类器Ck={B,H}

D=D正样本(B,H,hcell,wcell)-D负样本(B,H,hcell,wcell)

(13)

步骤3 根据上一步得到的block块坐标B以及对应的HOG值H,遍历所有样本更新权值,满足该条件的样本权重不变,提高其它样本的权重

(14)

将更新后的权重归一化

wi+1,n=w′i+1,n/Zi

(15)

(16)

其中,Zi为规范化因子。

步骤4 重复步骤2和步骤3过程I次,每次迭代产生一个弱分类器Cwi,最后剔除重复的弱分类器,构成一个强分类器Cs={Cw1,Cw2,…,Cwi}。

2 算法优化与实现

传统的HOG算法采用串行结构提取特征,算法执行效率较低,在硬件实现中难以满足实时性的要求,每个时钟周期只能处理一个任务。本文采用FPGA的三级流水线结构设计方式对HOG特征提取算法进行加速,实现了在一个时钟周期内,同时完成特征提取的梯度计算模块、cell单元统计直方图生成模块、block单元统计直方图生成模块的工作,大大提高算法的速度。为了进一步提高算法的效率,设计中针对硬件结构特性采用分段近似的方法简化算法的归一化过程,通过移位运算替代复杂的除法运算,不仅提高了归一化的速度,又可以降低硬件资源的消耗。基于软件实现的AdaBoost分类算法在检测过程中,需要串行遍历每一个弱分类器进行匹配判断,本文采用并行结构将弱分类保存在FPGA的BRAM中,采用查找表的方式替代遍历方式,只需要一个时钟周期就可以完成匹配判断工作。优化后的算法在保证检测率的同时,大大加速算法的执行速度。

本文算法在XILINX公司的ZYNQ-7000片上系统实现,该片上系统包含PL和PS两部分。算法的设计流程图如图3所示,图片读取模块和显示控制模块运算量小但流程控制复杂,适合在PS端实现;特征提取模块计算量大、级联分类器模块易于并行化,适合在PL端实现;最后将检测结果送至显示屏。其中PS端和PL端采用AXI总线完成数据通信。

图3 基于ZYNQ行人检测算法的设计流程

2.1 HOG算法硬件设计

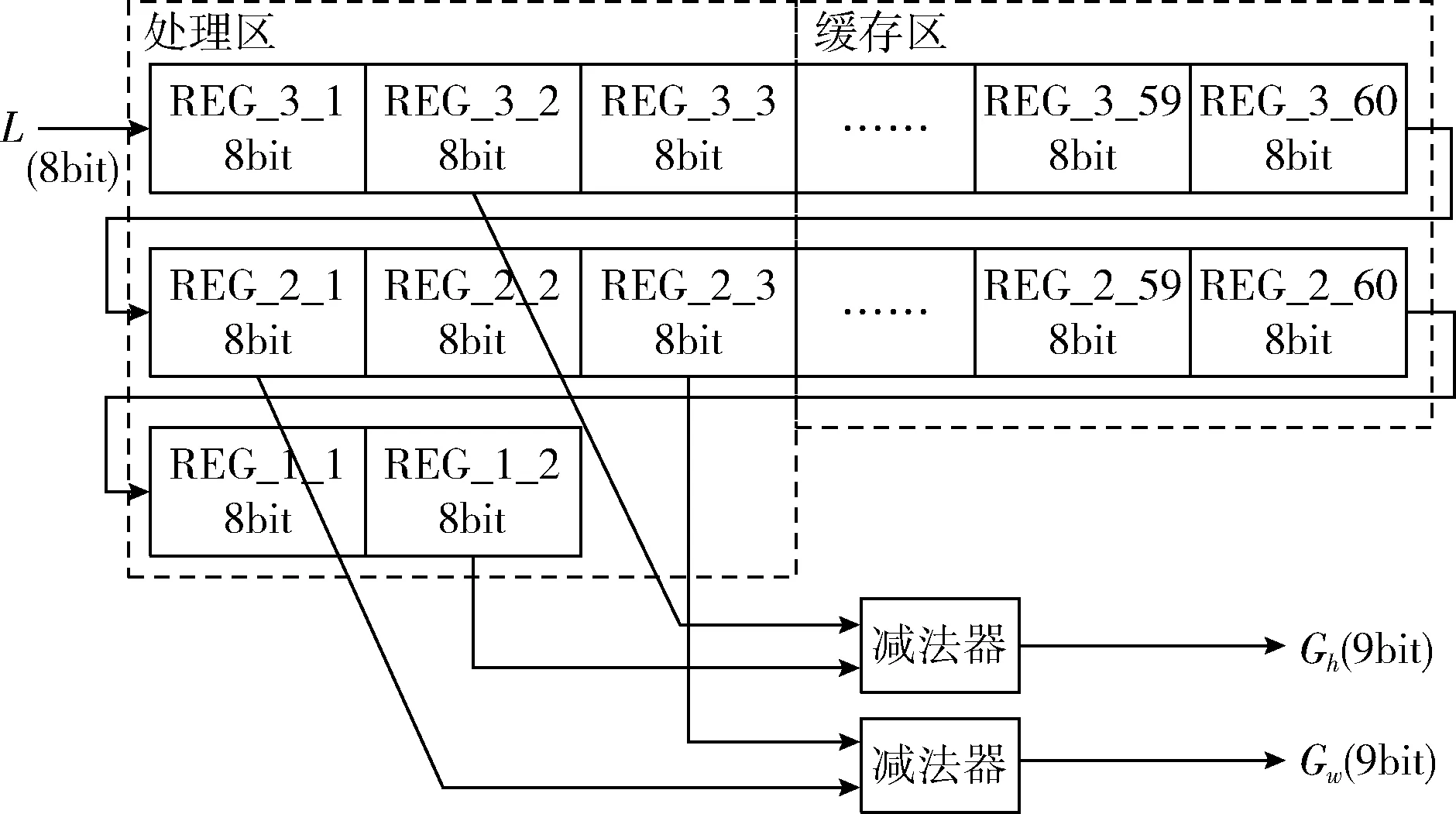

2.1.1 梯度计算

本文采用流水线结构设计梯度计算模块,该模块包含一个处理区和一个缓存区,如图4所示。处理区由8个8bit的移位寄存器构成,在时钟上升沿的驱动下,新到的8bit亮度值L移入寄存器REG_3_1,其它寄存器的值依次移入下一级寄存器单元。本文待检测图片像素为80×60,因此缓存区需要2组57(=60-3) 个8bit寄存器单元完成缓存。该方法保证计算梯度所需的亮度值始终处于处理区的REG_3_2、REG_1_2、REG_2_1和REG_2_3。采用流水线结构,不需要一次性缓存4800(=80×60) 个像素值,只需要设计122个8bit寄存器缓存即可,大大节约了硬件资源。

2.1.2 梯度幅值和角度

由于生成直方图时只需要确定对应的段号即可,而不需要知道具体的角度值,因此K Dohi等针对式(4)、式(5)提出了一种简化方法[10],将梯度方向表示为θn(h,w)

图4 梯度计算的流水线结构

(17)

其中,θn(h,w)∈{0,1,2,…,7}。 具体硬件电路实现如图5所示,该方法避免了复杂的tan-1运算,只需要4次乘法运算、4次比较运算和1次减法运算。

图5 梯度幅值和角度计算模块

由于Gh和Gw为9bit有符号数,使用ZYNQ-7000提供的DSP48E模块中的18×25的乘法器,完全满足式(4)中平方运算的精度要求。最后调用CORDIC IP核对平方和进行开方,得到梯度幅值。

2.1.3 生成cell统计直方图

由于每个像素点包含梯度幅值和梯度角度两个数据,为了方便设计,将9bit梯度幅值和3bit梯度角度拼接为一个12位的数据作为本模块的输入。同样采用流水线结构设计cell统计直方图电路模块,如图6所示。处理区中包含了5×5个寄存器单元,对应一个cell单元,生成的cell单元统计直方图h可用8×14bit表示。由于cell单元之间互相不重叠,因此与梯度计算模块不同,该模块不需要每个时钟周期都进行计算。

图6 cell统计直方图流水线结构

2.1.4 生成block统计直方图

图7 block统计直方图流水线结构

cell单元以3×3大小划分成block块,采用流水线结构进行设计,如图7所示。上一级生成的cell单元统计直方图h,依次流入下一级寄存器单元。文献[10]提出了一种分段法近似法,对归一化过程进行了简化。该方法的主要思想是将式(9)中的归一化分母近似为以2为底的指数幂和的形式,将除法运算转化成移位运算,在一定误差范围内,大大提高了算法的速度。为了节约硬件资源,将归一化后的直方图二值化,二值化后每个block统计直方图只需9×8bit即可表示。

2.2 AdaBoost级联分类器硬件设计

分类器的设计过程分为离线学习和硬件实现两个阶段。在设计中,分类器的离线学习过程在MATLAB上完成。每次学习过程,分别统计正负样本每个block块单元HOG特征值的累加权重分布,选出正负样本中HOG特征值的累积分布差值最大时对应的特征值H和块坐标B作为当前迭代输出的弱分类器。经过500次迭代训练,并剔除重复的弱分类器后,得到了61个弱分类器Cw={B,H}。 将所有的弱分类器级联构成一个强分类器Cs。 强分类器通过待检测图像与训练好的弱分类器匹配成功的统计个数来判断当前检测窗口是否存在行人,当统计值低于某阈值时判断为没有行人,高于该阈值则判断为有行人。为了确定该阈值,图8给出了本设计采用的NICTA行人库的ROC曲线图,该曲线描述了阈值从10到50之间的系统误检率和召回率之间的关系,越接近图表的左上方,系统的检测效果更好[10],选取24作为分类器的阈值,此时检测效果最好。

图8 NICTA行人库ROC曲线

分类器的设计模块如图9所示。系统上电后,PS端将待检测的图像数据通过AXI总线送至HOG特征提取电路。特征提取电路工作时,每一级流水线输出待检测图像当前block块的HOG特征值Hvbin,坐标生成电路输出当前的块坐标Bnorm,其中块坐标Bnorm的数据格式与弱分类器块坐标B的格式相同。根据当前电路输出的块坐标Bnorm,利用查找表的方式,一个时钟周期就可以找出固化在FPGA的BRAM中具有相同坐标Bwi所对应的弱分类器的HOG特征值Hwi,而在PC端实现的算法找出该特征值,则需要在消耗多个时钟周期下遍历所有弱分类器才能找出。将找到的弱分类器的HOG特征值Hwi与特征提取电路模块输出的HOG特征值Hvbin匹配判断,统计匹配成功的弱分类器的个数。统计结果通过AXI总线送回PS端,PS端根据统计结果和训练阶段得到的分类器的阈值关系,判断当前待检测图像是否存在行人,并输出相应的检测结果。

图9 分类器的设计

3 实验结果与分析

本实验硬件平台采用基于ZYNQ-7000的黑金ALINX7010开发板,其中ARM主频667MHz,FPGA主频250 MHz,开发环境使用VIVADO 2018.1和Xilinx SDK 2018.1,编程语言使用Verilog HDL和C;分类器的学习在MATLAB R2016a实现。

实验使用NICTA行人数据库[11],样本数据大小80×60,随机选取2000个正样本和2000个负样本构成训练样本集,另外选取3000个正样本和3000个负样本作为测试样本集。图10给出了正负样本的示例,第一行为正样本,第二行为负样本。

图10 正样本和负样本示例

在AdaBoost分类算法中,训练样本集经过500次迭代,得到了61个弱分类器。分类器的阈值为24。为了减低FPGA的资源消耗,在特征提取阶段,对Block块特征值进行二值化,二值化的阈值取0.03[10]。

实验中,采用召回率、精度、误检率作为评价行人检测系统检测性能的技术指标。设TP、TN、FP、FN分别表示正样本分类为正样本,负样本分类为负样本,负样本分类成正样本和正样本分类为负样本的样本数。则召回率TPR、精度P、误检率FPR可以分别表示为

(18)

(19)

(20)

召回率TPR、精度P和误检率FPR是衡量算法检测性能的重要技术指标,TPR和P越高,FPR越小,检测性能越好[4]。表1给出了本文算法在3种不同的实现方式下的各项性能指标的比较。

表1 不同实现方式下算法检测率的比较

从表1可以看出,基于MATLAB和基于ZYNQ平台ARM方式实现的检测系统,各项性能指标相同。而采用基于FPGA+ARM实现方式,由于在设计过程中为了简化计算,提高检测速度,采用了近似计算的方式,召回率、精度和误检率均有所降低,但与前两种实现方式相当,基本达到同等性能。

FPGA占用资源主要包括LUT、LUTRAM、FF、BRAM和DSP。表2给出了本文方法和基于PS实现方法在资源利用和时间消耗两个性能指标的对比。

表2 资源和时间消耗对比

从表2可以看出:

(1)PS实现方法中,特征提取算法和分类器的设计都是通过软件在ARM核中实现,所设计的系统主要硬件资源消耗在显示模块VDMA的IP核的实现上;

(2)本文采用的PS+PL方法,除了VDMA上的资源消耗,还有为了提高算法的速度,移植到FPGA上的特征提取模块和分类器模块所需的硬件资源消耗;

(3)本文算法占用的各项硬件资源相比要多于PS方法,但对于本设计中采用的ZYNQ-7000平台,能够完全满足所需的资源要求;

(4)本文方法的运算速度相对于PS方法提高了44倍以上,每秒可检测83张(80×60)以上,完全满足实时检测的要求。

4 结束语

本文针对户外场景下行人检测系统对实时性、便携性和低功耗等性能要求,提出了一种基于ZYNQ的行人检测算法。利用FPGA的特性,对HOG算法和AdaBoost分类器的结构设计和实现方法上进行优化,大大提高算法的效率;结合ARM部分(PS)完成显示和控制工作,提高了系统设计的灵活性。在保持同等检测性能的条件下,运算速度上得到了大幅提升,能够很好地满足实际需求。